高速コンバータのトレンドと使い道

まず、高速コンバータとはどのぐらい高速なのでしょうか?定義は難しいですが、一般的にはサンプリングレートが数十MHz~のコンバータを示しているように思います。これからも分かるように、過去においては数十MHzで「高速コンバータ」と言われていたんですね。ところが今では、十数GHzのサンプリングレートの高速コンバータが発売されています。実に3桁も増えているんです。半導体の進化と一緒に、高速コンバータはこのようにどんどんサンプリングレートを増やしています。

ここまで速くなったコンバータが使われるところというと、真っ先にあげられるのが無線機とレーダーシステムです(これに関連した計測関連もそうですね)。

簡単に言えばRF領域を直接デジタル化しちゃえ!ということになります。

この記事で無線機の詳細を議論することはしませんが、簡単にイメージがお伝えできればと思います。

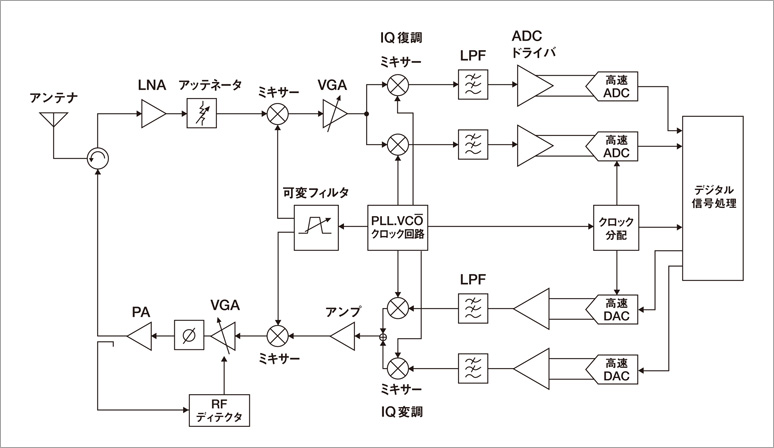

一般的には無線機は高周波の信号を扱うために周波数変換を行って処理されています。RF段をミキサーを使ってIF段、さらにミキサーでベースバンドまで落として処理をする、という流れかと思います。一般的なブロック図を下記に示します。

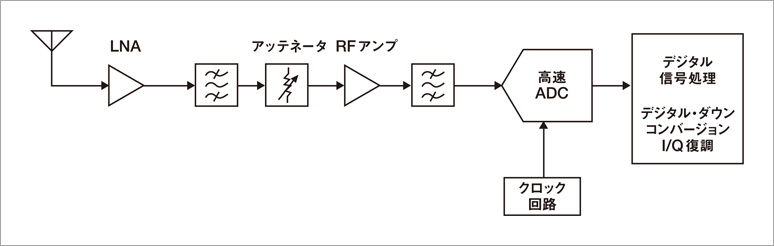

それが最近の高速コンバータを使うとこうなります。

非常にシンプルになりましたね。

(もちろんこれはこれで別の様々な課題があることは承知の上シンプル化して話を進めます)

メリットとしては大きくは以下の3つがあります。

- アナログ部品削減によるSNと歪の改善

- ハードの共通化(デジタル処理の変更で対応する)

(ソフトウェア無線(SDR-Software Defined Radio)の考え方) - Space saving

このように高速コンバータを使うことは多くのメリットを生み出しています。

次に高速コンバータのIC側の問題を考えてみます

高速コンバータのICのボトルネックとは?

少し過去にさかのぼります(高速コンバータが数百Msps程度の時期)。

サンプリングレートをあげていく過程で何がボトルネックになっていたかと言うと、一番大きなところは増大するデジタルデータをどうやって出力するのか?という問題でした。

(実際にコンバータの設計者と話をしたことがありますが、「コンバータのコアのサンプリングレートを上げることは今の半導体技術があれば難しくない」、とおっしゃっていたことを記憶しています)

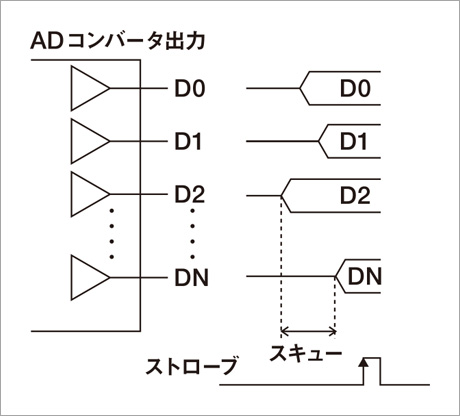

200MHz程度までのサンプリングレートでは、一般的なパラレルインターフェースで対応可能でした。しかしながら200MHzを超えてくるとパラレルインターフェースでは難しい局面が増えてきます。物理的なインターフェースの問題とタイミングスキューの問題ですね。

ディファレンシャルインターフェースのLVDSを使用することで延命しましたが、それでも800MHzぐらいまでです。もちろん信号線を増やすことで1本あたりの伝送速度を落として対応する方法もありますが、その場合はICのピン数や基板の配線領域が増えてしまい基板設計が大変となってしまいます。

そんなこんなで、いよいよ本格的なシリアルインターフェースの必要性が叫ばれるようになります。シリアルインターフェースは他の規格もそうですが、いろいろな手順が必要になってきます。それを各メーカーが勝手に作るわけにはいきませんので、多くのメーカーが集まり、JESD204が規格化されました。

(現在ではJESD204Bとなっていますので、これからの呼称はJESD204Bで統一します)

| function | JESD204 | JESD204A | JESD204B |

| 規格のリリース | 2001 | 2006 | 2011 |

| レーンの伝送速度 | 3.125Gbps | 3.125Gbps | 12.5Gbps |

| マルチ・レーン(コンバータ1台に複数レーン) | × | ○ | ○ |

| マルチ・デバイス(レーン1本に複数コンバータ) | ○ | ○ | ○ |

| レーン同期 | × | ○ | ○ |

| ディタミニスティック・レイテンシ | × | × | ○ |

JESD204Bは他のシリアルインターフェースの規格と共通の部分も多いのですが、やはりコンバータ向けの規格であるが故の特徴もあります。(上記表のディタミニスティック・レイテンシなんてまさにそうですね)

JESD204Bが規格化されたことでボトルネックが取り除かれ、高速コンバータの性能は飛躍的に向上することになります。そして最初の方ででてきたソフトウェア無線の概念などがでてきたわけです。10GHzを超えるサンプリングレートのコンバータってなんか隔世の感がありますよね。

JESD204Bは大量のデジタルデータを流せますので、コンバータの高速化のほかに多チャンネル化に対しても寄与することとなりました。大型の医療器では何百、何千ものアナログインプットが必要な機器が存在しております。そのような機器で個別にコンバータを配置していたら大変なことになりますので、たくさんの入力チャネルを備えたADコンバータが必須となります。そうなるとデジタルデータが大量に作られるのは必然であり、ここでもJESD204Bがブレークスルーとなり、ADコンバータの多チャンネル化を実現しています。

コンバータの盟主アナログ・デバイセズ社では何百チャネルのインプットを備えたADコンバータがあるんですよ。

JESD204Bの普及のために

I often hear people say that it's difficult to get started with JESD204B if you don't know anything about it. Analog Devices, Inc. is actively promoting the development of JESD204B-related products and enriching documentation in order to popularize JESD204B.

What is JESD204B (Analog Devices Official Site)

Macnica group is also planning a free seminar on Thursday, September 21st, which will include an actual connection demonstration, in order to lower the hurdles for JESD204B as much as possible for everyone. If you are interested, please join us. You can apply from the link below.

[Analog Devices x Intel® FPGA] JESD204B Open Seminar <Free>

(*すでに締め切られております)

ユーザー様にとってメリットの多い高速コンバータ、多チャンネルコンバータを採用するうえで、必須の知識となるJESD204Bへの入り口として活用いただければ幸いです。