Introduction

This article discusses the effectiveness of using in-pad vias and other additional printed circuit board (PCB) layout techniques to improve heat dissipation of current sensors with integrated conductors. An optimal heatsink is necessary to prevent the IC from exceeding its maximum junction temperature of 165°C.

BACKGROUND

Integrated Allegro current sensor package

Allegro's current sensor IC family is a fully integrated current sensing solution that leads the industry in power density. Current enters the package through integrated conductor leads (IP+, IP-), and the resistance of these conductors generates heat. This heat needs to be dissipated to keep the IC temperature below 165°C. In the absence of an active heatsink, the primary source of passive heatsink is heat dissipation to the PCB itself. The more metal directly connected to the integrated conductors, the more effective the heatsink becomes. The purpose of this article is to explain how to maximize passive heatsink to the PCB.

An overview of the integrated current sensor packages included in this article is provided in Table 1. Figures 1 and 3 show a comparison of die heating from 25°C with the sensed current applied to various Allegro current sensor packages. Figures 2 and 4 also show a comparison of die heating from 125°C with the applied sensed current.

Figure 1: In-pad vias — Allegro's lab results for high surface area packaging, 25°C. *Provided by Allegro MicroSystems.

Figure 2: In-pad vias — Allegro's lab results for high surface area packaging, 125°C. *Provided by Allegro MicroSystems.

Figure 3: In-pad vias — Allegro's lab results for low-surface-level packaging, 25°C. *Provided by Allegro MicroSystems.

Figure 4: In-pad vias — Allegro's lab results for high surface area packaging, 125°C. *Provided by Allegro MicroSystems.

Table 1: Overview of Allegro integrated current sensor package (provided by Allegro MicroSystems)

[1] Recommendations regarding PCB layout are provided in the appendix.

[2] Certification is currently being requested.

[3] RθJA represents the system-level thermal resistance when heat generated by the power consumed within the package is transferred from the circuitry (junctions) on the chip to the surrounding environment. RθJA is generally defined based on a two-layer PCB layout as defined in JESD51. However, for current sensors, the JEDEC standard board is not suitable because it cannot handle high currents. The RθJA defined in this document is based on the Allegro evaluation board optimized for high-current transmission mentioned in this article. RθJA is highly dependent on the PCB and the operating environment, but it is useful as an indicator for roughly evaluating the thermal performance of a package and for comparing packages.

[4] ΨJT is a thermal index for power consumption within a package, defined as the difference between the junction temperature and the highest temperature on the top of the package. This index is useful as a simple method for estimating the junction temperature by measuring the temperature on the top of the package. This value is highly dependent on the PCB and the operating environment. Technically it is not a "thermal resistance" and can take a negative value. This is because, unlike most IC packages, the main heat source (internal current loop) is not located at the same position as the die, and a negative value can occur when the temperature on the top of the package is higher than the junction temperature.

Advantages of In-Pad Vias

In-pad via technology places vias directly beneath the pads of surface mount components to connect the inner and outer layers. When using in-pad vias, the vias must be filled to prevent solder from being drawn into the holes and degrading the quality of the solder joint. The most common via fillers are non-conductive. Vias can also be filled with electrically and thermally conductive materials, but these tend to be more expensive than non-conductive materials and offer only a slight improvement over non-conductive fillers. Figures 5 and 6 show a comparison of LZ packages with and without vias beneath the copper pads.

Figure 5: Vias under the copper pad, using an LZ package as an example.

*Provided by Allegro MicroSystems

Figure 6: Example of an LZ package, showing the absence of vias under the copper pad.

*Provided by Allegro MicroSystems

In-pad vias are commonly used for thermal performance, space saving, and reduced electrical resistance.

- Thermal performance: As shown in Figure 5, by placing vias directly beneath integrated conductor leads, the PCB pads serve both as current conductors and heat dissipators. This method allows heat generated by components to dissipate more efficiently through the substrate to the inner metal layer, where it is more efficiently diffused away from the components.

- Space-saving: Placing vias directly beneath a pad is useful in some designs where space is limited, allowing components to be placed closer together. However, when vias are used for heat dissipation, additional components near the integrated conductor should be kept to a minimum to maximize the amount of uninterrupted metal plane for heat conduction.

- Reducing PCB trace resistance: Because vias connect multiple layers within the PCB directly in parallel, the resistance on the PCB from the current source to the integrated conductor leads can be minimized (see Figure 5). The resistance of the current-carrying layers around the IC generates heat within the PCB (see Figure 9), increasing the PCB temperature around the IC. This reduces the temperature gradient for heat to flow away from the IC, resulting in decreased heat dissipation efficiency.

Comparison of results between in-padded vias and non-in-padded vias.

Allegro MicroSystems provides evaluation boards with optimized heatsinks for rapid evaluation of Allegro current sensors in a lab environment (see Figure 9). The following comparisons collect data from these two evaluation boards. The boards are identical except that one has in-pad vias and the other has off-pad vias. (The two evaluation boards used to evaluate the LC/LZ package are shown in Figures 7 and 8. For all other packages, reference layout diagrams showing in-pad vias are included in the appendix. Note that these diagrams are not to scale.) Each via used in the in-pad vias is 0.5 mm in size. The via type is IPC-4761 Type VII: filled and capped vias. Non-conductive via filler is used. These boards are 6-layer, with each layer being 2 oz copper foil.

Figure 7: Reference diagram of LC/LZ PCB layout with in-pad vias

*Provided by Allegro MicroSystems

Figure 8: Reference diagram of LC/LZ PCB layout without in-pad vias.

*Provided by Allegro MicroSystems

The tests were conducted at ambient temperatures of 25°C and 125°C. Current was supplied to the PCB via a 2AWG gauge cable. Subsequently, DC current was passed through the integrated conductor leads of the device. The die temperature was measured using an on-chip temperature sensor after thermal equilibrium was reached. (This on-chip temperature sensor is not available to the customer.) The change in die temperature was determined by subtracting the measured ambient temperature from the measured die temperature.

For all packages, a comparison of thermal performance with and without in-pad vias can be seen in the plot below. Furthermore, a comparison of thermal performance at 25°C and 125°C can also be seen in the plot.

Note: Only evaluation boards with in-pad vias were used for testing at 125°C. As previously stated, the die temperature must not exceed 165°C, or an increase of 140°C from room temperature (140°C + 25°C = 165°C).

The data shows that using padded vias results in a smaller die temperature rise compared to not using padded vias. Allegro recommends using padded vias for all current sensors with integrated conductors.

For the most accurate results, Allegro recommends mounting components using a standard reflow process rather than hand soldering. Too much or too little solder can affect the results. This is especially true for QFN type packages (EZ and EX), where solder voids beneath the component are not visible and can significantly impact the heat sink on the PCB.

■ LZ Package

Figure 10: Comparison of LZ packages with and without in-pad vias

*Provided by Allegro MicroSystems

Figure 11: Comparison of LZ packages with in-pad vias (ambient temperature 25°C / 125°C)

*Provided by Allegro MicroSystems

■ LC Package

Figure 12: Comparison of LC packages with and without in-pad vias

*Provided by Allegro MicroSystems

Figure 13: Comparison of LC packages with and without padded vias (ambient temperature 25°C / 125°C)

*Provided by Allegro MicroSystems

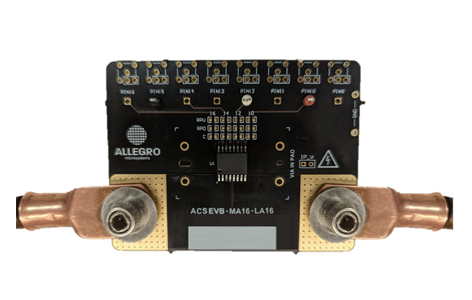

■ MA Package

Figure 14: Comparison of MA packages with and without in-pad vias

*Provided by Allegro MicroSystems

Figure 15: Comparison of MA packages with in-pad vias (ambient temperature 25°C / 125°C)

*Provided by Allegro MicroSystems

■ LA Package

Figure 16: Comparison of LA packages with and without InPad Via

*Provided by Allegro MicroSystems

Figure 17: Comparison of LA packages with in-pad vias (ambient temperature 25°C / 125°C)

*Provided by Allegro MicroSystems

■ MC Package

Figure 18: Comparison of MC packages with and without in-pad vias

*Provided by Allegro MicroSystems

Figure 19: Comparison of MC packages with in-pad vias (ambient temperature 25°C / 125°C)

*Provided by Allegro MicroSystems

■ EZ Package

Figure 20: Comparison of EZ packages with and without InPadVia

*Provided by Allegro MicroSystems

Figure 21: Comparison of EZ packages with in-pad vias (ambient temperature 25°C / 125°C)

*Provided by Allegro MicroSystems

■ EX Package

Figure 22: Comparison of EX packages with and without in-pad vias

*Provided by Allegro MicroSystems

Figure 23: Comparison of EX packages with in-pad vias (ambient temperature 25°C / 125°C)

*Provided by Allegro MicroSystems

■ LH Package

Figure 24: Comparison of LH packages with and without in-pad vias

*Provided by Allegro MicroSystems

Figure 25: Comparison of LH packages with in-pad vias (ambient temperature 25°C / 125°C)

*Provided by Allegro MicroSystems

■ MY / MZ Package

Figure 26: Comparison of MY/MZ packages with padded vias (ambient temperature 25°C / 125°C)

*Provided by Allegro MicroSystems

The effect of the temperature coefficient of copper.

The internal conductor is a copper alloy composed primarily of copper and small amounts of other metals, and its thermal behavior can be considered similar to that of pure copper. Copper has a positive temperature coefficient of resistance (+0.393% per 1°C), which means that its resistance increases as the temperature of the conductor rises. This is equivalent to an almost 40% increase in power consumed by the package if the ambient temperature rises by 100°C with no current flowing.

For example, if a current of 50Arms is passed through an MA package, and it has a resistance of 0.85mΩ at an ambient temperature of 25°C, it will generate 2.125W of power within the package. At an ambient temperature of 125°C, the generated power increases to 2.95W. This does not account for the temperature rise due to the power dissipated by the conductor when the current flows. This positive feedback provides further reason to efficiently remove heat from the package to reduce the possibility of thermal runaway.

Additional Board Layout Considerations

There are additional important considerations to take into account when designing these evaluation boards.

- Pad Layout: For optimal thermal performance, it is recommended that the top copper layer completely overlaps the primary current pads, leaving only a small gap between the internal conductor pins of IP+ and IP-. The size and number of vias in the overlapping area should be maximized based on the design rules of the PCB manufacturing process.

- Thermal Management: Maintaining junction temperatures below 165°C may require additional passive heatsinks or active cooling techniques at the system level. In isolated applications, adding a heatsink to the top of the package is not recommended as it may compromise the package's creepage distance (unless proper high-voltage isolation methods are followed). Adding insulation between the package and the heatsink generally reduces the heatsink's effectiveness, as most dielectric insulating materials are also good thermal insulators. Passive heatsinks passing over the top of the package are problematic, and heat dissipation via the PCB is the preferred method.

- Component Placement: If other components that generate a lot of heat are located near the current sensor, the temperature gradient for heat to flow out of the current sensor may be reduced. The best design practice is to place heat-generating components as far away as possible.

- Copper layer: A thick copper layer offers two advantages: improved heat conduction from the component and lower electrical resistance that generates heat. Maximizing the thickness of each layer and the number of layers that are in direct contact with the current sensor via the padded via minimizes the die junction temperature.

- Trace width: High-current traces require sufficient width to minimize voltage drop and inductance and prevent excessive heat generation. It is recommended to use the maximum practical PCB trace and board area around the current sensor.

- Solder Stencil: Solder voids on the large current conductor pads (IP+ to IP-) of QFN EZ packages increase the resistance of the solder joint and reduce heat sink to the PCB. Solder joint voids should be minimized. Voids can be caused by the release of gases from the solder flux. Voids can be minimized by providing a path for gases to escape from under the solder during solder reflow. Adding a grid to the solder stencil creates a path for gases to escape from under the package during the reflow solder wetting process.

CONCLUSION

Placing vias beneath the copper pads of Allegro current sensors minimizes current path resistance compared to placing vias outside the pads, improving heat sinking to the PCB and resulting in optimal thermal performance. Additional standard layout techniques can be implemented to further minimize die heating during operation of the integrated conductor current sensor.

Appendix

■ PCB Layout References

Figure 27: EX PCB Layout Reference Diagram

*Provided by Allegro MicroSystems

Figure 28: LC PCB Layout Reference Diagram

*Provided by Allegro MicroSystems

Figure 29: MA/LA PCB Layout Reference Diagram

*Provided by Allegro MicroSystems

Figure 30: MY/MZ PCB Layout Reference Diagram

*Provided by Allegro MicroSystems

Figure 31: MC PCB Layout Reference Diagram

*Provided by Allegro MicroSystems

Figure 32: LZ PCB Layout Reference Diagram

*Provided by Allegro MicroSystems

Figure 33: EZ PCB Layout Reference Diagram

*Provided by Allegro MicroSystems

■ Top Layer Showing Layout References of In-Pad Vias

Figure 34: EX PCB Layout Reference Diagram

*Provided by Allegro MicroSystems

Figure 35: LC PCB top layer

*Provided by Allegro MicroSystems

Figure 36: MA/LA PCB Top Layer

*Provided by Allegro MicroSystems

Figure 37: MC PCB Top Layer

*Provided by Allegro MicroSystems

Figure 38: EZ PCB top layer

*Provided by Allegro MicroSystems

Figure 39: LH PCB uppermost layer

*Provided by Allegro MicroSystems

Figure 40: MZ / MY PCB Layout Reference Diagram

*Provided by Allegro MicroSystems

Revision History

| number | date | content | Person in charge |

| - | August 28, 2023 | First edition release | K. Hampton |

| 1 | October 2, 2023 | Added thermal properties to Table 1 (page 2). Added footnotes to Table 1 (page 2). Corrected wire gauge size (page 3). Minor editorial updates (all pages). | K. Hampton |

| 2 | January 24, 2024 | Added application information for 125°C (2 pages), minor editorial updates (all pages). | K. Hampton |

| 3 | February 13, 2024 | Corrected the temperature in the caption of Figure 1 (page 1). | K. Hampton |

| 4 | September 23, 2024 | Added the LH package (all pages). Made minor editorial changes throughout, including the removal of the future tense (will) and standardization of terminology (unifying vias-in-pad to in-pad vias). | K. Hampton |

| 5 | January 9, 2025 | Added MY and MZ packages (all pages). Updated Figures 1 and 2 (pages 1 and 2). Updated rounding calculations for thermal resistance metrics (page 4). Removed related documentation and application support pages (page 13). | K. Hampton |

Copyright and Disclaimer

Copyright 2025, Allegro MicroSystems.

The information contained in this document does not constitute any representation, warranty, assurance, or solicitation from Allegro to you regarding the subject matter of this document. The information provided does not guarantee that the processes based on this information are reliable, or that Allegro has investigated all possible failure modes. It is your responsibility to conduct sufficient certification testing to ensure that the final product is reliable and meets all design requirements.

Copies of this document will be considered uncontrolled documents.

Inquiry

If you have any questions regarding this article, please contact us below.

Go to Allegro MicroSystems manufacturer information top page

If you would like to return to the Allegro MicroSystems manufacturer information top page, please click below.