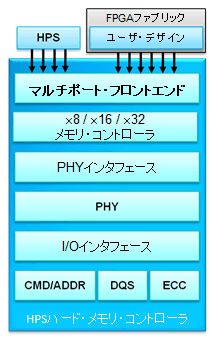

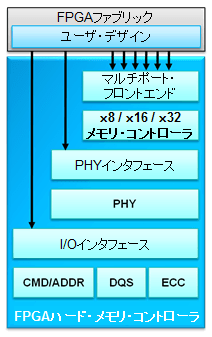

SoC FPGA にはメモリ・コントローラがハードで搭載されています。

このメモリ・コントローラは、ECC (誤り訂正コード)をサポートしており、HPS (ハード・プロセッサ・システム)と FPGA 側の両方に搭載しています。

ソフト・エラー発生率の増加を受けて、多くの設計者が外部 DDR メモリへの誤り訂正コード (ECC) の追加を検討し始めています。

ECC を使用すれば、シングル・ビット・エラーを訂正し、システム障害の可能性を大幅に低減することが可能です。

インテル®の SoC FPGA は、ECC をサポートするのに最適なデバイスです。

必要なロジック機能をすべて統合しているため、DDR メモリの幅を拡張するだけで外部メモリの ECC を実現できます。

HPS マルチポート・メモリ・コントローラの特長

|

|

|

FPGA マルチポート・メモリ・コントローラの特長

|

|

|