## リファレンス・マニュアル

---

Mpression Beryll Board

Revision 1.0

2014/2

# 目次

|                                       |    |

|---------------------------------------|----|

| 1. 安全使用上の注意                           | 3  |

| 1.1 シンボルの説明                           | 3  |

| 1.2 注意事項                              | 3  |

| 1.3 製造者情報                             | 5  |

| 2. 重要事項                               | 6  |

| 3. 使用前にご確認ください                        | 8  |

| 4. Beryll ボードおよびハードウェア概要              | 9  |

| 4.1 概要                                | 9  |

| 4.2 製品仕様                              | 9  |

| 4.3 ブロックダイヤグラム                        | 10 |

| 4.4 ボード仕様                             | 10 |

| 5. Beryll 搭載デバイス                      | 14 |

| 5.1 Cyclone V GX FPGA                 | 14 |

| 5.2 FPGA およびコンフィギュレーション ROM へのプログラミング | 14 |

| 5.3 コンフィギュレーション ROM へのプログラミング         | 16 |

| 5.4 コネクタピンアサイン                        | 19 |

| 5.5 シリアル・ポート                          | 22 |

| 5.6 DDR3 SDRAM                        | 22 |

| 5.7 FLASH / SRAM                      | 24 |

| 5.8 USB 2.0                           | 25 |

| 5.9 10 / 100 イーサネット                   | 26 |

| 5.10 24 ビットオーディオ・コーデック                | 27 |

| 5.11 ユーザーインターフェース                     | 28 |

| 5.12 クロック回路                           | 29 |

| 5.13 電源ツリー                            | 31 |

| 6. 使用上の注意点                            | 32 |

| 7. 改定履歴                               | 33 |

# 1. 安全上の注意

ここに示した注意事項は、お使いになる人や、他の人への危害、財産への損害を未然に防ぐための内容を記載していますので、必ずお守りください。

## 1.1 凡例

|           |                                                            |

|-----------|------------------------------------------------------------|

| <b>危険</b> | この表示は、取り扱いを誤った場合、「死亡または重傷を負う危険が切迫して生じることが想定される」内容です。       |

| <b>警告</b> | この表示は、取り扱いを誤った場合、「死亡または重傷を負う可能性が想定される」内容です。                |

| <b>注意</b> | この表示は、取り扱いを誤った場合、「傷害を負う可能性が想定される場合および物的損害のみの発生が想定される」内容です。 |

## 1.2 注意事項

|           |                                                                                                           |

|-----------|-----------------------------------------------------------------------------------------------------------|

| <b>警告</b> | 本マニュアルで指定された仕様に基づく AC アダプタ (梱包品) を使用してください。指定の仕様を満たさない AC アダプタを使用した場合は、キットの発熱、破裂、発火の原因となります。              |

|           | 強い衝撃を与えた後、投げつけたりしないでください。<br>発熱、破裂、発火や機器の故障、火災の原因となります。                                                   |

|           | 電子レンジなどの加熱調理機器や高圧容器に、本体や AC アダプタを入れないでください。本体や AC アダプタの発熱、破裂、発火、発煙、部品の破壊、変更などの原因となります。                    |

|           | 使用中の本体を布など熱のこもりやすいもので包んだりしないでください。<br>熱がこもり、発火、故障の原因となることがあります。                                           |

|           | 本体を廃棄する時は、他の一般ゴミと一緒に捨てないで下さい。<br>火中に投じると破裂する恐れがあります。廃棄方法については、廃棄物に関する各種法律・法令・条例等に従ってください。                 |

|           | 極端な高温、低温、また温度変化の激しい場所で使用しないで下さい。<br>故障の原因となります。周囲温度は 5°C ~ 35°C、湿度は 0% ~ 85% の範囲でご使用ください。                 |

|           | 電源コードを強く引っ張ったり、重いものを乗せたりしないでください。<br>電源コードを傷つけたり、破損したり、束ねたり、加工したりしないでください。<br>傷ついた部分から漏電して、火災・感電の原因になります。 |

|           | 濡れた手で電源プラグを抜き差ししないでください。<br>感電による怪我や故障の原因になります。                                                           |

|           | 電源プラグはコンセントの奥までしっかりと差し込んでください。<br>しっかりと差し込まないと、感電や発電による火災の原因となります。                                        |

|           | タコ配線を行ったり、AC アダプタの規格電圧以外の電源に接続したりしないでください。<br>故障や感電、発熱による火災の原因になります。                                      |

|                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  <b>警告</b><br><small>(前項から継続)</small> | <p>電源プラグのほこりを定期的に拭き取り、コンセント周辺のたまたたほこりを取り除いてください。</p> <p>ほこりがたまたままで使用していると湿気などで、絶縁不良となり、火災の原因になります。</p> <p>電源プラグやコンセプト周辺のほこりは、乾いた布で拭き取ってください。</p> <p>当ボードにコップや花瓶など、水や液体が入った容器を置かないでください。</p> <p>当ボードに水や液体が入ると、故障や感電の原因になります。水などをこぼした場合は、使用を中止し、電源を切って電源プラグを抜いてください。修理や技術的な相談はアルティマへお問い合わせください。</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|  <b>注意</b>                          | <p>ぐらついた台の上や傾いた場所等、不安定な場所には置かないでください。</p> <p>落下して、けがや故障の原因になります。</p> <p>直射日光の強い場所や炎天下の車内など高温の場所で使用、放置しないでください。</p> <p>発熱、破損、発火、暴走、変形、故障の原因になります。また、機器の一部が熱くなり、火傷の原因となる場合もあります。</p> <p>本体を組み込んだ装置の保守中は、電源を抜いて作業してください。</p> <p>感電の危険性があります。</p> <p>ボードに無理な力がかかるような場所に置かないでください。</p> <p>基板の変形により、基板の破損、部品の脱落、故障の原因となります。</p> <p>拡張ボードや他の周辺機器と一緒に使いの場合には、それぞれ個別の取り扱い説明書をよく読んで適正にお使いください。</p> <p>本マニュアルに記載されているもの、また別途動作を確認できていることを公表しているものの他は、特定の拡張ボードや周辺機器の相互動作は保証いたしかねます。</p> <p>当ボードを移動・接続するときは、電源スイッチを切ってください。</p> <p>電源をいれたまま移動・接続すると、故障や感電の原因になります。</p> <p>ベンジンやシンナーなど化学薬品を含んだ雑巾で手入れしないでください。</p> <p>当ボードが変質する可能性があります。科学雑巾を使用するときは、その注意書きに従ってください。</p> <p>当ボードを箱から取り出した際、機器本体に結露が発生した場合は、すぐに電源を入れないでください。</p> <p>当ボードを箱から取り出す際、冷えたボード本体が部屋の暖かい空気により結露が発生することがあります。</p> <p>結露があるまま電源を入れると、当ボードが破損したり、部品の寿命が短くなる場合があります。</p> <p>当ボードを取り出したら室温になじませてください。結露が発生した場合は、水滴が蒸発してから設置や接続を行ってください。</p> <p>カスタマイズ可能と明示している部分以外の分解、解体、改変、改造、再生はしないでください。</p> <p>本キットはカスタマイズが可能なキットですが、本マニュアルに指定された部分以外は基本動作に必要な部分に何らか外部の手が加わることで製品全体の動作保証が出来なくなります。本マニュアルに記載されているカスタマイズ可能部分以外のカスタマイズをご希望の場合には、はじめに必ずアルティマにご相談ください。</p> |

## 1.3 開発元情報

株式会社アルティマ

技術統括部

ソリューション 1 部

〒222-8563 横浜市港北区新横浜 1-5-5

詳しくは、Web サイトをご覧ください。

## 1.4 問い合わせ情報

ご購入頂いた販売代理店、もしくは下記 Web のお問い合わせフォームよりお問い合わせ下さい。

<http://www.m-pression.com/ja/contact>

## 2. 重要事項

### 最初にお読みください:

- 当製品のご使用前に必ず当リファレンス・マニュアルをお読みください

- 当リファレンス・マニュアルは、お手元にお持ちください

- ボードの構成を十分にご理解頂いた上でボードをご使用ください

### 当製品の用途 :

- 当製品は、アルテラ社のCyclone® V GX FPGA を使用するシステムの検証用ボードとしての使用を想定しております。当ボードをご使用頂く事で、ソフトウェア、ハードウェアの検証を行って頂く事が可能です。

### 当製品をご使用されるお客様 :

- 当製品は、ユーザーマニュアルおよびGetting Started を精読し、開発ボード及びFPGA の取扱いに熟知された方の使用を想定しております。当製品を使用するには、FPGA、ロジック回路、および電子回路への基本的な知識を必要といたします。

### 当製品を使用頂く際の注意事項 :

- 当製品は、お客様のプログラム開発および評価段階で使用するための評価用ボードとなります。

お客様の設計されたプログラムの量産時においては、当ボードをお客様の装置に組込んで使用することはできません。また、開発済の回路については、必ず統合試験、評価、または実験などにより実使用の可否をご確認ください。

- 当製品の使用から生ずる一切の結果について、株式会社マクニカ(以降マクニカ)は責任を持ちません。

- マクニカは、潜在的に内包されるすべての危険性を評価予期しているわけではありません。したがって当ボードやリファレンス・マニュアル内の警告や注意は、すべての警告や注意を含んでいるわけではありません。

それゆえ、当製品をご使用の際は、ユーザー様ご自身で製品を安全にご利用頂く必要があります。

- すべてのUSB メモリやSD カード、および消耗品は保証外となります。

- LAN インタフェース接続用機器の接続コネクションについては、保証外となります。

- 製品の改造又は、お客様による製品の損傷時は、交換対応ができません。

- 当製品は、鉛フリー製品を使用した製品です。

- 当マニュアルに記載のあるいずれのベンダの商標および登録済み商標の権利は、各ベンダに帰属します。

### 製品改善のポリシー :

- マクニカは、製品のデザイン、パフォーマンスおよび安全性に関して製品を常に改善し続けます。

マクニカは、お客様に予告なく、いつでも製品のドキュメント、リファレンス・マニュアル、デザインおよび一部およびすべての仕様を変更する権利を保有します。

### 製品の RMA について :

- 製品の納品後、30日以内の初期不良に関しましては無償交換にて対応させて頂きます

但し、以下の場合は無償交換の対応ができませんのでご了承ください。

- (1) 製品の誤使用または、通常使用環境ではない状況での製品の損傷

- (2) 製品の改造または補修

- (3) 火災、地震、製品の落下やその他アクシデントによる損傷

**図および写真 :**

- ・ 図や写真は、お手元にある実際の製品とは異なる可能性がございます。

### 3. 使用前にご確認ください

梱包の開封時点でそれぞれ同梱されているか、破損など無いかを確認してください。

梱包物が足りない場合や、外見上認識できる破損を発見した場合には、お届けより30日以内に弊社の担当営業までご連絡ください。

|                                |                                          |

|--------------------------------|------------------------------------------|

| Customer letter                |                                          |

| Beryll ボード                     |                                          |

| USB スタンダード A to Mini-B プラグケーブル |                                          |

| AC アダプタ (出力 12V)               |                                          |

| リファレンス・マニュアル                   | これらのファイルは、レターに記載されているURL よりダウンロードしてください。 |

| Beryll ボード回路図                  |                                          |

| FPGA サンプルデザイン                  |                                          |

# 4. Beryll ボードおよびハードウェア概要

## 4.1 概要

当ボードは、アルテラ 社のローコストFPGA であるCyclone V GX FPGA を使用したFPGA 開発ボードです。当開発ボードは以下の特徴があります。

- A. Cyclone V GX FPGA を使用し、柔軟にユーザ・ロジックの開発・検証が可能。

- B. アルテラ社の ドータ・カード・コネクタ (以下、HSMC という) を搭載し、システム拡張が可能

- C. On-Board USB-Blaster™ 回路を搭載しており、USB ケーブルを接続することで FPGA のコンフィギュレーション回路をダウンロード可能

- D. Cyclone V FPGA より新規搭載された HMC (ハード・メモリ・コントローラ) をマイクロン社の DDR3 メモリと共に評価可能

## 4.2 製品仕様

表 1 に 当ボードの製品仕様を示します。

表 1 Beryll ボード製品仕様

| 機能                            | 部品 又は 仕様                                                                                                         |

|-------------------------------|------------------------------------------------------------------------------------------------------------------|

| FPGA                          | 5CGXFC4C6F27C                                                                                                    |

| Power Supply                  | DC 12 V 3.8 A                                                                                                    |

| Dimensions                    | 140.00 mm x 155.00 mm                                                                                            |

| HSMC                          | ASP-122953-01                                                                                                    |

| Printed Circuit Board         | FR4 10-layer                                                                                                     |

| Configuration ROM             | EPICS128S16N                                                                                                     |

| SRAM                          | IDT71V416S10PHG8 (512 KByte)                                                                                     |

| DDR-SDRAM                     | DDR3-800 256 MBytes (128 MByte x 2) MT41J64MJT                                                                   |

| Flash ROM                     | JS28F256M29EWLA (32 MByte)                                                                                       |

| USB 2.0 (Mini-B)              | CY7C68013A-56LTXC                                                                                                |

| Audio                         | UDA1345TS                                                                                                        |

| Ethernet                      | DP83865DVH                                                                                                       |

| Clock (for FPGA)              | 27 MHz x 1, 33 MHz x 1, 50 MHz x 1, 125 MHz x 1                                                                  |

| JTAG Connector                | DIP 10-pin Header, 2.54-mm pitch x 1                                                                             |

| Status LED                    | 12 pcs<br>(12V_POWER, HSMC PSNTn, nSTATUS, nCONFIG, CONF_DONE, INIT_DONE, Blaster, ACT,LK10,LK100,LK1000,DUPLEX) |

| FPGA Reconfiguration Push SW  | 1 (SYS_RESET)                                                                                                    |

| General-purpose LED           | 8                                                                                                                |

| General-purpose Push SW       | 4                                                                                                                |

| General-purpose Dip SW        | 1 (SW0-SW3)                                                                                                      |

| General-purpose 7 Segment LED | 2                                                                                                                |

| Character LCD Connector       | 1 (3.3-V) * A character LCD is optional.                                                                         |

| Power SW                      | 1                                                                                                                |

| RS-232C                       | DB9 Female Connector                                                                                             |

(注) 当ボードには、キャラクタ LCD のコネクタが付属していますが、LCD ディスプレイは付属しておりません。LCD はお客様にてご用意頂けます様お願いします。

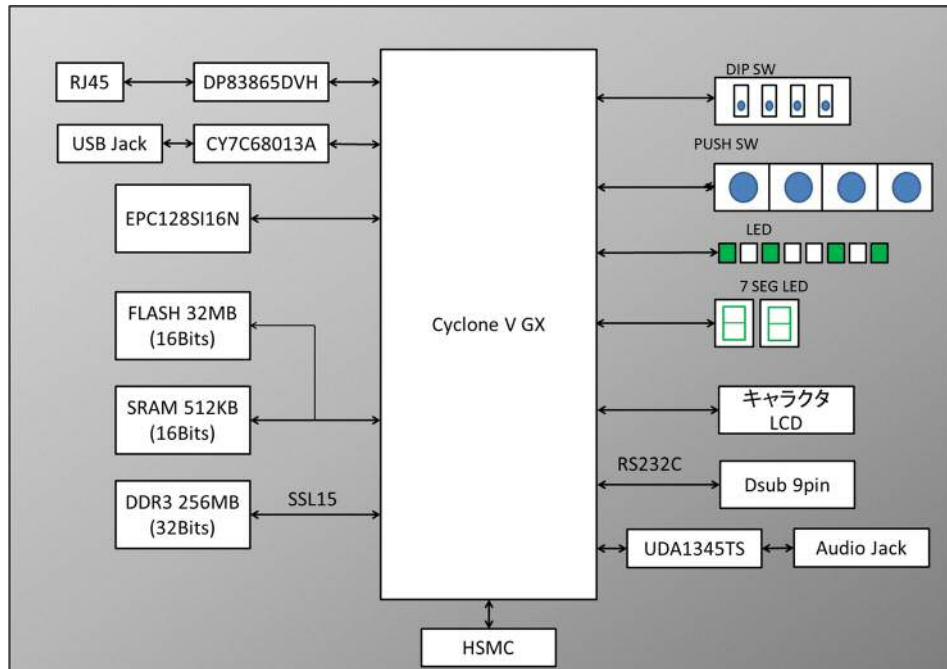

## 4.3 ブロックダイヤグラム

図 1 に当ボードのブロックダイヤグラムを示します。当ボードは Cyclone V GX FPGA の評価ボードという特性上、すべての機能が Cyclone V GX FPGA に集約されています。

図 1 Beryll ボードブロックダイヤグラム

## 4.4 ボード仕様

この章では、当ボードのスイッチ・コネクタおよび部品のレイアウトに関して解説します。

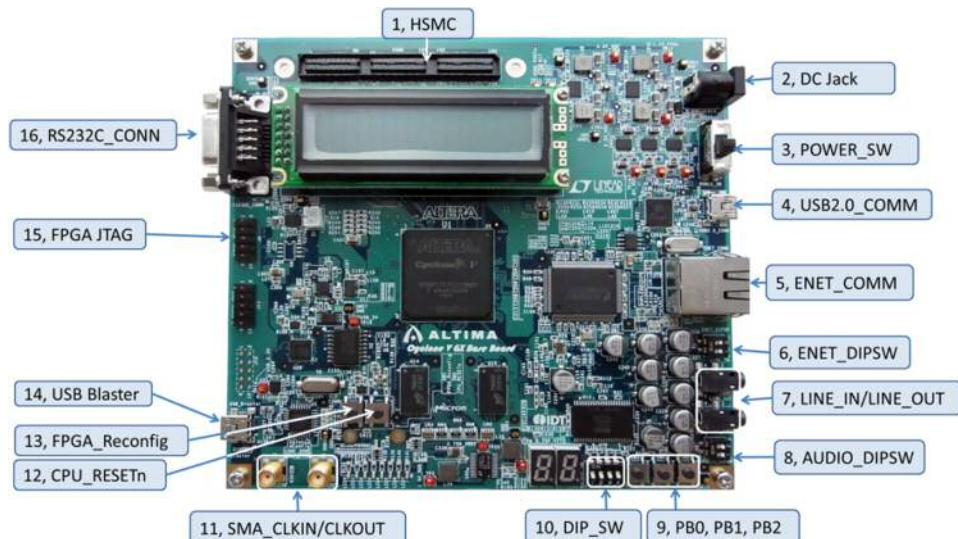

### 4.4.1 Beryll スイッチ/ コネクタ レイアウト

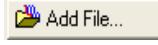

図 2 に当ボードのスイッチ / コネクタのレイアウトを示します。

図2 Beryll スイッチ,コネクタレイアウト

- |                    |                               |

|--------------------|-------------------------------|

| 1 HSMC             | 9 汎用プッシュスイッチ                  |

| 2 DC ジャック          | 10 汎用 DIP スイッチ                |

| 3 電源スイッチ           | 11 SMA コネクタ                   |

| 4 USB2.0 ミニ-B コネクタ | 12 リセット用プッシュスイッチ              |

| 5 イーサネットコネクタ RJ45  | 13 FPGA リコンフィギュレーション用プッシュスイッチ |

| 6 イーサネット DIP スイッチ  | 14 USB ブラスター用コネクタ             |

| 7 オーディオライン入力/出力    | 15 FPGA 用 JTAG コネクタ（未搭載）      |

| 8 オーディオ DIP スイッチ   | 16 RS232C コネクタ                |

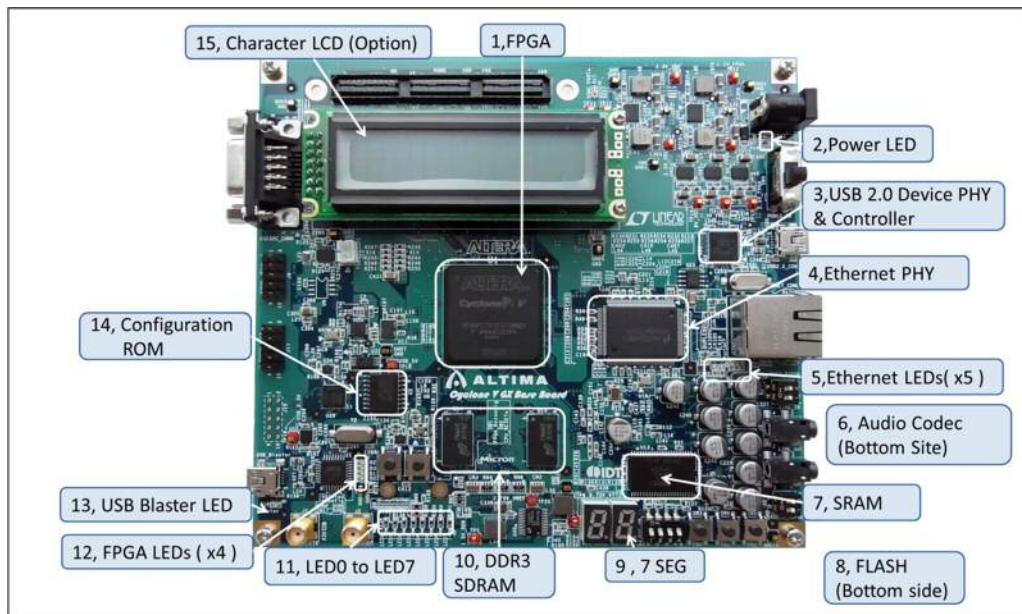

#### 4.4.2 Beryll 部品レイアウト

図3に当ボードの主な部品レイアウトを示します。

図3 Beryll コンポーネント・レイアウト

- |                                                        |                                                                   |

|--------------------------------------------------------|-------------------------------------------------------------------|

| 1 Cyclone V GX FPGA                                    | 9 7 セグ LED                                                        |

| 2 パワー LED                                              | 10 DDR3 SDRAM                                                     |

| 3 USB2.0 デバイスPHY コントローラ                                | 11 ユーザー LED                                                       |

| 4 イーサネット PHY                                           | 12 FPGA ステータス LED × 4<br>(nSTATUS/ nCONFIG/ CONF_DONE/ INIT_DONE) |

| 5 イーサネット LED × 5<br>(ACT/ LK10/ LK100/ LK1000/ DUPLEX) | 13 USB_BLASTER LED                                                |

| 6 オーディオ・コーデック                                          | 14 コンフィギュレーション・ロム                                                 |

| 7 SRAM                                                 | 15 キャラクタ LCD ( Option)                                            |

| 8 FLASH                                                |                                                                   |

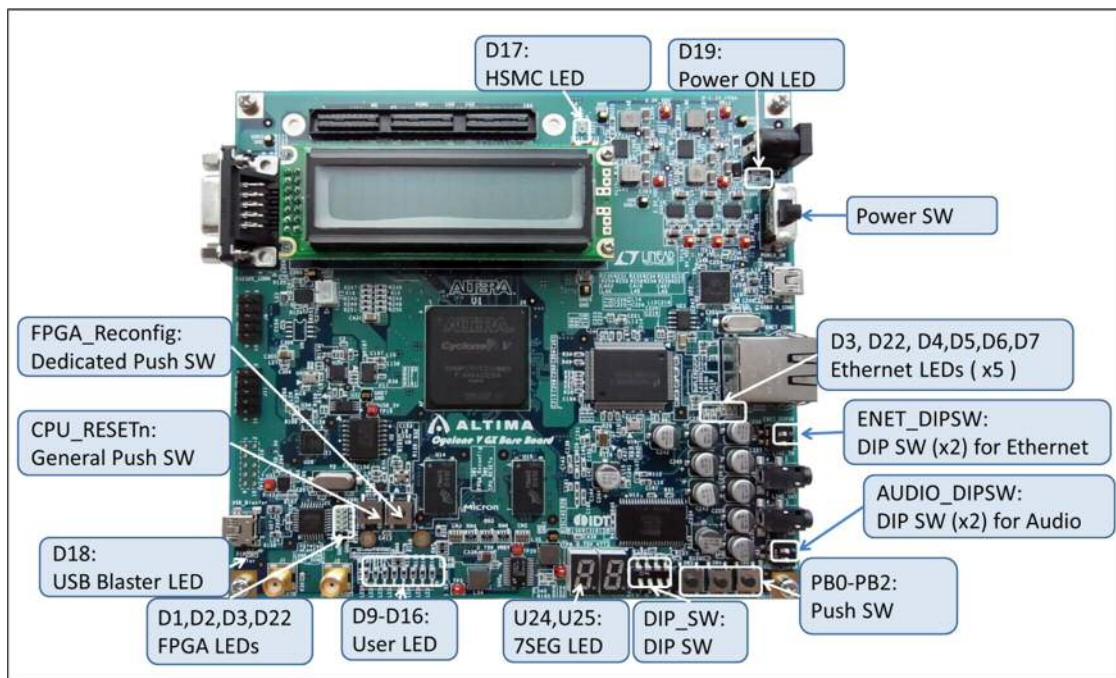

#### 4.4.3 Beryll スイッチ / LED レイアウト及び仕様

図 4 に当ボードのスイッチ / LED のレイアウトを示します

図 4 スイッチおよび各 LED の位置

表 2 に各 LED の機能を示します。

表 2 LED 仕様

| 部品位置     | 機能                           |

|----------|------------------------------|

| D1       | FPGA CONF_DONE チェック用 LED     |

| D2       | FPGA nSTATUS チェック用 LED       |

| D3       | FPGA nCONFIG チェック用 LED       |

| D4       | ACT : 通信時の確認用LED             |

| D5       | LK10 : 10Mbps通信時のリンク確認用LED   |

| D6       | LK100 : 100Mbps通信時のリンク確認用LED |

| D7       | LK1000 : 1Gbps通信時のリンク確認用LED  |

| D8       | DUPLEX : 全二重通信時の確認用LED       |

| D9-D16   | 汎用 LED x8                    |

| D17      | HSMCドータボード実装時LED             |

| D18      | USB Blasterケーブル接続確認          |

| D19      | +12V電源 LED                   |

| D22      | FPGA INIT_DONE確認用のLED        |

| U24, U25 | 汎用7セグメントLED x2               |

表3に各スイッチの機能を示します。

表3 スイッチ仕様

| 部品ロケーション                | 初期値      | 機能                                                                                                                                                                                    |

|-------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER_SW                | 下スライド    | 下スライド:電源OFF, 上スライド:電源ON                                                                                                                                                               |

| ENET_DIPSW              | 2つともOPEN | CRS/RGMII_SEL0<br>Open : RGMII - 3COM<br>Short : RGMII - HP<br>COL/CLK_MAC_FREQ<br>Open : 125MHz output<br>Short : 25MHz output<br>二つともOpenでお使いください                                   |

| AUDIO_DIPSW             | 2つともOPEN | AUDIO_MP2<br>Open : StaticPin Low or FPGA Control<br>Short : StaticPin and Mid Voltage<br><br>AUDIO_MP4<br>Open : StaticPin High or FPGA Control<br>Short : StaticPin and Mid Voltage |

| DIP_SW                  | なし       | 汎用ディップスイッチ ( x 4 )                                                                                                                                                                    |

| CPU_RESETn, PB0,PB1,PB2 | なし       | 汎用プッシュSW                                                                                                                                                                              |

| FPGA_Reconfig           | なし       | FPGAのリコンフィグレーションプッシュSW                                                                                                                                                                |

## 5. Beryll 搭載デバイス

この章では、当ボードを使用する際にお客様がご使用になられる FPGA 及び周辺に搭載されている各種コンポーネントについて解説します。

### 5.1 Cyclone V GX FPGA

当ボードにはアルテラ社 28nm ローコスト FPGA Cyclone V GX が搭載されています。搭載されている Cyclone V GX FPGA の仕様を表 4 に示します。

表 4. Cyclone V GX FPGA Specification

| デバイス   | コア・ファブリック |              |                      |              |              |       | インタコネクト     |             |             | ハード IP        |                 |

|--------|-----------|--------------|----------------------|--------------|--------------|-------|-------------|-------------|-------------|---------------|-----------------|

|        | LE 数      | メモリ<br>ブロック数 | ブロック・<br>メモリ<br>(Kb) | MLAB<br>(Kb) | DSP<br>ブロック数 | PLL 数 | トランシーバ<br>数 | GPIO<br>ピン数 | LVDS<br>ペア数 | PCIe<br>ブロック数 | メモリ・<br>コントローラ数 |

| 5CGXC4 | 50K       | 250          | 2,500                | 295          | 70           | 6     | 6           | 336         | 90          | 2             | 2               |

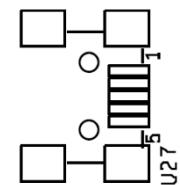

### 5.2 FPGA および コンフィギュレーション・デバイスへのプログラミング

FPGA と EPCS コンフィギュレーション・ロムへのプログラミングには、当ボードに添付するミニ USB ケーブルを(U27) の On-Board USB-Blaster™ に接続してコンフィギュレーション・ファイルの書き込みを行います。そのため、別途アルテラ社の USB-Blaster ケーブルなどのプログラミング・ハードウェアが必要ありません。

#### 5.2.1 はじめに

Quartus® II 開発ソフトウェアの Programmer を使用し、デバイスにプログラミング (Configuration file の書き込み)を行います。はじめて使用する場合は、各プログラミング・ハードウェアのドライバ・インストールが必要です。

#### 5.2.2 FPGA へのプログラミング操作方法

ここでは、プログラミングの基本操作を紹介します。

##### A. Programmer の起動

プログラミング・ハードウェアを接続し、Quartus II 開発ソフトウェアの Tools メニュー ⇒ Programmer または、

ボタンをクリックします。

## B. プログラミング・モードの選択

Mode のプルダウン・リストより、デバイスへの書き込みを実行する手法を選択します。

当ボードでは、JTAG を選択します。

## C. プログラミング・ハードウェアの設定

- a. Hardware Setup ボタンをクリックします。

- b. Hardware Setup ウィンドウの Hardware Settings タブを選択します。

- c. Current selected hardware のプルダウン・リストから、使用するプログラミング・ハードウェアを選択します。(④へ進んでください。) プルダウン・リストに使用するプログラミング・ハードウェアがない場合は、Add Hardware ボタンをクリックします。

- d. Add Hardware ダイアログ・ボックスの Hardware type から USB-Blaster を選択し、OK ボタンをクリックします。

- e. Hardware Setup ウィンドウの Currently selected hardware から USB-Blaster を選択し、Close ボタンをクリックします。

## D. プログラミング

- a. ボタンをクリックし、デバイスに書き込むプログラミング・ファイル(\*.SOF)を選択します。

- b. プログラミング・オプションは、デバイスにデータを書き込む時は、「Program / Configure」にチェックを入れてください。

- c. ボタンをクリックし、プログラミングを開始します。

### 《参考情報》

※ POF ファイル(\*.pof)： MAX<sup>®</sup> CPLD シリーズ、コンフィギュレーション・デバイス用のプログラミングファイル

※ SOF ファイル(\*.sof)： Stratix<sup>®</sup> FPGA、Arria<sup>®</sup> FPGA および Cyclone FPGA などの FPGA 用のプログラミング・ファイル

※ JIC ファイル(\*.jic)： コンフィギュレーション・ロム用のプログラミング・ファイル

### 《参考情報》

#### ◆ Program / Configure

デバイスへプログラミング・データを書き込み(プログラミング)します。

#### ◆ Verify

Programmer に登録されたプログラミング・データの内容と、デバイスに書き込まれたプログラミング・データを比較し検証します。

◆ Blank-Check

デバイスの中身が空であること、つまり完全に消去されていることを確認します。

◆ Examine

MAX CPLD デバイスやコンフィギュレーション・デバイスに既に書き込まれているプログラミング・データを吸い上げます。

- ※ Security Bit オプション(下記)を有効にして書き込んであるデータの場合、正しいデータを吸い出すことができません。

- ※ Examine を実行しても、デバイス内のデータは消去されません。

- ※ 吸い出されたデータからデザイン・ファイルへ復元することはできません。

◆ Security Bit

デバイスに書き込まれたデータの検査や、Examine によりロードされたデータが再プログラミングされても復成されることを防ぎます。(MAX<sup>®</sup> 7000 および MAX<sup>®</sup> 3000 のみでサポート)

◆ Erase

MAX CPLD デバイスやコンフィギュレーション・デバイス内のデータを消去します。

◆ ISP CLAMP

IPS ファイル(\*.ips)を活用して、プログラミング中の I/O ピン状態を設定します。

(MAX<sup>®</sup> 7000B、MAX<sup>®</sup> II のみサポート)

## 5.3 EPCS configuration ROMへのプログラミング

### 5.3.1 はじめに

FPGA デバイスの JTAG Indirect Configuration (以下 JIC) 機能を利用して、JTAG インタフェースをサポートしていない EPCS デバイスを JTAG チェーン経由でプログラミングすることが可能になります。

### 5.3.2 JIC の概要

Cyclone V FPGA デバイスのコンフィギュレーション・デバイスとして EPCS デバイスを使用する場合、データ転送方式はアクティブ・シリアル・コンフィギュレーション・モード (AS モード) をサポートしています。AS モードでコンフィギュレーションを行う場合は、EPCS コンフィギュレーション・デバイスに、AS モードでプログラミングするための 10 ピン・ヘッダが必要です。一方、FPGA に対して JTAG ポート経由でデータのコンフィギュレーションや、SignalTap<sup>®</sup> II によるデバッグを行う場合は、JTAG 用の 10 ピン・ヘッダも必要です。

しかし JIC 機能を活用すると FPGA 内部のシリアル・フラッシュ・ローダ・デザインがブリッジとなり、EPCS デバイスに対するプログラミングが JTAG ポート経由で行えるようになります。そのため、AS モード用の 10 ピン・ヘッダを用意する必要がなくなります。それにより基板面積を縮小し、さらなる低コストを実現することが可能です。

### 5.3.3 EPCS コンフィギュレーション・デバイスへのプログラミング 操作方法

シリアル・フラッシュ・ローダ経由のプログラミングは、従来の SOF ファイルや POF ファイルではなく、JIC ファイルで行います。FPGA 用のコンフィギュレーション・ファイルの SOF ファイルから JIC ファイルを作成し、プログラミングを実行します。

操作フローは以下のとおりです。

ステップ 1 : デザインのコンパイル(プログラミング・ファイルの作成)

ステップ 2 : JIC ファイルの作成

ステップ 3 : プログラミング

#### ステップ 1. デザインのコンパイル

JIC ファイルのもととなるコンフィギュレーション・ファイル (.sof) を生成するため、デザインのコンパイルを行います。

- Processing メニュー ⇒ Start Compilation を選択、または ボタンをクリック

#### ステップ 2. JIC ファイルの作成

コンパイル後に生成された SOF ファイルから、JIC 用のプログラミング・ファイルである \*.jic ファイルを作成します。

- 1) File メニュー ⇒ Convert Programming Files を選択します。

- 2) Output Programming File 項目にて、作成するファイル・フォーマット、コンフィギュレーション・デバイス、出力ファイル名を設定します。

- Programming file type に JTAG Indirect Configuration File (.jic) を選択します。

- Configuration device にプログラミングするコンフィギュレーション・デバイスの型式を設定します。当ボードでは、EPCS128 を選択します。

- File name に出力ファイルの生成パスと出力ファイル名を指定します。

- Input files to convert 項目に、シリアル・フラッシュ・ローダ・デザインを使用する FPGA の型式を選択します。

- Flash Loader 行を選択し、Add Device ボタンをクリックします。

- Select Device ダイアログ・ボックスにて Device family を Cyclone V GX、Device name を選択し、OK ボタンをクリックします。

- JIC ファイルのもととなるコンフィギュレーション・ファイル (.sof) を指定します。

- SOF Data 行を選択し、Add File ボタンをクリックします。

- 変換する sof ファイルを選択し、“開く”ボタンをクリックします。

- プログラミング・ファイルを圧縮する場合は、圧縮したい SOF ファイルを選択し、

Properties ボタンをクリックします。SOF File Properties ダイアログ・ボックスにて、Compression オプションにチェックを入れ OK ボタンをクリックします。

- Generate ボタンをクリックします。

“Generated <jic ファイル名> successfully” のメッセージが表示され、JIC ファイルの作成が完了します。

### ステップ 3. プログラミング

生成した JIC ファイルを EPCS デバイスに JTAG モードでプログラミングします。

- 1) Programmer を起動します。

Tools メニュー ⇒ Programmer を選択、または  ボタンをクリックします。

- 2) 使用するハードウェア(ダウンロード・ケーブル)および Mode に JTAG を選択します。

- 3)  ボタンをクリックし、JIC ファイルを選択します。

- 4) JIC ファイル行の Program/Configure オプションにチェックを入れます。

- 5)  ボタンをクリックし、プログラミングを開始します。

はじめに FPGA デバイス内のシリアル・フラッシュ・ローダが有効になり、その後シリアル・フラッシュ・ローダを経由して EPCS プログラミングが実行されます。プログラミングが正常に終了すると、Progress のゲージ(Programmer 画面の右上)が 100% になり、Message ダイアログ・ボックスにはプログラミングの成功を知らせるメッセージが確認できます。

以上で、JTAG Indirect Configuration による EPCS デバイスのプログラミングは終了です。

## 5.4 コネクタピニアサイン

図4に当ボードのコネクタ位置及び各コネクタのピン配置を示します。

図4. Beryll コネクタ位置

### 01. U35 (DC ジャック)

| ピン | 信号名 | ピン | 信号名 |

|----|-----|----|-----|

| 1  | 12V | 2  | NC  |

| 3  | GND |    |     |

### 02. U20 (USB 2.0\_CONN)

| ピン | 信号名   | ピン | 信号名 |

|----|-------|----|-----|

| 1  | V_BUS | 2  | D+  |

| 3  | D-    | 4  | ID  |

| 5  | G     |    |     |

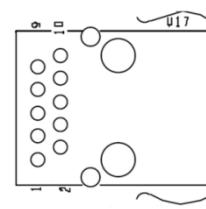

### 03. U17 (ENET\_CONN)

| ピン | 信号名     | ピン | 信号名     |

|----|---------|----|---------|

| 1  | TD0_P   | 2  | TD0_N   |

| 3  | TD1_P   | 4  | TD1_N   |

| 5  | TD2_P   | 6  | TD2_N   |

| 7  | TD3_P   | 8  | TD3_N   |

| 9  | VCC     | 10 | GND     |

| 11 | GND_TAB | 12 | GND_TAB |

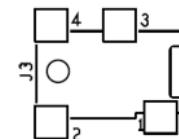

### 04. J3 (Audio ラインイン)

| ピン | 信号名 | ピン | 信号名 |

|----|-----|----|-----|

| 1  | GND | 2  | L   |

| 3  | R   | 4  | NC  |

**05. J4 (Audio ラインアウト)**

| ピン | 信号名 | ピン | 信号名 |

|----|-----|----|-----|

| 1  | GND | 2  | L   |

| 3  | R   | 4  | NC  |

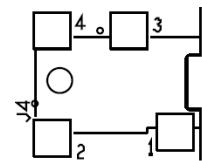

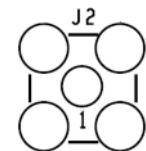

**06. J2 (SMA CLKIN)**

| ピン | 信号名        | ピン | 信号名 |

|----|------------|----|-----|

| 1  | SMA_CLK_IN | 2  | NC  |

| 3  | NC         | 4  | NC  |

| 5  | NC         |    |     |

**07. J1 (SMA CLKOUT)**

| ピン | 信号名         | ピン | 信号名 |

|----|-------------|----|-----|

| 1  | SMA_CLK_OUT | 2  | NC  |

| 3  | NC          | 4  | NC  |

| 5  | NC          |    |     |

**08. U27 (USB-Blaster)**

| ピン | 信号名   | ピン | 信号名 |

|----|-------|----|-----|

| 1  | V_BUS | 2  | D+  |

| 3  | D-    | 4  | ID  |

| 5  | G     |    |     |

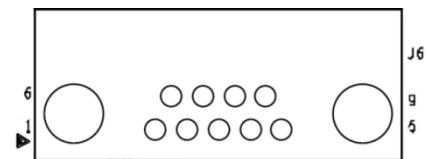

**9. J6 (RS232C DSub9 ピンメスコネクタ)**

| ピン | 信号名      | ピン | 信号名      |

|----|----------|----|----------|

| 1  | NC       | 2  | UART_TXD |

| 3  | UART_RXD | 4  | NC       |

| 5  | NC       | 6  | NC       |

| 7  | NC       | 8  | NC       |

| 9  | NC       |    |          |

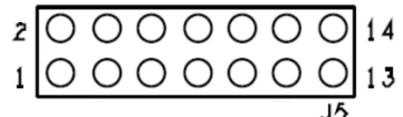

**10.J5 (キャラクタLCD)**

| ピン | 信号名       | ピン | 信号名       |

|----|-----------|----|-----------|

| 1  | NC        | 2  | NC        |

| 3  | NC        | 4  | LCD_RS    |

| 5  | LCD_RW    | 6  | LCD_E     |

| 7  | LCD_DATA0 | 8  | LCD_DATA1 |

| 9  | LCD_DATA2 | 10 | LCD_DATA3 |

| 11 | LCD_DATA4 | 12 | LCD_DATA5 |

| 13 | LCD_DATA6 | 14 | LCD_DATA7 |

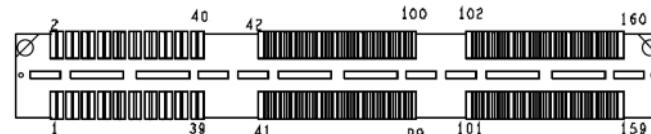

## 11. J8 (HSMC コネクタ)

| ピン | 信号名               | ピン | 信号名              | ピン  | 信号名               | ピン  | 信号名              |

|----|-------------------|----|------------------|-----|-------------------|-----|------------------|

| 1  |                   | 2  |                  | 81  |                   | 82  |                  |

| 3  |                   | 4  |                  | 83  | HSMC_2_DATAOUT6_P | 84  | HSMC_2_DATAIN6_P |

| 5  |                   | 6  |                  | 85  | HSMC_2_DATAOUT6_N | 86  | HSMC_2_DATAIN6_N |

| 7  |                   | 8  |                  | 87  |                   | 88  |                  |

| 9  |                   | 10 |                  | 89  | HSMC_2_DATAOUT7_P | 90  | HSMC_2_DATAIN7_P |

| 11 |                   | 12 |                  | 91  | HSMC_2_DATAOUT7_N | 92  | HSMC_2_DATAIN7_N |

| 13 |                   | 14 |                  | 93  |                   | 94  |                  |

| 15 |                   | 16 |                  | 95  | HSMC_2_CLKOUT_P   | 96  | HSMC_2_CLKIN_P   |

| 17 | GX_TXD3_P         | 18 | GX_RXD3_P        | 97  | HSMC_2_CLKOUT_N   | 98  | HSMC_2_CLKIN_N   |

| 19 | GX_TXD3_N         | 20 | GX_RXD3_N        | 99  |                   | 100 |                  |

| 21 | GX_TXD2_P         | 22 | GX_RXD2_P        | 101 | HSMC_3_DATAOUT0_P | 102 | HSMC_3_DATAIN0_P |

| 23 | GX_TXD2_N         | 24 | GX_RXD2_N        | 103 | HSMC_3_DATAOUT0_N | 104 | HSMC_3_DATAIN0_N |

| 25 | GX_TXD1_P         | 26 | GX_RXD1_P        | 105 |                   | 106 |                  |

| 27 | GX_TXD1_N         | 28 | GX_RXD1_N        | 107 | HSMC_3_DATAOUT1_P | 108 | HSMC_3_DATAIN1_P |

| 29 | GX_RXD0_P         | 30 | GX_RXD0_P        | 109 | HSMC_3_DATAOUT1_N | 110 | HSMC_3_DATAIN1_N |

| 31 | GX_RXD0_N         | 32 | GX_RXD0_N        | 111 |                   | 112 |                  |

| 33 | HSMC_1_DATA0      | 34 | HSMC_1_DATA1     | 113 | HSMC_3_DATAOUT2_P | 114 | HSMC_3_DATAIN2_P |

| 35 | HSMC_1_DATA2      | 36 | HSMC_1_DATA4     | 115 | HSMC_3_DATAOUT2_N | 116 | HSMC_3_DATAIN2_N |

| 37 | HSMC_1_DATA4      | 38 | HSMC_1_DATA5     | 117 |                   | 118 |                  |

| 39 | HSMC_1_CLKOUT     | 40 | HSMC_1_CLKIN     | 119 | HSMC_3_DATAOUT3_P | 120 | HSMC_3_DATAIN3_P |

| 41 | HSMC_DATA0        | 42 | HSMC_DATA1       | 121 | HSMC_3_DATAOUT3_N | 122 | HSMC_3_DATAIN3_N |

| 43 | HSMC_DATA2        | 44 | HSMC_DATA3       | 123 |                   | 124 |                  |

| 45 |                   | 46 |                  | 125 | HSMC_3_DATAOUT4_P | 126 | HSMC_3_DATAIN4_P |

| 47 | HSMC_2_DATAOUT0_P | 48 | HSMC_2_DATAIN0_P | 127 | HSMC_3_DATAOUT4_N | 128 | HSMC_3_DATAIN4_N |

| 49 | HSMC_2_DATAOUT0_N | 50 | HSMC_2_DATAIN0_N | 129 |                   | 130 |                  |

| 51 |                   | 52 |                  | 131 | HSMC_3_DATAOUT5_P | 132 | HSMC_3_DATAIN5_P |

| 53 | HSMC_2_DATAOUT1_P | 54 | HSMC_2_DATAIN1_P | 133 | HSMC_3_DATAOUT5_N | 134 | HSMC_3_DATAIN5_N |

| 55 | HSMC_2_DATAOUT1_N | 56 | HSMC_2_DATAIN1_N | 135 |                   | 136 |                  |

| 57 |                   | 58 |                  | 137 | HSMC_3_DATAOUT6_P | 138 | HSMC_3_DATAIN6_P |

| 59 | HSMC_2_DATAOUT2_P | 60 | HSMC_2_DATAIN2_P | 139 | HSMC_3_DATAOUT6_N | 140 | HSMC_3_DATAIN6_N |

| 61 | HSMC_2_DATAOUT2_N | 62 | HSMC_2_DATAIN2_N | 141 |                   | 142 |                  |

| 63 |                   | 64 |                  | 143 | HSMC_3_DATAOUT7_P | 144 | HSMC_3_DATAIN7_P |

| 65 | HSMC_2_DATAOUT3_P | 66 | HSMC_2_DATAIN3_P | 145 | HSMC_3_DATAOUT7_N | 146 | HSMC_3_DATAIN7_N |

| 67 | HSMC_2_DATAOUT3_N | 68 | HSMC_2_DATAIN3_N | 147 |                   | 148 |                  |

| 69 |                   | 70 |                  | 149 | HSMC_3_DATAOUT8_P | 150 | HSMC_3_DATAIN7_P |

| 71 | HSMC_2_DATAOUT4_P | 72 | HSMC_2_DATAIN4_P | 151 | HSMC_3_DATAOUT8_N | 152 | HSMC_3_DATAIN7_N |

| 73 | HSMC_2_DATAOUT4_N | 74 | HSMC_2_DATAIN4_N | 153 |                   | 154 |                  |

| 75 |                   | 76 |                  | 155 | HSMC_3_CLKOUT_P   | 156 | HSMC_3_CLKIN_P   |

| 77 | HSMC_2_DATAOUT5_P | 78 | HSMC_2_DATAIN5_P | 157 | HSMC_3_CLKOUT_N   | 158 | HSMC_3_CLKIN_N   |

| 79 | HSMC_2_DATAOUT5_N | 80 | HSMC_2_DATAIN5_N | 159 |                   | 160 |                  |

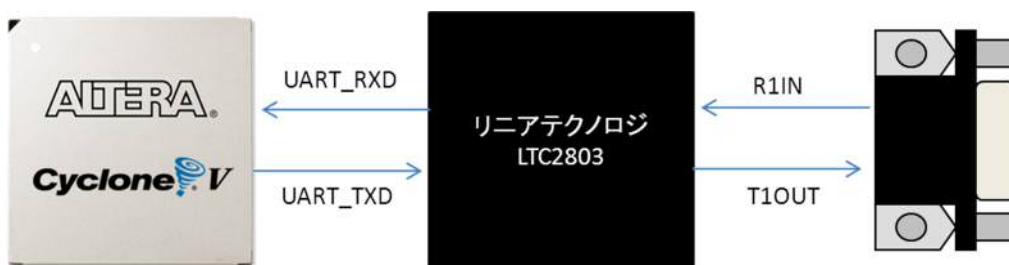

## 5.5 シリアル・ポート

当ボードは、1 ポートの非同期のシリアル・ポートを装備しています。RS232C インタフェース用にリニアテクノロジー社の LTC2803 FPGA のトランシーバ及び9ピンの D SUB コネクタを使用しています。FPGA、LTC2803 及び D SUB コネクタのピン情報については、以下の図 5 及びピンリストをご確認ください。なお、シリアルケーブルをご購入の際は、ストレート仕様のものを購入下さい。リニアテクノロジー社 LTC2803 の資料に関しては以下の URL より入手してください。

<http://www.linear.com/product/LTC2803>

\*上記のリンク先は予告なく変更されることがあります。

図 5. FPGA 、LTC2803、DB9 コネクタ接続情報

表 5. RS232C ピンリスト

| 回路図信号名   | 信号の詳細   | FPGA ピン番号  | LTC2803 ピン番号<br>(FPGA 側) | LTC2803 ピン番号<br>(D-SUB 側) | D-SUB ピン番号 |

|----------|---------|------------|--------------------------|---------------------------|------------|

| UART_XD  | トランスマッタ | Bank 8A_K6 | 14                       | 3                         | 2          |

| UART_RXD | レシーバ    | Bank 8A_L7 | 16                       | 1                         | 3          |

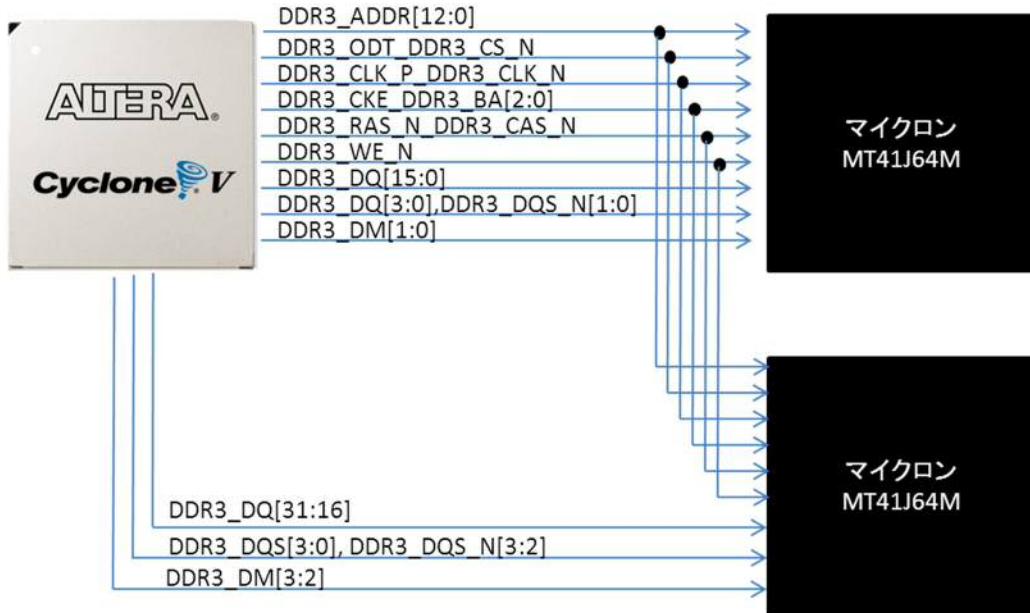

## 5.6 DDR3 SDRAM

当ボードには、マイクロンテクノロジー社の MT41J64M16JT (16bit, 128MByte, 800MHz) を 2 つ搭載し、FPGA の HMC (ハード・メモリ・コントローラ) と接続されています。お客様は、添付のリファレンスデザインを使用していくことで、Cyclone V GX FPGA のハード・メモリ・コントローラを評価して頂く事が可能です。Cyclone V GX FPGA 並びに DDR3 メモリのピン情報は図 6 をご確認ください。

マイクロン社 MT41J64M16JT のデータシートに関しては、以下の URL より入手してください。

<http://www.micron.com/part/dram/ddr3-sdram/mt41j64m16jt-15e>

\*上記のリンク先は予告なく変更されることがあります。

\*当ボードに搭載される DDR3 メモリは DDR3 800MHz を実現するための条件を満たす相当品に変更させていただくことがあります、あらかじめご了承ください。

図 6 FPGA と DDR3 メモリの接続

表 6. FPGA 及び DDR3 メモリピン情報

| 信号名          | FPGA<br>ピン番号 | DDR#0<br>ピン番号 | DDR#1<br>ピン番号 | 信号名         | FPGA<br>ピン番号 | DDR#0<br>ピン番号 | DDR#1<br>ピン番号 |

|--------------|--------------|---------------|---------------|-------------|--------------|---------------|---------------|

| DDR3_ADDR0   | AE6          | N3            | N3            | DDR3_DQ8    | AC15         | D7            |               |

| DDR3_ADDR1   | AF6          | P7            | P7            | DDR3_DQ9    | AB15         | C3            |               |

| DDR3_ADDR2   | AF7          | P3            | P3            | DDR3_DQ10   | AC14         | C8            |               |

| DDR3_ADDR3   | AF8          | N2            | N2            | DDR3_DQ11   | AF13         | C2            |               |

| DDR3_ADDR4   | U10          | P8            | P8            | DDR3_DQ12   | AB16         | A7            |               |

| DDR3_ADDR5   | U11          | P2            | P2            | DDR3_DQ13   | AA16         | A2            |               |

| DDR3_ADDR6   | AE9          | R8            | R8            | DDR3_DQ14   | AE14         | B8            |               |

| DDR3_ADDR7   | AF9          | R2            | R2            | DDR3_DQ15   | AF18         | A3            |               |

| DDR3_ADDR8   | AB12         | T8            | T8            | DDR3_DQ16   | AD16         |               | F3            |

| DDR3_ADDR9   | AB11         | R3            | R3            | DDR3_DQ17   | AD17         |               | F7            |

| DDR3_ADDR10  | AC9          | I7            | I7            | DDR3_DQ18   | AC18         |               | F2            |

| DDR3_ADDR11  | AC8          | R7            | R7            | DDR3_DQ19   | AF19         |               | F8            |

| DDR3_ADDR12  | AB10         | N7            | N7            | DDR3_DQ20   | AC17         |               | H3            |

| DDR3_BA0     | V10          | M2            | M2            | DDR3_DQ21   | AB17         |               | H8            |

| DDR3_BA1     | AD8          | N8            | N8            | DDR3_DQ22   | AF21         |               | G2            |

| DDR3_BA2     | AE8          | M3            | M3            | DDR3_DQ23   | AE21         |               | H7            |

| DDR3_DM0     | AF11         | E7            |               | DDR3_DQ24   | AE15         |               | D7            |

| DDR3_DM1     | AE18         | D3            |               | DDR3_DQ25   | AE16         |               | C3            |

| DDR3_DM2     | AE20         | E7            |               | DDR3_DQ26   | AC20         |               | C8            |

| DDR3_DM3     | AA14         |               | D3            | DDR3_DQ27   | AD21         |               | C2            |

| DDR3_CS_N    | R11          | L2            | L2            | DDR3_DQ28   | AF16         |               | A7            |

| DDR3_CAS_N   | W10          | K3            | K3            | DDR3_DQ29   | AF17         |               | A2            |

| DDR3_RAS_N   | Y10          | J3            | J3            | DDR3_DQ30   | AD23         |               | B8            |

| DDR3_WE_N    | T9           | L3            | L3            | DDR3_DQ31   | AF23         |               | A3            |

| DDR3_RESET_N | AE19         | T2            | T2            | DDR3_DQS_P1 |              | C7            |               |

| DDR3_ODT     | AD13         | K1            | K1            | DDR3_DQS_N1 |              | B7            |               |

| DDR3_DQ0     | AA14         | F3            |               | DDR3_DQS_P0 |              | F3            |               |

| DDR3_DQ1     | Y14          | F7            |               | DDR3_DQS_N0 |              | G3            |               |

| DDR3_DQ2     | AD11         | F2            |               | DDR3_DQS_P3 |              |               | C7            |

| DDR3_DQ3     | AD12         | F8            |               | DDR3_DQS_N3 |              |               | B7            |

| DDR3_DQ4     | Y13          | H3            |               | DDR3_DQS_P0 |              |               | F3            |

| DDR3_DQ5     | W12          | H8            |               | DDR3_DQS_N0 |              |               | G3            |

| DDR3_DQ6     | AD10         | G2            |               | DDR3_CLK_P  |              | J7            | J7            |

| DDR3_DQ7     | AF12         | H7            |               | DDR3_CLK_N  |              | K7            | K7            |

|              |              |               |               | DDR3_CKE    |              | K9            | K9            |

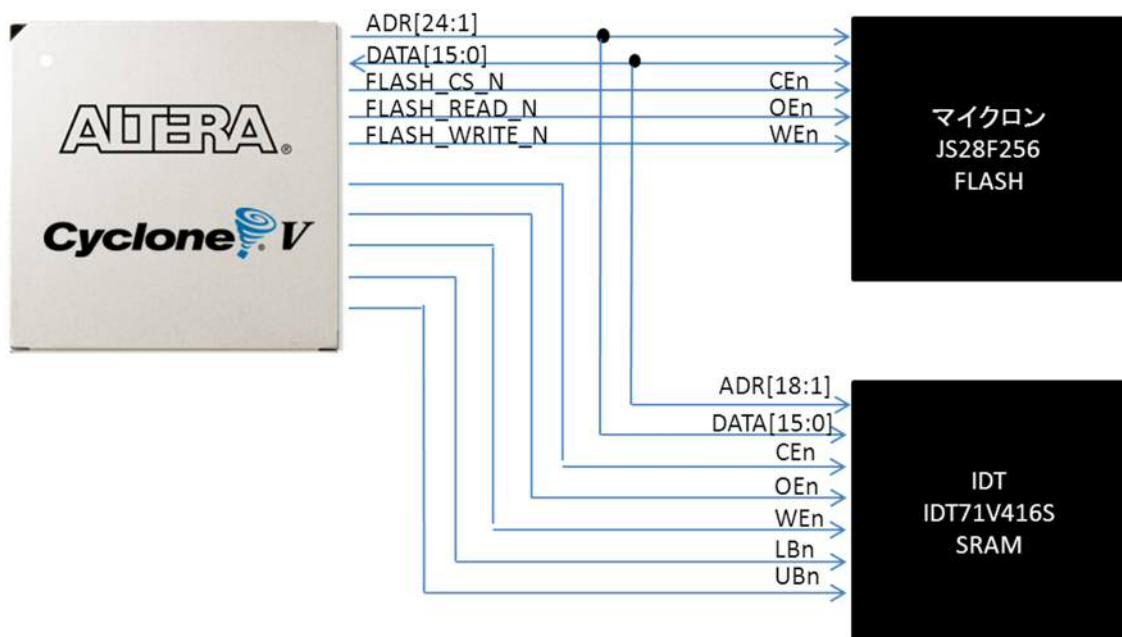

## 5.7 FLASH / SRAM

当ボードにはマイクロンテクノロジ社製 JS28F256M29EWL (16bit 幅, 256Mbits)FLASH ROM 及び IDT 社製 IDT71V416S10PHG8(16bit 幅、4Mbit )SRAM を搭載しております。アドレス、データバスは FLASH / SRAM 共有で使用されています。これらのデバイスは、Cyclone V GX FPGA で Nios® II プロセッサを使用する際に、Nios II のソフトウェアブート用として FLASH を、Nios II 用のキャッシュ ROM として SRAM をご利用頂く事が可能です。もちろん、汎用 FLASH、SRAM としての使用も可能ですので、ご活用ください。FLASH 及び SRAM と FPGA のピン情報は図 7 をご確認ください。

Flash ROM のデータシートは、以下の URL より入手してください。

<http://www.micron.com/partsnor-flash/parallel-nor-flash/js28f256m29ewla?pc={9A9BFAD5-DEE0-49F7-ACE8-ED039D2582D6}>

\*上記のリンク先は予告なく変更されることがあります。

SRAM のデータシートは、以下の URL より入手してください。

<http://ja.idt.com/products/memory-logic/srams/asynchronous-srams/71v416-33v-256k-x-16-asynchronous-static-ram-center-pwr-gnd-pinout>

\*上記のリンク先は予告なく変更されることがあります。

図 7. FPGA 及び FLASH/SRAM のピン情報

表 7. FPGA 及び FLASH/SRAM ピン情報

| 信号名             | FPGA<br>ピン番号 | FLASH<br>ピン番号 | SRAM<br>ピン番号 | 信号名           | FPGA<br>ピン番号 | FLASHピン<br>番号 | SRAMピン<br>番号 |

|-----------------|--------------|---------------|--------------|---------------|--------------|---------------|--------------|

| FLASH_ADDRESS1  | AD26         | A0            | A0           | FLASH_DATA0   | V24          | DQ0           | DQ0          |

| FLASH_ADDRESS2  | AF26         | A1            | A1           | FLASH_DATA1   | V23          | DQ1           | DQ1          |

| FLASH_ADDRESS3  | AE25         | A2            | A2           | FLASH_DATA2   | W26          | DQ2           | DQ2          |

| FLASH_ADDRESS4  | AF24         | A3            | A3           | FLASH_DATA3   | W25          | DQ3           | DQ3          |

| FLASH_ADDRESS5  | AE23         | A4            | A4           | FLASH_DATA4   | AA26         | DQ4           | DQ4          |

| FLASH_ADDRESS6  | AB22         | A5            | A5           | FLASH_DATA5   | AA24         | DQ5           | DQ5          |

| FLASH_ADDRESS7  | AD22         | A6            | A6           | FLASH_DATA6   | AB26         | DQ6           | DQ6          |

| FLASH_ADDRESS8  | AF22         | A7            | A7           | FLASH_DATA7   | AB25         | DQ7           | DQ7          |

| FLASH_ADDRESS9  | AA21         | A8            | A8           | FLASH_DATA8   | AC25         | DQ8           | DQ8          |

| FLASH_ADDRESS10 | Y20          | A9            | A9           | FLASH_DATA9   | AD25         | DQ9           | DQ9          |

| FLASH_ADDRESS11 | AD20         | A10           | A10          | FLASH_DATA10  | Y24          | DQ10          | DQ10         |

| FLASH_ADDRESS12 | V19          | A11           | A11          | FLASH_DATA11  | Y23          | DQ11          | DQ11         |

| FLASH_ADDRESS13 | Y19          | A12           | A12          | FLASH_DATA12  | AA23         | DQ12          | DQ12         |

| FLASH_ADDRESS14 | AB19         | A13           | A13          | FLASH_DATA13  | AA22         | DQ13          | DQ13         |

| FLASH_ADDRESS15 | AC19         | A14           | A14          | FLASH_DATA14  | AC23         | DQ14          | DQ14         |

| FLASH_ADDRESS16 | AD18         | A15           | A15          | FLASH_DATA15  | AC22         | DQ15/A-1      | DQ15         |

| FLASH_ADDRESS17 | AA18         | A16           | A16          | FLASH_CS_N    | U22          | CE_N          |              |

| FLASH_ADDRESS18 | Y18          | A17           | A17          | FLASH_READ_N  | V22          | OE_N          |              |

| FLASH_ADDRESS19 | W18          | A18           |              | FLASH_WRITE_N | W21          | WE_N          |              |

| FLASH_ADDRESS20 | V18          | A19           |              | SRAM_CS_N     | V20          |               | CS_N         |

| FLASH_ADDRESS21 | V17          | A20           |              | SRAM_OE_N     | U15          |               | OE_N         |

| FLASH_ADDRESS22 | U17          | A21           |              | SRAM_WRITE_N  | T17          |               | WE_N         |

| FLASH_ADDRESS23 | Y16          | A22           |              | SRAM_BE0_N    | U20          |               | BLE_N        |

| FLASH_ADDRESS24 | U16          | A23           |              | SRAM_BE1_N    | T19          |               | BLH_N        |

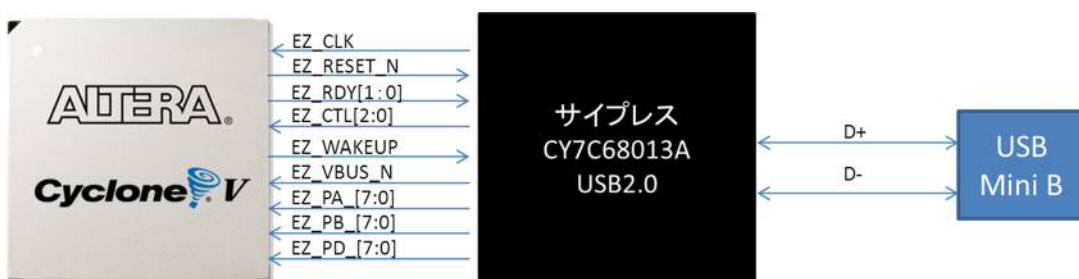

## 5.8 USB 2.0

当ボードには USB2.0 インタフェース用としてサイプレスセミコンダクタ社の EZ-USB® CY7C68013A-56LTXC を搭載しております。当デバイスは、USB2.0 トランシーバ、8051 マイクロプロセッサによる USB コントローラ、16KB RAM 等が統合された USB2.0 インタフェース用統合コントローラです。当ボードに搭載している Cyclone V GX FPGA は サイプレスセミコンダクタ社の EZ-USB より GPIO レベルで信号を受信します。FPGA 及び CY7C68013 のピン情報については、図 8 及びピン配置リストをご確認ください。サイプレス社 EZ-USB のデータシートに関しては、以下の URL より入手してください。

<http://www.cypress.com/?mpn=CY7C68013A-56LTXC>

\*上記のリンク先は予告なく変更されることがあります。

図 8. FPGA 及び EZ-USB の接続情報

表 8. FPGA 及び EZ-USB のピン情報

| 信号名    | FPGA<br>ピン番号 | USB<br>ピン番号 | 信号名        | FPGA<br>ピン番号 | USB<br>ピン番号 |

|--------|--------------|-------------|------------|--------------|-------------|

| EZ_PA0 | G25          | 33          | EZ_PD0     | B26          | 45          |

| EZ_PA1 | G24          | 34          | EZ_PD1     | B25          | 46          |

| EZ_PA2 | G22          | 35          | EZ_PD2     | C25          | 47          |

| EZ_PA3 | H25          | 36          | EZ_PD3     | D26          | 48          |

| EZ_PA4 | H24          | 37          | EZ_PD4     | D25          | 49          |

| EZ_PA5 | H23          | 38          | EZ_PD5     | D22          | 50          |

| EZ_PA6 | H22          | 39          | EZ_PD6     | E26          | 51          |

| EZ_PA7 | J23          | 40          | EZ_PD7     | E25          | 52          |

| EZ_PB0 | E24          | 18          | EZ_RDY0    | J25          | 1           |

| EZ_PB1 | E23          | 19          | EZ_RDY1    | J26          | 2           |

| EZ_PB2 | E21          | 20          | EZ_CLK     | K25          | 13          |

| EZ_PB3 | F24          | 21          | EZ_WAKEUP  | K26          | 44          |

| EZ_PB4 | F23          | 22          | EZ_RESET_N | L23          | 32          |

| EZ_PB5 | F22          | 23          | EZ_CTL0    | K24          | 29          |

| EZ_PB6 | F21          | 24          | EZ_CTL1    | K23          | 30          |

| EZ_PB7 | G26          | 25          | EZ_CTL2    | L24          | 31          |

## 5.9 10/100 イーサネット

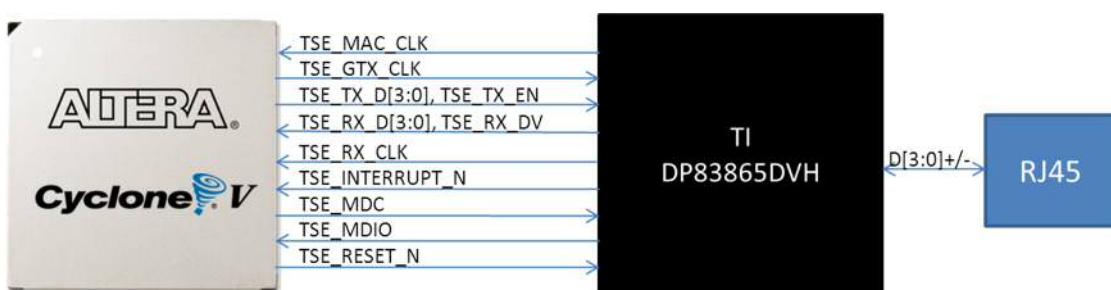

当ボードにはイーサネット・インターフェース用としてテキサス・インスツルメンツ社 DP83865DVH を搭載しております。テキサス・インスツルメンツ DP83865DVH は、1.8V, 0.18μ プロセスを用いた超低消費電力のイーサネット・インターフェース用トランシーバです。FPGA 及び DP83865DVH のピン情報については、図 9 及びピン配置リストをご確認ください。

本 LSI のデータシートに関しては、以下の URL より入手してください。

<http://www.ti.com/product/dp83865>

\*上記のリンク先は予告なく変更されることがあります。

図 9. FPGA 及び DP83865DVH の接続情報

表 9. FPGA 及び DP83865DVH のピン配置リスト

| 信号名             | FPGA<br>ピン番号 | DP83865<br>ピン番号 |

|-----------------|--------------|-----------------|

| TSE_MAC_CLK     | N20          | 85              |

| TSE_RESET_N     | P21          | 33              |

| TSE_RX_CLK      | R20          | 44              |

| TSE_RX_DV       | R25          | 41              |

| TSE_RX_D0       | R26          | 56              |

| TSE_RX_D1       | P26          | 55              |

| TSE_RX_D2       | P23          | 52              |

| TSE_RX_D3       | N25          | 51              |

| TSE_GTX_CLK     | F26          | 79              |

| TSE_TX_EN       | N23          | 62              |

| TSE_TX_D0       | N24          | 76              |

| TSE_TX_D1       | M26          | 75              |

| TSE_TX_D2       | M25          | 72              |

| TSE_TX_D3       | M24          | 71              |

| TSE_MDIO        | R23          | 80              |

| TSE_MDC         | P22          | 81              |

| TSE_INTERRUPT_N | P20          | 3               |

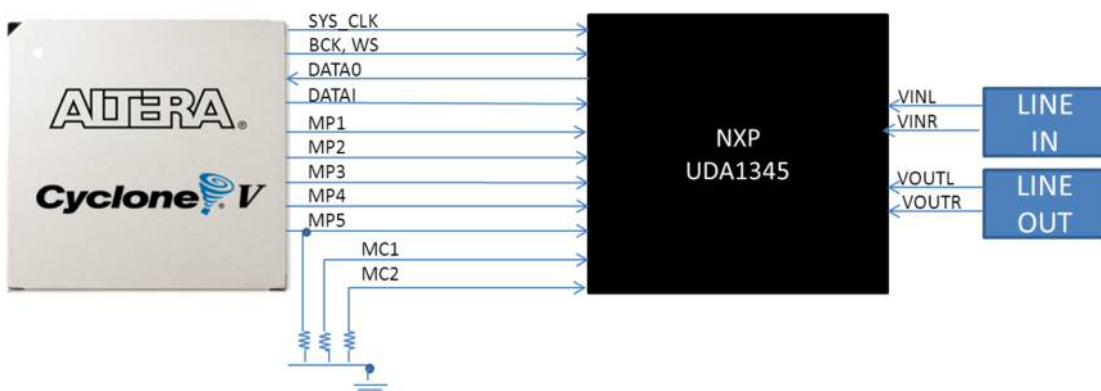

## 5.10 24 ビットオーディオ・コーデック

当ボードには Audio インタフェース用 24bit CODEC 用として NXP セミコンダクターズ 社の UDA1345TS を搭載しています。FPGA 及び DP83865DVH のピン情報については、図 10 及びピン配置リストをご確認ください。

本デバイスのデータシートに関しては、以下の URL より入手してください。

[http://www.nxp.com/documents/data\\_sheet/UDA1345TS.pdf](http://www.nxp.com/documents/data_sheet/UDA1345TS.pdf)

\*上記のリンク先は予告なく変更されることがあります。

図 10. FPGA 及び UDA1345 の接続情報

| 信号名          | FPGA<br>ピン番号 | Audio<br>ピン番号 |

|--------------|--------------|---------------|

| AUDIO_SYSCLK | Y25          | 12            |

| AUDIO_BCK    | Y26          | 16            |

| AUDIO_DI     | T26          | 18            |

| AUDIO_WS     | U25          | 17            |

| AUDIO_DO     | U26          | 19            |

| AUDIO_MC     | T22          | 8/21          |

| AUDIO_MP1    | T24          | 9             |

| AUDIO_MP2    | U24          | 13            |

| AUDIO_MP3    | V25          | 14            |

| AUDIO_MP4    | R24          | 15            |

| AUDIO_MP5    | T23          | 20            |

表 10. FPGA 及び UDA1345 のピン配置リスト

## 5.11 ユーザ・インターフェース

当ボードには、お客様が独自に設定可能な各種入力インターフェースが用意されています。8 個の LED、2 個の 7 セグ、4 個のプッシュボタン、1 個の DIP スイッチ、キャラクタ LCD、UART がユーザ・インターフェースとして用意されています。各ピンの仕様については、以下のピンリストをご確認ください。

| 信号名         | FPGA<br>ピン<br>番号 | 機能          | 信号名       | FPGA<br>ピン<br>番号 | 機能                  |

|-------------|------------------|-------------|-----------|------------------|---------------------|

| LED_N0      | H19              | LED8~0      | DIPS W0   | P12              | User DIP SW         |

| LED_N1      | G20              |             | DIPS W1   | T12              |                     |

| LED_N2      | H20              |             | DIPS W2   | U9               |                     |

| LED_N3      | J20              |             | DIPS W3   | V9               |                     |

| LED_N4      | J21              |             | LCD_DATA0 | H7               | キャラクタLCD            |

| LED_N5      | K21              |             | LCD_DATA1 | H8               |                     |

| LED_N6      | M22              |             | LCD_DATA2 | H9               |                     |

| LED_N7      | M21              |             | LCD_DATA3 | G6               |                     |

| SEVEN_SEG0  | AD7              | SEVEN SEG 0 | LCD_DATA4 | G7               | User Push<br>Button |

| SEVEN_SEG1  | AD6              |             | LCD_DATA5 | F6               |                     |

| SEVEN_SEG2  | AB6              |             | LCD_DATA6 | F7               |                     |

| SEVEN_SEG3  | AA7              |             | LCD_DATA7 | E6               |                     |

| SEVEN_SEG4  | AA6              |             | LCD_E     | J8               |                     |

| SEVEN_SEG5  | Y9               |             | LCD_RS    | J7               |                     |

| SEVEN_SEG6  | Y8               |             | LCD_RW    | K9               |                     |

| SEVEN_SEG7  | W8               |             | PUSHSW_N0 | AB24             |                     |

| SEVEN_SEG8  | V8               |             | PUSHSW_N1 | W20              |                     |

| SEVEN_SEG9  | U7               |             | PUSHSW_N2 | AC13             |                     |

| SEVEN_SEG10 | T8               |             | PUSHSW_N3 | V12              |                     |

| SEVEN_SEG11 | T7               |             | UART_RXD  | L7               | UART                |

| SEVEN_SEG12 | R10              |             | UART_TXD  | K6               |                     |

| SEVEN_SEG13 | R9               |             |           |                  |                     |

| SEVEN_SEG14 | R8               |             |           |                  |                     |

| SEVEN_SEG15 | P8               |             |           |                  |                     |

表 11. 各種入力インターフェースピン配置リスト

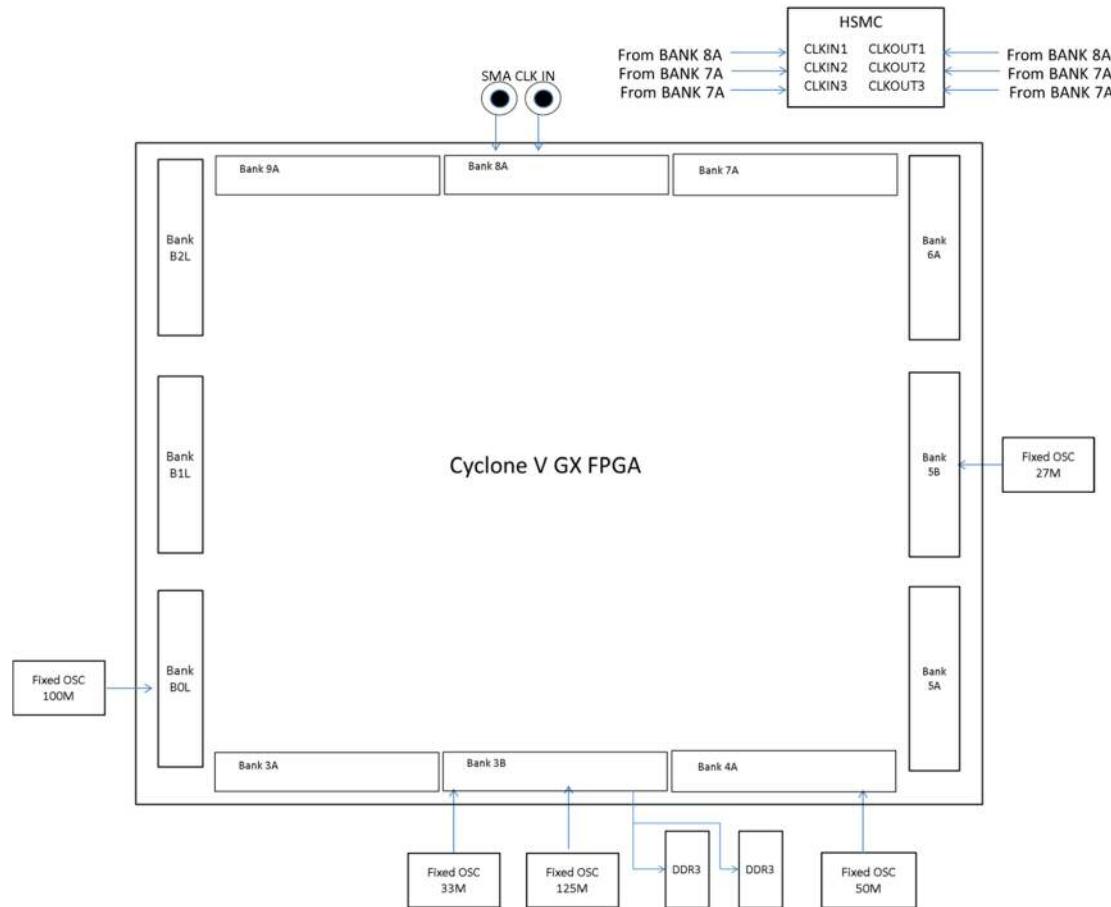

## 5.12 クロック回路

このセクションでは、当ボードに搭載されているクロック回路について解説します。

### 5.12.1 ボード搭載オシレータ

当ボードには、FPGA の回路で使用可能なクロックとして 25-MHz, 50-MHz, 125-MHz をご用意しています。当ボードへのクロック入力に関しては、表 11 をご確認ください。

表 11. クロック入力系統図

表 12 に当ボードに搭載されているクロックリソースの周波数、I/O スタンダード、およびピン番号を示します。

表 12. オンボード・クロックリソース

| 部品番号 | 回路図の信号名     | 周波数     | I/O スタンダード | Cyclone V<br>ピン番号 | 用途             |

|------|-------------|---------|------------|-------------------|----------------|

| U7   | CLK27M      | 27 MHz  | 3.3V       | T21               | ユーザ・ロジック       |

| U8   | CLK33M      | 33 MHz  | 1.8V       | T13               | ユーザ・ロジック       |

| U10  | CLK50M      | 50 MHz  | 1.8        | U12               | ユーザ・ロジック       |

| U11  | CLK125M     | 125 MHz | 1.8V       | P11               | ユーザ・ロジック       |

| U3   | DIFF0_P     | 100 MHz | LVDS       | V6                | トランシーバ・リファレンス  |

|      | DIFF0_N     | 100 MHz | LVDS       | W6                | トランシーバ・リファレンス  |

| U18  | TSE_MAC_CLK | 25 MHz  | 3.3V       | N20               | イーサネット PHY     |

|      | TSE_RX_CLK  | 25 MHz  | 3.3V       | R20               | イーサネット PHY     |

| U22  | EZ_CLK      | 48 MHz  | 3.3V       | K25               | USB 2.0 コントローラ |

## 5.12.2 外部入力・出力クロック

当ボードは、外部からの入力クロックを HSMC または SMA を介して入力することができます。 表 13 に外部入力クロックの一覧を示します。

表 13. 外部入力クロック

| 部品   | 回路図の信号名        | I/O スタンダード | Cyclone V<br>ピン番号 | 詳細                                                       |

|------|----------------|------------|-------------------|----------------------------------------------------------|

| HSMC | HSMC_1_CLKIN   | 2.5V       | L8                | HSMC ケーブルまたはデータカードからのシングルエンの入力.                          |

| HSMC | HSMC_2_CLKIN_P | LVDS/ 2.5V | H12               | HSMC ケーブルまたはデータカードからの LVDS 入力. 2 x 2.5V のデータ入力ピンとして使用可能. |

|      | HSMC_2_CLKIN_N | LVDS/ 2.5V | G11               |                                                          |

| HSMC | HSMC_3_CLKIN_P | LVDS/ 2.5V | G15               | HSMC ケーブルまたはデータカードからの LVDS 入力. 2 x 2.5V のデータ入力ピンとして使用可能. |

|      | HSMC_3_CLKIN_N | LVDS/ 2.5V | G14               |                                                          |

| SMA  | SMA_CLKIN      | 2.5V       | N9                | SMA コネクタ                                                 |

表 14 に当ボードの外部出力クロックを示します。.

表 14. 外部出力クロック

| 部品   | 回路図の信号名         | I/O スタンダード | Cyclone V<br>ピン番号 | 詳細                                                       |

|------|-----------------|------------|-------------------|----------------------------------------------------------|

| HSMC | HSMC_1_CLKOUT   | 2.5V       | A7                | FPGA 2.5V 出力(または GPIO)                                   |

| HSMC | HSMC_2_CLKOUT_P | LVDS/ 2.5V | B15               | HSMC ケーブルまたはデータカードからの LVDS 出力. 2 x 2.5V のデータ出力ピンとして使用可能。 |

|      | HSMC_2_CLKOUT_N | LVDS/ 2.5V | C15               |                                                          |

| HSMC | HSMC_3_CLKOUT_P | LVDS/ 2.5V | A23               | HSMC ケーブルまたはデータカードからの LVDS 出力. 2 x 2.5V のデータ出力ピンとして使用可能。 |

|      | HSMC_3_CLKOUT_N | LVDS/ 2.5V | A22               |                                                          |

| SMA  | SMA_CLKOUT      | 2.5V       | M9                | SMA コネクタ                                                 |

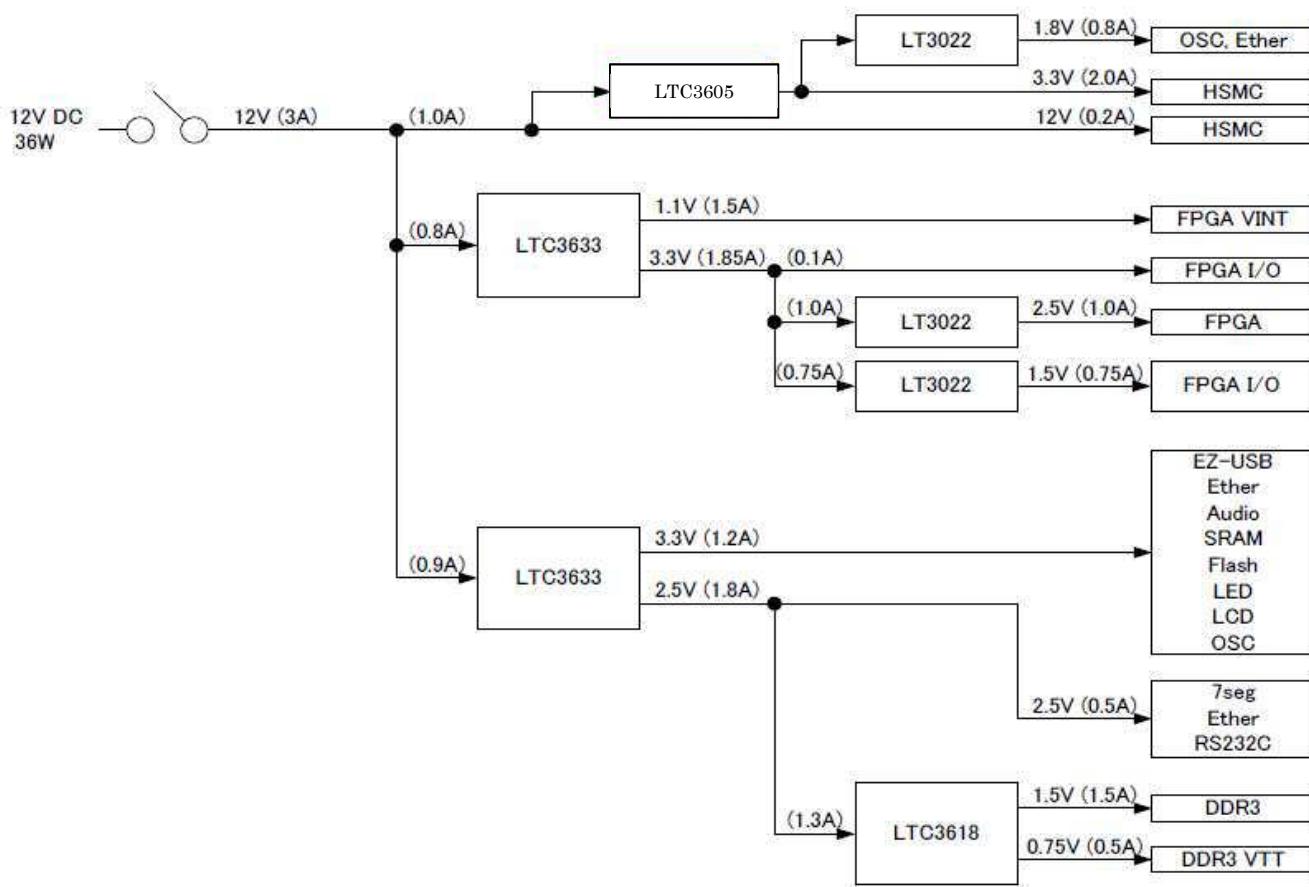

## 5.13 電源ツリー

当ボードでは、電源デバイスとしてリニアテクノロジー社の電源デバイスを使用しています。図 12 に当ボードの電源ツリー図を示します。

図 12. Beryll 電源ツリー

# 6. 使用上の注意事項

## 6.1 未使用ピンのモード選択

ハードウェア・デザイン上で使用されていないピン(未使用ピン) の処理を行います。当ボードを使用する場合は、未使用ピンをトライステート・モードに設定しておく必要があります。以下に Quartus II 開発ソフトウェアにおける未使用ピンの設定方法を示します。

1. Assignments メニュー > Device を選択します。

2. [Device & Pin Options] ボタンをクリックします。

Device & Pin Options ウィンドウが表示されます。

3. Unused Pins タブを選択します。

4. Reserve all unused pins 項目で As input tri-stated を選択します。

5. [OK] ボタンをクリックします。

6. [OK] ボタンをクリックし、Device & Pin Options ウィンドウを閉じます。

## 7. 改定履歴

| 日付        | 版   | 更新概要 |

|-----------|-----|------|

| 2014年2月1日 | 0.1 | • 初版 |

|           |     | •    |

|           |     | •    |

### 免責、及び、ご利用上の注意

弊社より資料を入手されましたお客様におかれましては、下記の使用上の注意を一読いただいた上でご使用ください。

1. 本資料は非売品です。許可無く転売することや無断複製することを禁じます。

2. 本資料は予告なく変更することがあります。

3. 本資料の作成には万全を期していますが、万一ご不明な点や誤り、記載漏れなどお気づきの点がありましたら、下記までご一報いただければ幸いです。

株式会社マクニカ

戦略技術本部 Mpression 推進部

〒222-8561 横浜市港北区新横浜 1-6-3 HP: <http://www.m-pression.com>

4. 本資料で取り扱っている回路、技術、プログラムに関して運用した結果の影響については、責任を負いかねますのであらかじめご了承ください。

5. 製品をご使用になる場合は、各デバイス・メーカーの最新資料もあわせてご利用ください。