## **Getting Started**

## **Mpression Beryll Board**

Revision 1.0

2014 / 2

# 目次

| 1. 安全上の注意                     | 3  |

|-------------------------------|----|

| 1.1 凡例                        | 3  |

| 1.2 注意事項                      | 3  |

| 1.3 製造元情報                     | 5  |

| 2. 重要事項                       | 6  |

| 3. 事前準備                       | 7  |

| 3.1 当マニュアルについて                | 7  |

| 3.2 事前準備                      | 7  |

| 4.ボードセットアップとデザインの実行           | 9  |

| 4.1 Beryll ボード仕様              | 9  |

| 4.1.1 Beryll スイッチ / コネクタレイアウト | 9  |

| 4.1.2 Beryll 部品レイアウト          | 10 |

| 4.1.3 Beryll スイッチ / LED レイアウト | 10 |

| 4.2 FPGA サンプル・デザインの実行         | 11 |

| 4.2.1 サンプル・デザインのブロック・ダイヤグラム   | 11 |

| 4.2.2 デザインの実行                 | 12 |

| 4.3 ソフトウェアプロジェクトの作成と実行        | 14 |

| 4.3.1 ソフトウェアプロジェクトの作成         | 14 |

| 4.3.2 ソフトウェアプロジェクトのビルド        | 17 |

| 4.3.3 ターゲットボードでのソフトウェアの実行     | 20 |

| 4.3.4 ソフトウェアのデバッグ             | 22 |

| 5.更新履歴                        | 24 |

## 1. 安全上の注意

ここに示した注意事項は、お使いになる人や、他の人への危害、財産への損害を未然に防ぐための内容を記載していますので、必ずお守りください。

## 1.1 凡例

| <b>企</b> 危険 | この表示は、取り扱いを誤った場合、「死亡また重傷を負う危険が切迫して生じることが<br>想定される」内容です。    |

|-------------|------------------------------------------------------------|

| 警告          | この表示は、取り扱いを誤った場合、「死亡または重傷を負う可能性が想定される」内<br>容です。            |

| 注意          | この表示は、取り扱いを誤った場合、「傷害を負う可能性が想定される場合および物的損害のみの発生が想定される」内容です。 |

## 1.2 注意事項

| <u> </u> | 危険                                                                                                        | 本マニュアルで指定された仕様に基づく AC アダプタ (梱包品) を使用してください。<br>指定の仕様を満たさない AC アダプタを使用した場合は、キットの発熱、破裂、発火の<br>原因となります。 |

|----------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| 警告       | 強い衝撃を与えたり、投げつけたりしないでください。<br>発熱、破裂、発火や機器の故障、火災の原因となります。                                                   |                                                                                                      |

|          | 電子レンジなどの加熱調理機器や高圧容器に、本体や AC アダプタを入れないでください。本体や AC アダプタの発熱、破裂、発火、発煙、部品の破壊、変更などの原因となります。                    |                                                                                                      |

|          | 使用中の本体を布など熱のこもりやすいもので包んだりしないでください。<br>熱がこもり、発火、故障の原因となることがあります。                                           |                                                                                                      |

|          | 本体を廃棄する時は、他の一般ゴミと一緒に捨てないで下さい。<br>火中に投じると破裂する恐れがあります。廃棄方法については、廃棄物に関する各種法律・法令・条例等に従ってください。                 |                                                                                                      |

|          | 極端な高温、低温、また温度変化の激しい場所で使用しないで下さい。<br>故障の原因となります。周囲温度は 5℃ ~ 35℃、湿度は 0% ~ 85% の範囲でご<br>使用ください。               |                                                                                                      |

|          | 電源コードを強く引っ張ったり、重いものを乗せたりしないでください。<br>電源コードを傷つけたり、破損したり、束ねたり、加工したりしないでください。<br>傷ついた部分から漏電して、火災・感電の原因になります。 |                                                                                                      |

|          | 濡れた手で電源プラグを抜き差ししないでください。<br>感電による怪我や故障の原因になります。                                                           |                                                                                                      |

|          | 電源プラグはコンセントの奥までしっかりと差し込んでください。<br>しっかり差し込まないと、感電や発電による火災の原因となります。                                         |                                                                                                      |

|          |                                                                                                           | タコ配線を行ったり、AC アダプタの規格電圧以外の電源に接続したりしないでください。<br>故障や感電、発熱による火災の原因なります。                                  |

### 警告

(前頃から継続)

電源プラグのほこりを定期的に拭き取り、コンセント周辺のたまったほこりを取り除いてください。

ほこりがたまったままで使用していると湿気などで、絶縁不良となり、火災の原因になります。

電源プラグやコンセプト周辺のほこりは、乾いた布で拭き取ってください。

本ボードにコップや花瓶など、水や液体が入った容器を置かないでください。

本ボードに水や液体が入ると、故障や感電の原因になります。水などをこぼした場合は、使用を中止し、電源を切って電源プラグを抜いてください。修理や技術的な相談はアルティマへお問い合わせください。

ぐらついた台の上や傾いた場所等、不安定な場所には置かないでください。 落下して、けがや故障の原因になります。

直射日光の強い場所や炎天下の車内など高温の場所で使用、放置しないでください。 発熱、破損、発火、暴走、変形、故障の原因になります。また、機器の一部が熱くなり、火 傷の原因となる場合もあります。

本体を組み込んだ装置の保守中は、電源を抜いて作業してください。

感電の危険性があります。

ボードに無理な力がかかるような場所に置かないでください。

基板の変形により、基板の破損、部品の脱落、故障の原因となります。

拡張ボードや他の周辺機器と一緒にお使いの場合には、それぞれ個別の取り扱い説明書をよく読んで適正にお使いください。

本マニュアルに記載されているもの、また別途動作を確認できていることを公表しているものの他は、特定の拡張ボードや周辺機器の相互動作は保証いたしかねます。

本ボードを移動・接続するときは、電源スイッチを切ってください。

電源をいれたまま移動・接続すると、故障や感電の原因になります。

#### 注意

ベンジンやシンナーなど化学薬品を含んだ雑巾で手入れしないでください。

本ボードが変質する可能性があります。科学雑巾を使用するときは、その注意書きに従ってください。

本ボードを箱から取り出した際、機器本体に結露が発生した場合は、すぐに電源を入れないでください。

本ボードを箱から取り出す際、冷えたボード本体が部屋の暖かい空気により結露が発生することがあります。

結露があるまま電源を入れると、本ボードが破損したり、部品の寿命が短くなる場合があります。

本ボードを取り出したら室温になじませてください。結露が発生した場合は、水滴が蒸発してから設置や接続を行ってください。

カスタマイズ可能と明示している部分以外の分解、解体、改変、改造、再生はしないでください。

本キットはカスタマイズが可能なキットですが、本マニュアルに指定された部分 以外は基本動作に必要な部分に何らか外部の手が加わることで製品全体の動 作保証が出来なくなります。本マニュアルに記載されているカスタマイズ可能部 分以外のカスタマイズをご希望の場合には、はじめに必ずアルティマにご相談く ださい。

## 1.3 開発元

株式会社アルティマ 〒222-8563 横浜市港北区新横浜 1-5-5 http://www.altima.co.jp

## 1.4 お問い合わせ先

ご購入頂いた販売代理店、もしくは下記 Web のお問い合わせフォームよりお問い合わせ下さい。

Mpression ブランド Web サイト内 お問い合わせページ:

http://www.m-pression.com/ja/contact

## 2. 重要事項

#### 最初にお読みください:

- 当製品のご使用前に必ず当Getting Started をお読みください

- 当Getting Started は、お手元にお持ちください

- ・ ボードの構成を十分にご理解頂いた上でボードをご使用ください

#### 当製品の用途:

・ 当製品は、アルテラ社のCyclone® V GX FPGA を使用するシステムの検証用ボードとしての使用を想定しております。当ボードをご使用頂く事で、ソフトウェア、ハードウェアの検証を行って頂く事が可能です。

#### 当製品をご使用されると想定するお客様:

・ 当製品は、ユーザーマニュアルおよびGetting Started を精読し、開発ボード及びFPGA の取扱いに熟知された方の使用を想定しております。当製品を使用するには、FPGA、ロジック回路、および電子回路への基本的な知識を必要といたします。

#### 当製品を使用頂く際の注意事項:

- ・ 当製品は、お客様のプログラム開発および評価段階で使用するための評価用ボードとなります。 お客様の設計されたプログラムの量産時においては、当ボードをお客様の装置に組込んで使用することは できません。また、開発済の回路については、必ず統合試験、評価、または実験などにより実使用の可否を ご確認ください。

- ・ 当製品の使用から生ずる一切の結果について、株式会社アルティマ(以降アルティマ)は責任を持ちません。

- ・アルティマは、潜在的に内包されるすべての危険性を評価予期しているわけではありません。したがって 当ボードやGetting Started 内の警告や注意は、すべての警告や注意を含んでいるわけではありません。 それゆえ、当製品をご使用の際は、ユーザ様ご自身で製品を安全にご利用頂く必要があります。

- すべてのUSB メモリやSD カード、および消耗品は保証外となります。

- LAN インタフェース接続用機器の接続コネクションについては、保証外となります。

- ・ 製品の改造又は、お客様による製品の損傷時は、交換対応ができません。

- 当製品は、鉛フリー製品を使用した製品です。

- ・ 当マニュアルに記載のあるいずれのベンダの商標および登録済み商標の権利は、各ベンダに帰属します。

#### 製品改善のポリシー:

・ アルティマは、製品のデザイン、パフォーマンスおよび安全性に関して製品を常に改善し続けます。 アルティマは、お客様に予告なく、いつでも製品のドキュメント、リファレンス・マニュアル、デザインおよび 一部およびすべての仕様を変更する権利を保有します。

#### 製品の RMA について :

- ・ 製品の納品後、30日以内の初期不良に関しましては無償交換にて対応させて頂きます 但し、以下の場合は無償交換の対応ができませんのでご了承ください。

- (1) 製品の誤使用または、通常使用環境ではない状況での製品の損傷

- (2) 製品の改造または補修

- (3) 火災、地震、製品の落下やその他アクシデントによる損傷

#### 図および写真:

・ 図や写真は、お手元にある実際の製品とは異なる可能性がございます。

## 3. 事前準備

### 3.1 当マニュアルについて

当マニュアルでは、Beryll ボードを使用いただく際のボードセットアップ、サンプル・デザインの実行およびソフトウェアプロジェクトの設計フローをご紹介いたします。当マニュアルをお読みいただく事で次の内容をご理解頂くことができます。:

- 基本的な Beryll ボードの仕様の理解

- FPGA 開発の際に必要なソフトウェアのインストール

- Beryll ボードのセットアップ

- サンプル・デザインの実行

- ソフトウェアプロジェクトのビルドおよびデバッグフロー

### 3.2 事前準備

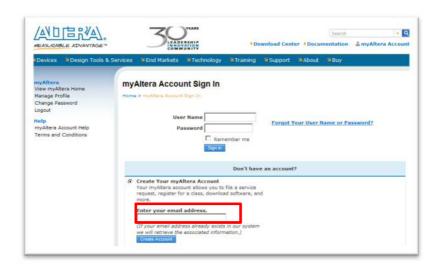

Beryll ボードを使用する前に、FPGA 開発の際に必要となる以下のソフトウェアをダウンロードし、対象の PC にインストールしてください。なお、アルテラ社ソフトウェアをダウンロードするには、アルテラ社 myAltera アカウントを取得する必要があります。myAltera アカウントは、ソフトウェアをダウンロードする前に必ずご登録を完了させるようお願いいたします。

#### A. アルテラ社 myAltera アカウントの取得

アルテラ社 myAltera アカウントを取得するためには、次の URL より必要情報を記入の上、アカウントを取得してください。

- myAltera 登録用 URL <u>https://www.altera.com/myaltera/mal-signin.jsp</u>

- myAltera に初めて登録される方は、URL の下部 "Create Your myAltera Account" にチェックをし "Enter Your email address " に登録をするユーザの E-mail アドレスを入力してください。

#### B. Quartus® II ウェブ・エディション・ソフトウェア

Quartus II ウェブ・エディション・ソフトウェアは、アルテラのライセンス・フリーソフトウェアです。当ソフトウェアは、サブスクリプション・エディションに比べ、一部機能に使用制限があります。Quartus II ウェブ・エディション・ソフトウェアは、Quartus II ウェブ・エディション・ソフトウェアページよりダウンロード可能です。

Quartus II ウェブ・エディション・ソフトウェア と サブスクリプション・エディションの違いについては以下 URL をご参照ください。

- Quartus II ウェブ・エディション・ソフトウェアページ <a href="http://dl.altera.com/?edition=web">http://dl.altera.com/?edition=web</a>

- Quartus II サブスクリプション・エディション vs ウェブ・エディション・ソフトウェアの機能比較 http://www.altera.com/literature/po/ss quartussevswe.pdf

### C. On-Board USB-Blaster <sup>™</sup> ドライバのインストール

Beryll ボードは、On-Board USB-Blaster 回路をサポートしています。Beryll ボードへの FPGA プログラミング・ファイルの書込みや OpenCore® を使用しての IP コアの評価において、On-Board USB-Blaster 経由で評価を実施していただくことが可能です。On-Board USB-Blaster のドライバのインストールは、Altera Programming Cable Driver Information ページ よりダウンロードしてください。

Altera Programming Cable Driver Information ページ http://www.altera.com/download/drivers/dri-index.html

## 4. ボードセットアップとデザインの実行

## 4.1 Beryll ボード仕様

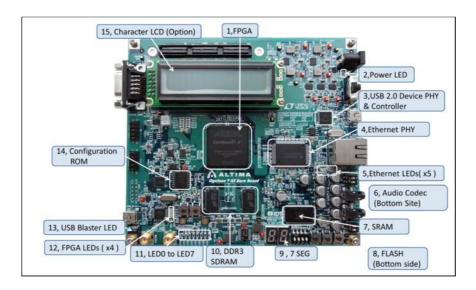

この項では、当ボードのスイッチ・コネクタおよび部品のレイアウトに関して解説します。

### 4.1.1 Beryll スイッチ / コネクタ レイアウト

図 1 に当ボードのスイッチ / コネクタ のレイアウトを示します。

図1 Beryll スイッチ / コネクタレイアウト

- 1 HSMC

- 2 DC ジャック

- 3 電源スイッチ

- 4 USB2.0 ミニ-B コネクタ

- 5 イーサネットコネクタ RJ45

- 6 イーサネット DIP スイッチ

- 7 オーディオライン入力/出力

- 8 オーディオ DIP スイッチ

- 9 汎用プッシュスイッチ

- 10 汎用 DIP スイッチ

- 11 SMA コネクタ

- 12 リセット用プッシュスイッチ

- 13 FPGA リコンフィギュレーション用プッシュスイッチ

- 14 USB ブラスターコネクタ

- 15 FPGA 用 JTAG コネクタ (未搭載)

- 16 RS232C コネクタ

## 4.1.2 Beryll 部品 レイアウト

図2に当ボードの主な部品レイアウトを示します。

図 2 Beryll コンポーネント・レイアウト

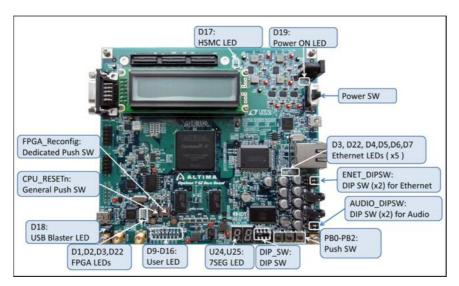

### 4.1.3 Beryll スイッチ / LED レイアウト及び仕様

図3 に当ボードのスイッチ / LED レイアウトを示します。

図3 Beryll スイッチ / LED レイアウト

表 1 に各 LED の機能を、表 2 に各スイッチの機能を示します。

表 1 LED 仕様

| 部品位置     | 機能                          |

|----------|-----------------------------|

| D1       | FPGA CONF_DONE チェック用 LED    |

| D2       | FPGA nSTATUS チェック用 LED      |

| D3       | FPGA nCONFIG チェック用 LED      |

| D4       | ACT:通信時の確認用LED              |

| D5       | LK10:10Mbps 通信時のリンク確認用LED   |

| D6       | LK100:100Mbps 通信時のリンク確認用LED |

| D7       | LK1000:1Gbps 通信時のリンク確認用LED  |

| D8       | DUPLEX:全二重通信時の確認用LED        |

| D9-D16   | 汎用 LED x8                   |

| D17      | HSMC ドータボード実装時LED           |

| D18      | USB-Blasterケーブル接続確認         |

| D19      | +12V B14 電源 LED             |

| D22      | FPGA INIT_DONE 確認用のLED      |

| U24, U25 | 汎用7セグメントLED x2              |

表 2 スイッチ仕様

| 部品ロケーション                | 初期値      | 機能                                   |

|-------------------------|----------|--------------------------------------|

| POWER_SW                | 下スライド    | 下スライド:電源OFF, 上スライド:電源ON              |

|                         |          | CRS/RGMII_SEL0                       |

|                         |          | Open: RGMII - 3COM                   |

|                         |          | Short : RGMII - HP                   |

| ENET_DIPSW              | 2つともOPEN | COL/CLK_MAC_FREQ                     |

|                         |          | Open: 125MHz output                  |

|                         |          | Short: 25MHz output                  |

|                         |          | 二つともOpenでお使いください                     |

|                         |          | AUDIO_MP2                            |

|                         |          | Open: StaticPin Low or FPGA Control  |

|                         |          | Short : StaticPin and Mid Voltage    |

| AUDIO_DIPSW             | 2つともOPEN |                                      |

|                         |          | AUDIO_MP4                            |

|                         |          | Open: StaticPin High or FPGA Control |

|                         |          | Short : StaticPin and Mid Voltage    |

| DIP_SW                  | なし       | 汎用ディップスイッチ ( x 4 )                   |

| CPU_RESETn, PB0,PB1,PB2 | なし       | 汎用プッシュSW                             |

| FPGA_Reconfig           | なし       | FPGAのリコンフィグレーションプッシュSW               |

## 4.2 FPGA サンプル・デザインの実行

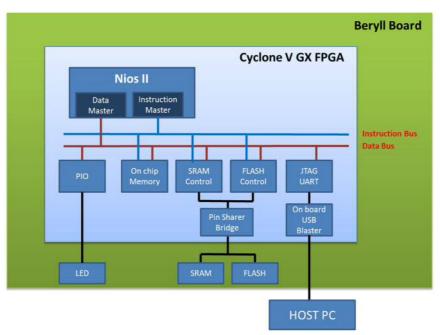

この項では、当ボードにサンプル・デザインである Beryll\_Factory\_Design を書き込み、DDR3, SRAM, FLASH をテストします。 Beryll\_Factory\_Design は、Nios $^{\circ}$ ll をデザインに組み込み、デザインを実行した際に各メモリにリード/ライトが正常に行えるかを LED の点灯により判定する構成となっています。

### 4.2.1 サンプル・デザインのブロック・ダイヤグラム

図 4 にサンプル・デザインのブロック・ダイヤグラムおよびハードウェアの構成を示します

図 4. サンプル・デザインブロック・ダイヤグラム

| ブロック図上の名称         | 機能                               |

|-------------------|----------------------------------|

| NIOS II           | Nios II コア                       |

| On chip memory    | 64k Byte Cyclone V FPGA オンチップメモリ |

| SRAM Control      | SRAM 用 汎用トライステート・コントローラ          |

| FLASH Control     | FLASH 用 汎用トライステート・コントローラ         |

| Pin sharer Bridge | トライステート・ピンシェアラ                   |

| JTAG UART         | JTAG                             |

| DDR Controller    | DDR3 SDRAM コントローラ                |

### 4.2.2 デザインの実行

次に、以下のフローを実施しサンプル・デザインを実行してください

#### A. サンプル・デザインを PC に保存

サンプル・デザインのプロジェクトフォルダ "Beryll\_Factory\_Design" を任意の作業フォルダにコピーします。 当マニュアルでは、例として作業フォルダ D: ¥work を使用します

#### B. Quartus II プロジェクトファイルを開く

ダウンロードした d:\footnotesign January の Beryll\_Factory\_Design.qpf をダブルクリックして Quartus II プロジェクトを開きます。

次にQuartus II の起動後右上のEntity 枠のプロジェクト 名(TOP)をダブルクリックしてVerilog ファイルを開きます。

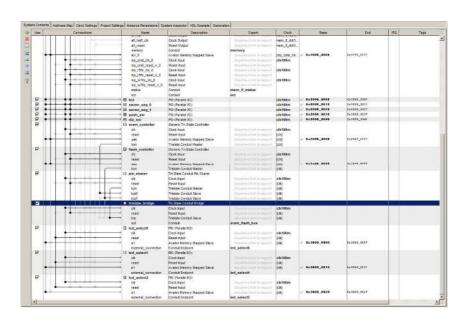

C. Quartus II Tools メニュー>Qsys をクリックして、Qsys を開き、システムの構成を確認します。

このサンプル・デザインには、メモリデバイスとしてオンチップメモリ、DDR-SDRAM、SRAM、NOR-FLASH が搭載されております、しかしこのデザインでは DDR-SDRAM、SRAM、NOR-FLASH の各メモリに対して、ライト後、リードプログラムを実行しておりますので、プログラムはオンチップメモリに置いてください。図 5 に Qsys にプログラムが反映されたイメージを示します。

図 5. Qsys にサンプル・デザインが正しく反映された場合

#### D. FPGA にプログラム・ファイルをダウンロードする

当ボードには、On-Board USB-Blaster が実装されています。On-Board USB-Blaster を使用することで、USB-Blaster ケーブルを使うことなくFPGA の回路を当ボードにダウンロードすることが可能です。On-Board USB-Blaster の USB コネクタ位置は図 1 の 14 USB Blaster を参照してください。

- a. 当ボードの電源を切った状態で USB ケーブルを PC と当ボードの USB-Blaster 用ミニコネクタに接続します(USB-Blaster 用ミニコネクタの位置は図 1 を参照して下さい)

- b. Quartus II プログラマを起動しますプログラマが起動したら、Beryll\_Factory\_Design\_TOP.sof が選択されているかを確認してください。

- c. 選択されていない場合は、"Auto Detect " ボタンを押しJTAG に接続されている FPGA を認識させた後に右クリックをして " Change File" を選択してください。

- d. 同時に Hardware Setup に USB-Blaster が選択されていることおよび Program/Configure のチェックボックスにチェックが入っていることを確認してください。

- e. Start ボタンをクリックして、プログラミングを開始します。右上の Progress の欄が 100%になったら プログラム終了です。

この sof ファイルにはオンチップメモリの初期化ファイルが含まれており、その初期化ファイルに Nios II のプログラムコードも含まれています。よって sof ファイルのダウンロードが終了後、このプログラムが自動的に実行されます。このソフトウェアは、ボードの簡易チェックをするものになっており、DDR-SDRAM, SRAM, NOR-FLASH のライト/リードテストを行います。

DDR-SDRAM のテスト結果 LED0 点灯:テストパス 点滅:テストフェイル SRAM のテスト結果 LED1 点灯:テストパス 点滅:テストフェイル

NOR-FLASH のテスト結果 LED2 点灯:テストパス 点滅:テストフェイル

- LED 4 LED 7 は図 1 10 汎用 DIP スイッチに連動して ON / OFF します。

- 2 ケタの7セグメント LED が 0-F でインクリメント繰り返します。

上記の3項目のテストが問題なく実施できたら、当回路が正常に動作したことになります

### 4.3 ソフトウェアプロジェクトの作成と実行

この項では、Nios II エンベデッド・デザイン・スイート(Nios II EDS) を使用してソフトウェアプロジェクトの作成からデバッグまでの一連のフローをご紹介します。

### 4.3.1 ソフトウェアプロジェクトの作成

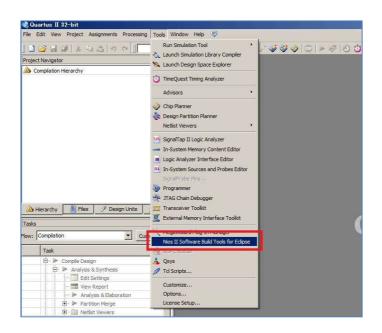

A. Quartus II の tools メニューより "Nios II Software Build tools for Eclipse " を起動します。

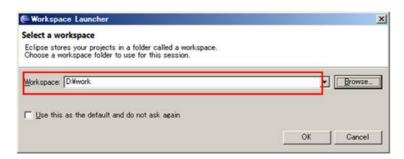

B. Nios II ソフトウェア・ビルド・ツール(Nios II SBT) の作業フォルダを決定します。任意のフォルダを指定することができますが、ここでは Quartus II のプロジェクトのフォルダを指定します。

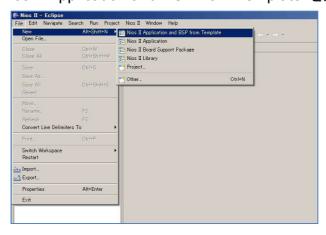

C. Nios II SBT を用いてソフトウェアプロジェクトを作成します。下図のように File > New > "Nios II Application and BSP from Template"を選択します。

D. 下図の Nios II Application and BSP from Template ダイアログボックスが開きます。このダイアログボックスで赤枠 "SOPC Information File Name" に Qsys が生成した\*.sopcinfo を選択します。このファイルにはハードウェアの情報が入っています。次に Project Name にプロジェクト名を入力し、Project template となる template を選択します。(ここでは Hello World Small)を選択しています。

E. Next を押して次のページに進みます。ここで"Create a new BSP project based on the application template"が選択されていることを確認して"Finish"を選択します。

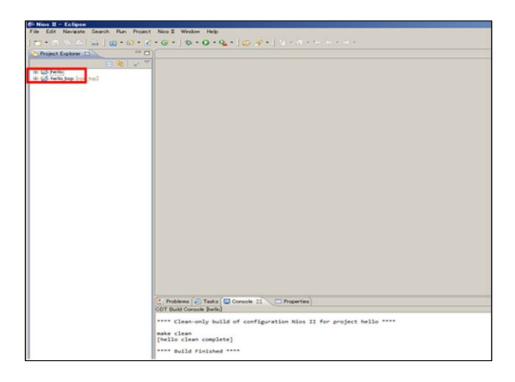

F. 下図のように左側のペインに"Hello"と"Hello bsp"というプロジェクトが二つできていることを確認してください。

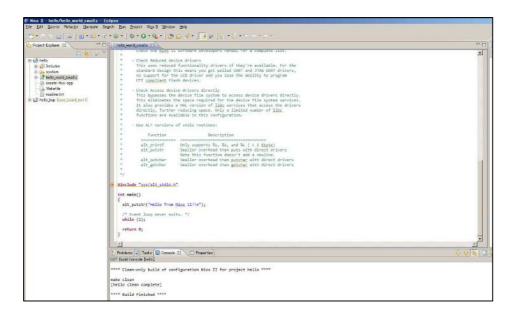

G. 下図のように"Hello"プロジェクトの中の"hello\_world\_small.c"を開いて中身を確認してください。これをテンプレートとしてプログラムを拡張できます。後程ソースを追加しますが、今はこのままこのソースを使用してみます。

### 4.3.2 ソフトウェアプロジェクトのビルド

次に Nios II SBT を使用して作成したソフトウェアプロジェクトをビルドします。

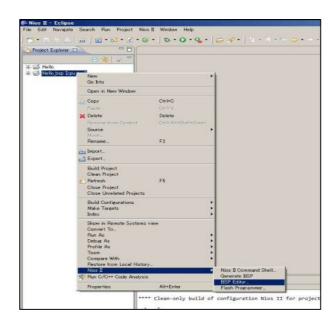

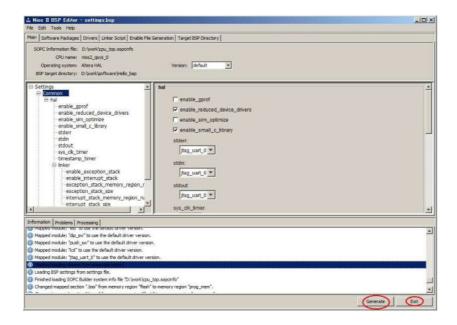

A. 下図のように"Hello\_Bsp"を左クリックして Nios II メニューの中の"BSP Editor"サブメニューを選択します。

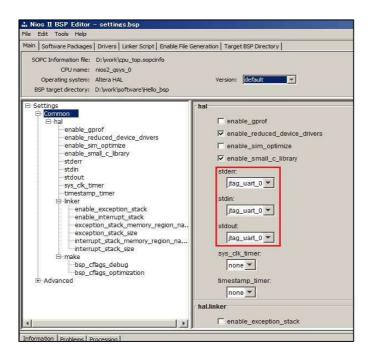

B. BSP Editor が起動したら、Main タブを選択して、以下の様に stderr, stdin, stdout に jtag\_uart が選択されていることを確認してください。

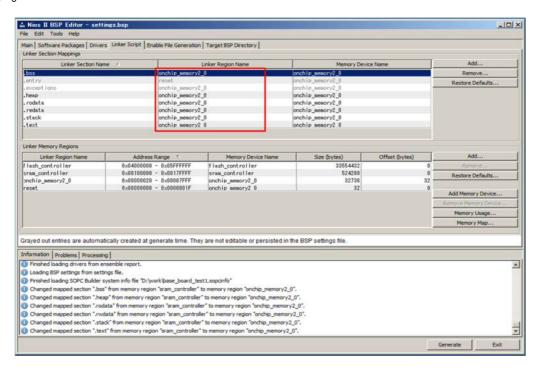

C. Linker Script タブを選択し、全てのメモリセクションでオンチップメモリを選択してください。

D. "Generate" ボタンを押してコードを生成した後に、"Exit" ボタンを押し BSP editor を終了します。

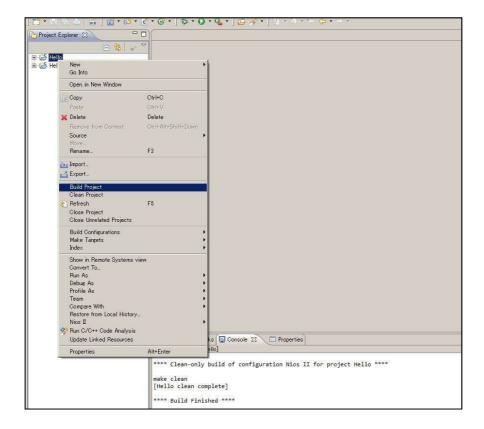

E. BSP Editor を終了したら Nios II SBT の Project Explorer 内の"Hello"プロジェクトを 左クリックし下図のように"Build Project"を選択してください。

### 4.3.3 ターゲットボードでのソフトウェアの実行

次にターゲットボードにビルドしたソフトウェアプログラムをダウンロードし、実行します。

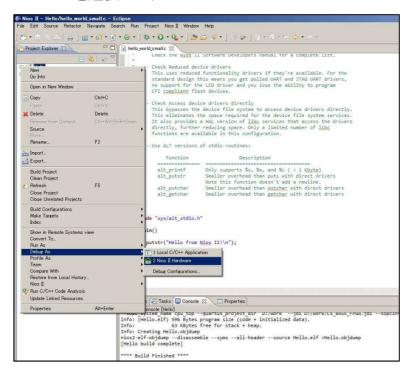

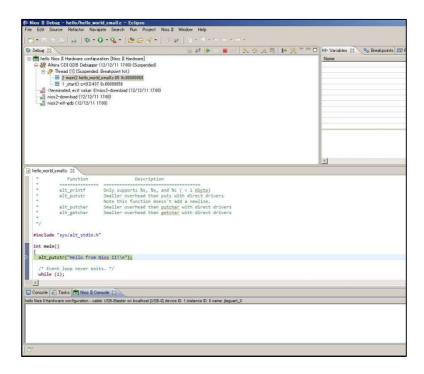

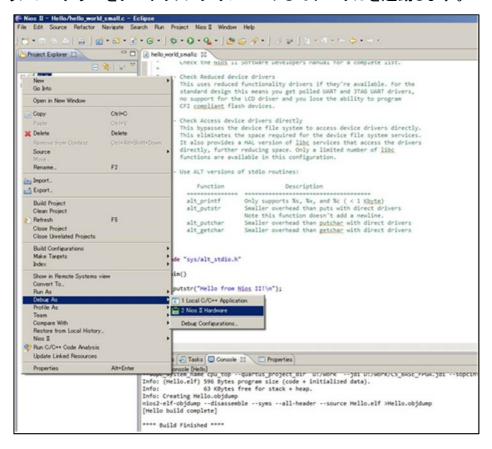

A. NIOS II SBT で"Hello" プロジェクトを右クリックし、"Debug As…" メニューの中の "Nios II Hardware" を選択します

B. ターゲットボードにダウンロードが完了し、下図のようにメイン関数の先頭で止まれば ターゲットでのプログラムの起動は正常にできていることになります。

C. 以下の赤枠で囲ったソースコードを既存の main 関数に追加してください。この中の

"IOWR\_ALTERA\_AVALON\_PIO\_DATA(ADRESS)"関数はキャッシュを通さずに

PIO ハードウェアにアクセスするためのマクロです。与えられたアドレスの PIO の設定を

変更します。

- D. ここでソースコードを書き換えたら"4.2.5"の手順に従ってもう一度プログラムをビルドし、その後"4.3.1"の手順に従ってターゲットにダウンロードして下さい。

- E. ダウンロード後、赤丸で囲ったツールバーのデバッガのステップを行い、

"alt\_putstr"を step over で実行、"Nios II console" にメッセージが表示されることを

確認して下さい。続いて while ループの中をステップ実行して、LED が点滅することを

確認して下さい。

```

| Price | State | Section | Price | Section | Section

```

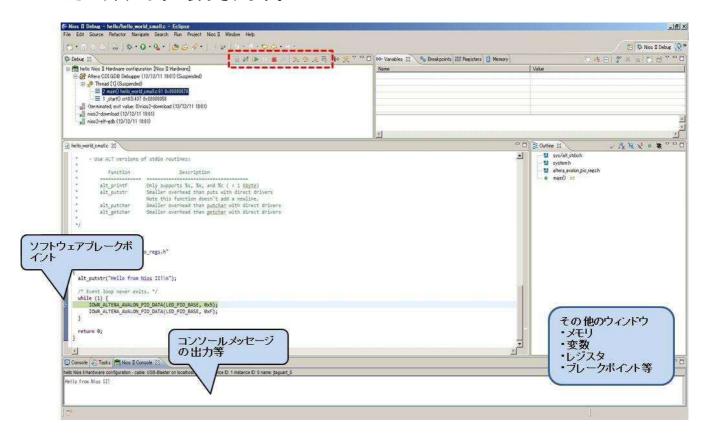

### 4.3.4 ソフトウェアのデバッグ

最後にソフトウェアのデバッグについて簡単に解説します。

A. 下図のようにプログラムをターゲットにダウンロードしてデバッガを起動します。

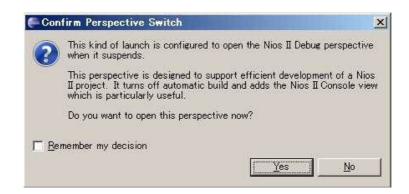

B. 下図のようにデバッガ画面に切り替えますが、というメッセージウィンドウが表示されるので、Yes をクリックします。

C. デバッガ画面に切り替わりましたので、ここでステップ実行やソフトウェア・ブレークポイント等の操作を行うことができます。ブレークポイントを設定すると、左側にマークがつきます。また下側のコンソールメッセージを表示するウィンドウには標準出力に表示した文字列が表示されます。これは標準入出力、標準エラー出力に"jtag\_uart"を指定しているため下図のように表示されます。

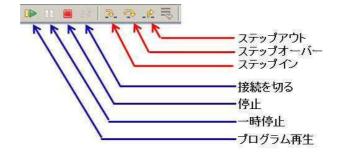

■ はデバッガを制御するためのツールバーアイコンです。

## 5. 更新履歴

| 日付        | 版 | 更新概要     |

|-----------|---|----------|

| 2014年2月1日 | 1 | • 初版リリース |

|           |   | •        |

|           |   | •        |

#### 免責、及び、ご利用上の注意

弊社より資料を入手されましたお客様におかれましては、下記の使用上の注意を一読いただいた上でご使用ください。

- 1. 本資料は非売品です。許可無く転売することや無断複製することを禁じます。

- 2. 本資料は予告なく変更することがあります。

- 3. 本資料の作成には万全を期していますが、万一ご不明な点や誤り、記載漏れなどお気づきの点がありましたら、下記までご一報いただければ幸いです。

株式会社アルティマ

戦略技術本部 Mpression 推進部

〒222-8561 横浜市港北区新横浜 1-6-3 HP: <a href="http://www.m-pression.com">http://www.m-pression.com</a>

- 4. 本資料で取り扱っている回路、技術、プログラムに関して運用した結果の影響については、責任を負いかねますのであらかじめご了承ください。5. 製品をご使用になる場合は、各デバイス・メーカの最新資料もあわせてご利用ください。