概要

ワイドバンドギャップ半導体を用いた高周波スイッチは、電力変換の効率化に貢献します。その一例である炭化ケイ素のスイッチは、SiC MOSFETとして、またはカスコード構成のSiC FETとして実装することができます。

本記事では、SiC FETの起源と最新世代への進化をたどり、その性能を他の技術と比較しています。4回にわたって、物理特性の違い、理想的なスイッチに対してのアプローチおよび特長、信頼性、実アプリケーションにおけるユニークな使い方、について説明します。

SiC FET – 代替アプローチ

ワイドバンドギャップ技術の登場により、多くの半導体メーカーが既存の製造ラインを利用してSiC製のMOSFETを開発する道を選んだ一方で、「白紙」の状態から他の選択肢を検討するメーカーもありました。SiCを用いた最もシンプルなスイッチはJFET構造で、ゲート酸化膜がなく、ユニポーラー伝導デバイスであるため、MOSFETのような制限はありません。

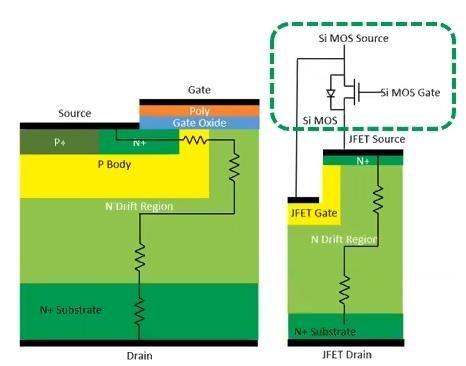

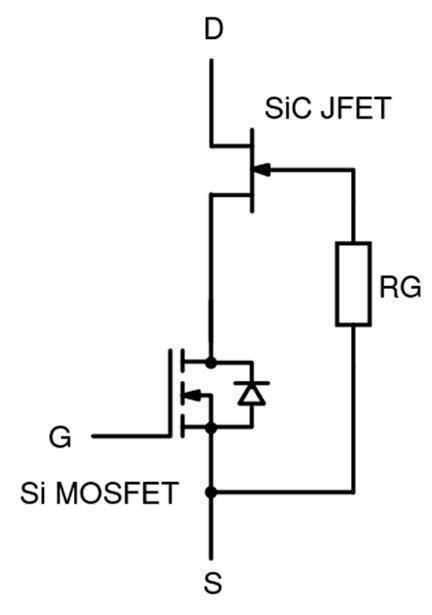

しかし、このデバイスには大きな欠点があります。それは、ゲート駆動が0Vの時には「通常オン」になり、オフにするには負の駆動が必要になることです。これは、特にシステムのオン/オフなどの過渡的な状況下では、不便であり、最悪の場合、アプリケーションの故障につながります。SiC FETは、SiC JFETとシリコンMOSFETを組み合わせたもので、通常はオフになっているが、MOSFETに対するJFETの利点を維持しています。図1は、SiC FETの配置(右)と、一般的なSiC MOSFETの回路図(左)を比較したものです。

SiC FETの配置はカスコードと呼ばれ、オーディオアンプのノイズ低減を目的とした真空管の組み合わせの原型を見たことがある大人のエンジニアには馴染み深いものかもしれません。カスコードまたは「エミッタースイッチ」は、バイポーラートランジスターやBJTとMOSFETの組み合わせなど、長年にわたってさまざまな形で登場してきましたが、一般的な特長は、低電圧スイッチが高電圧スイッチを制御し、高電圧定格と駆動のしやすさをうまく両立させることです。しかし、BJTを用いた回路は、ベースドライブ電流が大きく、スイッチング速度が遅いため、大電力では普及しませんでした。これらの問題を解決したのが、SiCカスコード、すなわち「SiC FET」です。

図2のSiC FETの回路図を参照すると、Si-MOSFETがゲートを介してオンになると、JFETのソースとゲートが実質的に短絡し、JFETが導通します。このとき、低電圧のSi-MOSFETのオン抵抗は、高電圧のSiC FETのオン抵抗に比べて非常に小さくできるため、JFETの伝導損失を固定したまま、JFETとMOSFETのドレイン・ソース間を電流が流れることになります。Si-MOSFETがオフになると、JFETのソース電圧が上昇し、ゲート-ソース間のしきい値(数ボルト負)を超えて、JFETがオフになります。デバイスの容量比のため、動的にはSi-MOSFETの電圧は低いままです。

SiC FETには、電気的性能と実用面の両方で、SiC MOSFETに勝る多くの利点があります。スイッチとしては、オン抵抗が大きな要因となりますが、SiC FETはSiC MOSFETに比べてチャネル内の電子移動度が非常に高いのが特長です。また、チャネル密度も高いため、同じ面積のダイに対して、SiC FETのオン抵抗は2〜4倍、逆に同じオン抵抗であれば、SiC MOSFETに比べて最大4倍のダイ数を得ることができます。シリコンスーパージャンクションのMOSFETと比較すると、最大で13倍のダイ数を得ることができます。材料としての炭化ケイ素はシリコンよりも常に高価である可能性が高いため、ウェハーあたりのドロスダイの増加は、SiC FET技術の成功に不可欠です。これまで述べてきたように、ダイの実行可能性を測る指標は、メリットの数値であるRDSAです。

もう1つのメリットは、RDS*EOSS、つまり、オン抵抗とデバイスの出力スイッチングエネルギーのトレードオフであり、出力キャパシタンスから求められます。これは、ダイ内のセルをより多く並列化することで、オン抵抗と伝導損失を低減できるため、有用な指標です。しかし、面積が増加するだけでなく、静電容量が直接増加し、結果としてEOSSも増加するため、周波数依存のスイッチング損失が増加することになります。そのため、RDS*EOSSの値は小さい方が有利です。

SiC FETのゲートは、カスケード接続されたSi MOSFETのゲートと同じです。そのため、フルエンハンスメントと低RDSONを実現するために、12Vまたは15Vで容易に駆動することができ、絶対的な最大値である25Vまで大きなマージンを確保することができます。また、SiC FETのゲート駆動は、シリコンMOSFETやIGBTと公称互換性があるため、既存製品の設計アップグレードの際に、後方互換性を確保することができます。実際には、SiC MOSFETやGaN HEMTセルは、最適な効率とゲート上の過電圧に対する十分な保護のために、カスタムの駆動方法を必要とします。

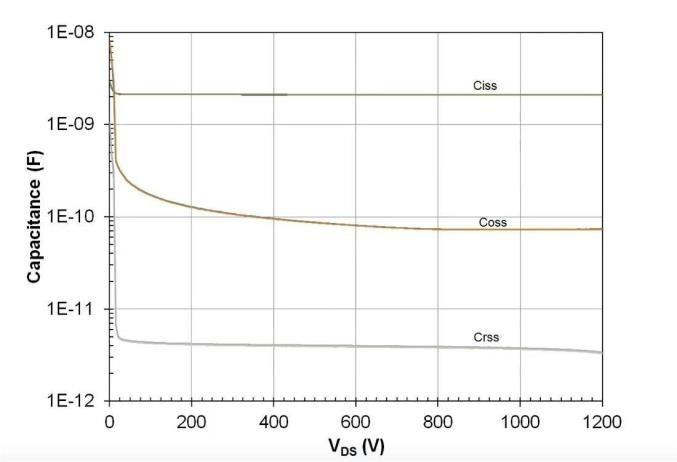

SiC FETは、デバイスの寸法が小さいことと、カスコード配列のSi MOSFETの絶縁効果により、ゲート・ドレインまたは「ミラー」キャパシタンスCrssがほとんどなく、超高速スイッチングが可能です。また、出力容量COSSとそれに伴うスイッチングエネルギーEOSSも小さく、損失を最小限に抑えた高速スイッチングを実現しています。エッジレートが非常に速いため、実用的な回路では、電圧のオーバーシュートやEMIを抑えるために、SiC FETを低速にする必要があります。これはゲート抵抗を追加することで可能ですが、高いスイッチング周波数では許容できないほどの制御遅延が発生するため、単純なRCスナバの方が良い解決策になることが多いです。通常、コンデンサーは約3×COSSに設定されているため、直列抵抗での損失は最小限に抑えられます。図3は、典型的なSiC FETデバイスの容量と、ブロッキング状態でのドレイン電圧の変化を示しています。それぞれの容量値の計算式は以下の通りです。

・Ciss = CGS + CGD

(CDSはショート)

・Crss = CGD

・Coss = CDS + CGD

SiCFET「ボディーダイオード」

電力変換器では、完璧なスイッチが低損失で両方向に導通することが求められます。これは、ACモータードライブや誘導負荷を持つコンバーターなどの回路で実際に求められるもので、いわゆる「第3象限」動作です。IGBTはこれができないので並列ダイオードが必要ですが、シリコンやSiCを用いたMOSFETやJFETは、ゲートの制御によりチャネルを介してどちらの方向にも導通します。

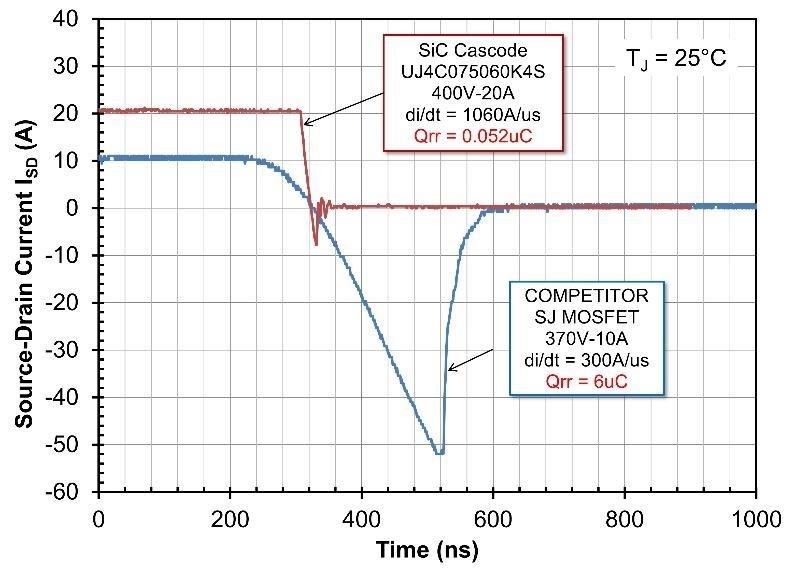

また、MOSFETにはJFETにはないボディーダイオードが内蔵されており、誘導負荷を持つハードスイッチコンバーターでは、ゲートを介してデバイスのチャネルがオンになる前の「デッドタイム」に、このボディーダイオードが「整流」によって自動的に導通し、逆方向の電流が流れるようになっています。この導通により電荷Qrrが蓄積され、その後ボディーダイオードが逆バイアスされたときに回収されます。

この動作により、大きなピーク電力が消費され、周波数が高くなるにつれて平均値が高くなり、効率が低下します。シリコン系のMOSFETでは、この影響が非常に大きく、一般的なトーテムポール型PFCステージのようにCCM(Continuous Conduction Mode)で動作する回路では、実質的に使用できない場合があります。SiC MOSFETは、Qrr値がSiの10倍程度になりますが、デバイスの出力容量が小さく、低電圧MOSFETの蓄積電荷が少ないため、SiC FETの方がさらに優れています。比較は、デバイスの電圧クラスによって異なりますが、図4は、SiC FETと同様のシリコンスーパージャンクションMOSFETの典型的な逆回復プロットです。

SiC MOSFETやGaNデバイスは、逆回復損失が十分に少ないか、あるいは全くないとはいえ、逆導通による電圧降下は別物です。これにより、電力変換器のデッドタイム時に大きな損失が発生します。Si製のスーパージャンクションMOSFETは、通常1V程度のダイオードドロップを示し、SiC製のMOSFETは、容易に4Vをドロップするボディーダイオードがあるため、さらに悪化します。第3象限動作のGaN HEMTセルは、I*Rチャネル電圧とゲートしきい値電圧の合計からゲートソース電圧を差し引いた電圧Vsdを落とします。Vsdの計算式は以下です。

・Vsd = (Vth-Vgs)+(Isd*Ron)

GaNのゲートしきい値は通常1.5Vなので、大電流ではトータルドロップが大きくなります。一般的に、ゲートをオフにするためにゲートを負に駆動すると、この電圧Vgsがソース・ドレイン間のドロップに加わり、結果としてVsdが数ボルトになり、他の技術に比べて大幅に悪化する可能性があります。また、SiC FETは、ソース-ドレイン間を導通させると、GaNデバイスと同様にチャネル抵抗によるI*Rドロップが発生しますが、このドロップは、低電圧カスケード接続されたSi MOSFETのボディーダイオードにかかる電圧によってのみ増加し、比較的低くなります。その結果、順方向電圧降下は通常約1.5Vとなり、SiC MOSFETやGaNの性能よりも優れています。

お問い合わせ

本記事に関してご質問などありましたら、以下より問い合わせください。

Qorvoメーカー情報Topページへ

Qorvoメーカー情報Topページへ戻りたい方は、以下をクリックください。