# Quartus II はじめてガイド

## タイミング制約の簡易設定方法

### ～ TimeQuest Timing Analyzer Wizard ～

ver.10.01

2010年8月

# Quartus II はじめてガイド - タイミング制約の簡易設定方法

## ~ TimeQuest Timing Analyzer Wizard ~

### 目次

|                                     |    |

|-------------------------------------|----|

| 1. はじめに .....                       | 3  |

| 2. 操作方法 .....                       | 4  |

| 2-1. ウィザードによる SDC ファイルの作成 .....     | 4  |

| 2-2. Quartus II に SDC ファイルを登録 ..... | 11 |

## 1. はじめに

現在アルテラでは、Quartus® II でタイミング制約を作成する場合、ASIC 業界の標準フォーマットになっている Synopsys Design Constraints (SDC) ファイルの使用を推奨しています。SDC ファイルを使用することで、TimeQuest Timing Analyzer と言う高性能なタイミング解析を行えるだけでなく、Quartus II に対して TimeQuest の解析結果に基づいた配置配線を実行させることも可能です。

SDC は、各タイミング制約を適切なコマンドにして記述します。また、SDC のタイミング制約の考え方には特徴があるため、今まで Quartus II においてクラシックなタイミング制約入力方法である Classic Timing Analyzer を使用していたユーザの中には、若干抵抗を感じるユーザもいるかもしれません。そのような方 (Classic Timing Analyzer のパラメータの考え方の方) でも SDC ファイルでデザインのタイミング制約を簡単に設定できるように、Quartus II 10.0 では TimeQuest Wizard を採用しています。

そのためこの資料の対象者は、過去に Quartus II の Classic Timing Analyzer を使用していたユーザです。そのため、Node Finder などの基本的な操作方法は省略しています。ご了承ください。

Quartus II を初めて使用するユーザ、または TimeQuest を通常通り使用するため SDC の具体的な記述方法や TimeQuest の解析方法を知りたいユーザは、本資料をご入手になった販売代理店の技術情報サイトにて、下記資料をご参考ください。

### 資料タイトル 『Quartus II - TimeQuest クイック・ガイド』

なお、TimeQuest でのタイミング制約および解析は、Quartus II 10.0 でサポートしているデバイスのうち MAX® 7000、MAX 3000 ファミリを除く全てのデバイスが対象です。MAX 7000、MAX 3000 ファミリの場合は、Classic Timing Analyzer をご利用ください。

<Note>

- ・ ウィザードによる SDC ファイル作成では、作成できるコマンドに限りがあります。(例えば、内部生成クロックの制約は、ウィザードでは作成できません。) このそれ以外のコマンドは、ウィザードで SDC ファイルを作成後に、直接追記するか SDC ファイル・エディタの Insert Constraints (Edit メニュー) により入力してください。

※ SDC ファイル・エディタの Insert Constraints (Edit メニュー) を利用する場合は、Name Finder の操作が必要です。操作方法は、上記資料(「Quartus II - TimeQuest クイック・ガイド」)をご覧ください。

- ・ ウィザードで作成した SDC ファイルは、再びウィザードにより編集することはできません。

- ・ デザイン内の PLL (phase-locked loop) 回路の入出力周波数情報の制約も、このウィザードで作成できます。

## 2. 操作方法

### 2-1. ウィザードによる SDC ファイルの作成

以下の操作は、すでにデザインのプロジェクトが設定されていることと、Analysis & Synthesis 以降のプロセスが実行されていることを前提にご案内しています。

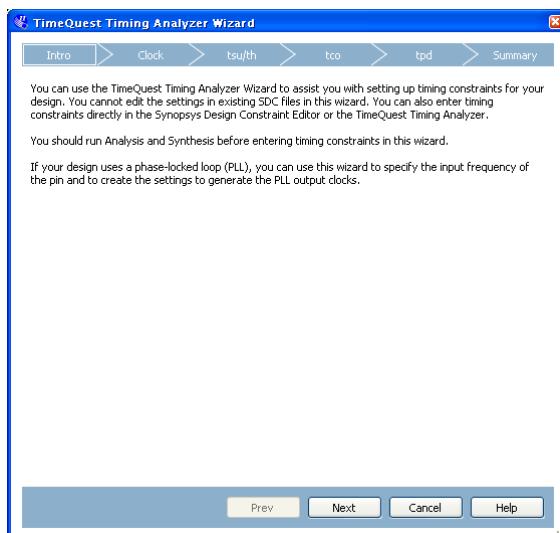

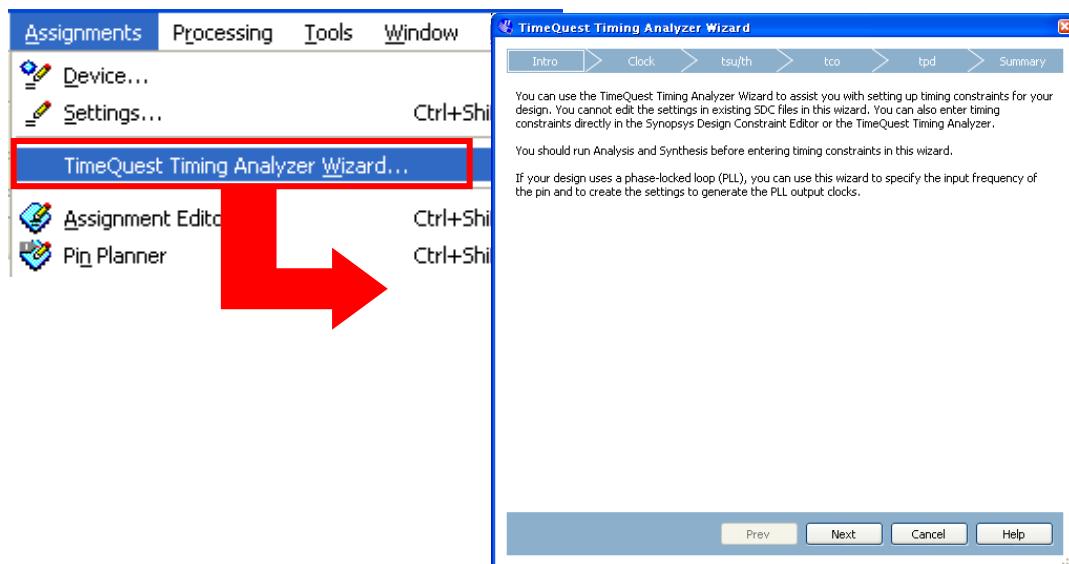

- ① Assignments メニュー ⇒ TimeQuest Timing Analyzer Wizard を選択し、ウィザードを起動します。

- ② Next ボタンをクリックします。

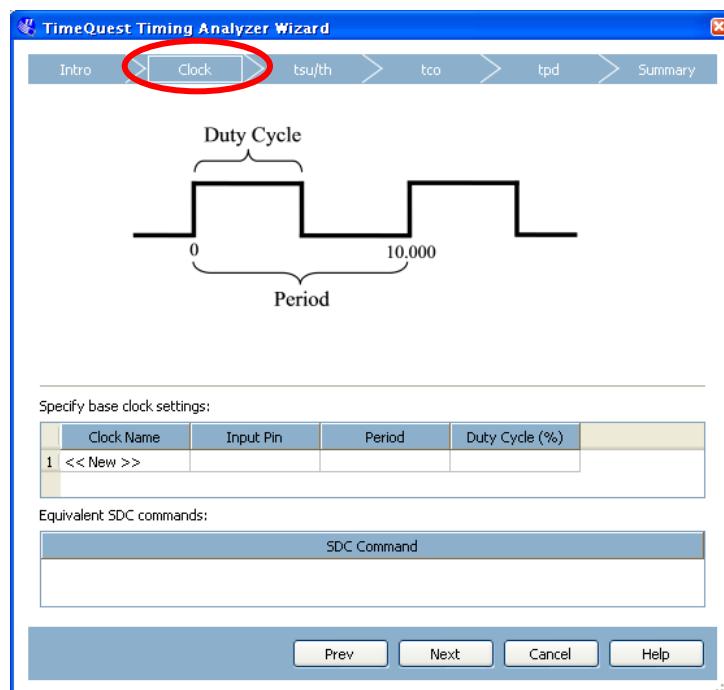

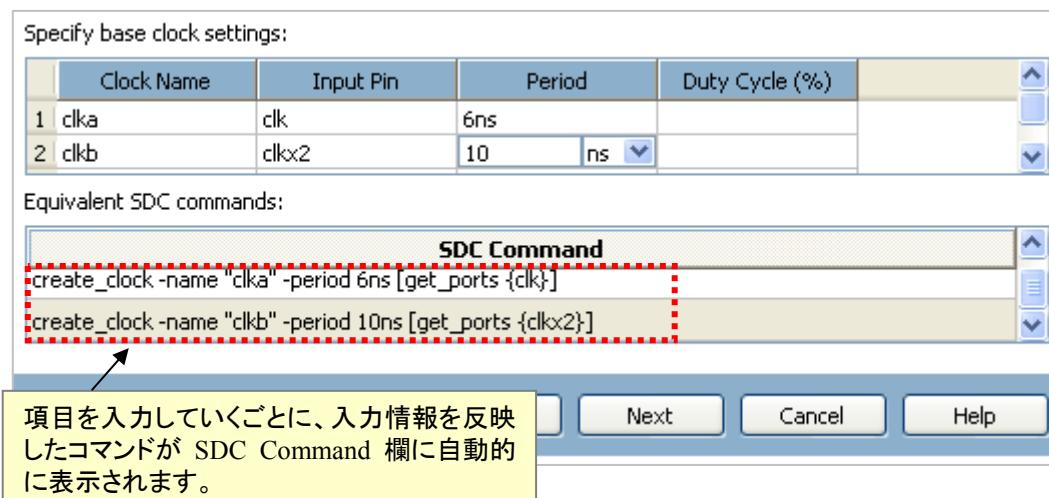

- ③ クロックの制約を作成します。

ここで作成できるクロック制約は、デバイスのピンから入力されるクロックです。内部生成されるクロックの制約は設定できません。内部生成されるクロックの制約は、SDC ファイルに適切なコマンドを直接入力するか、TimeQuest を使用して SDC ファイルを作成してください。

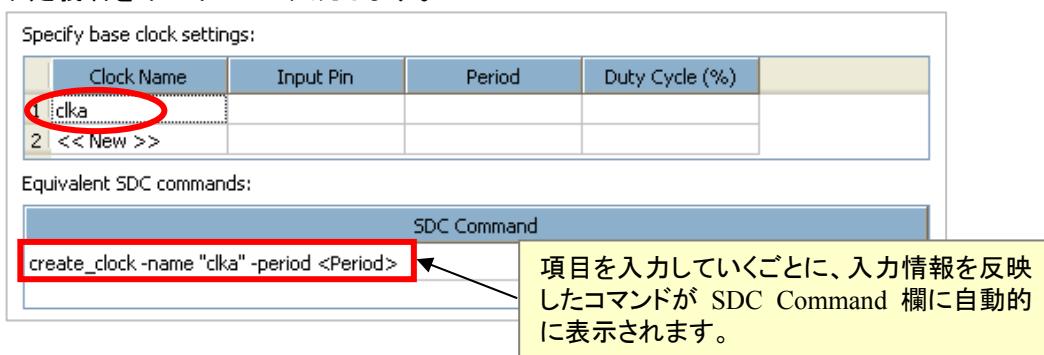

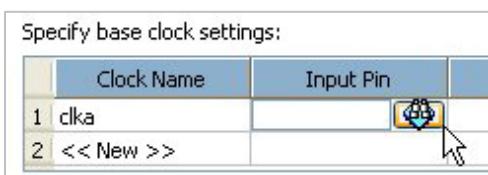

- 1) Clock Name 欄にクロック定義名(任意)を入力します。<< New >> 部分をダブルクリックし、クロック定義名をキーボードで入力します。

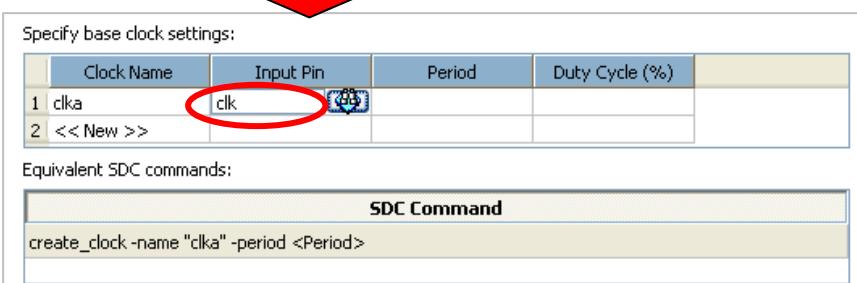

- 2) Input Pin 欄にクロック制約を与えるデザイン上のピン名を選択します。Input Pin 欄をダブルクリックし、 ボタンをクリックします。

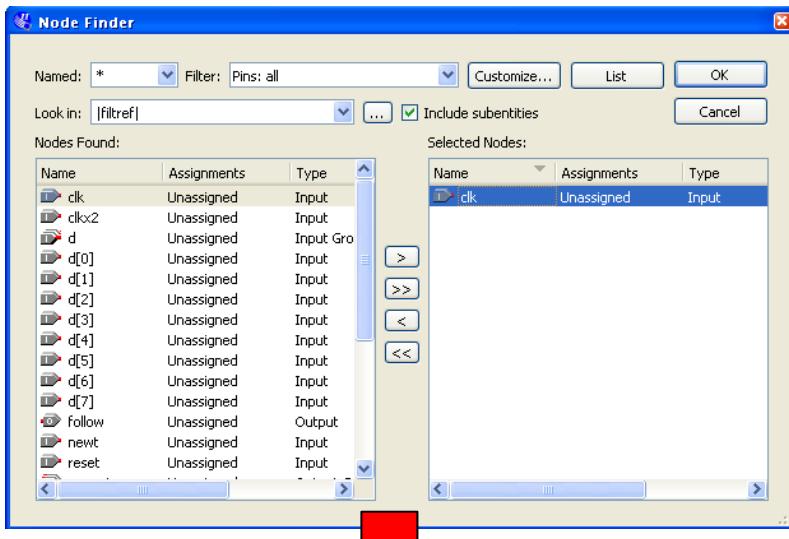

- 3) Node Finder が起動しますので、目的のクロックピンを選択します。

<Note>

- Node Finder の操作方法は、本資料をご入手になった販売代理店の技術情報サイトにて、下記資料をご参考ください。

資料タイトル 『Quartus II はじめてガイド - Assignment Editor の使い方』

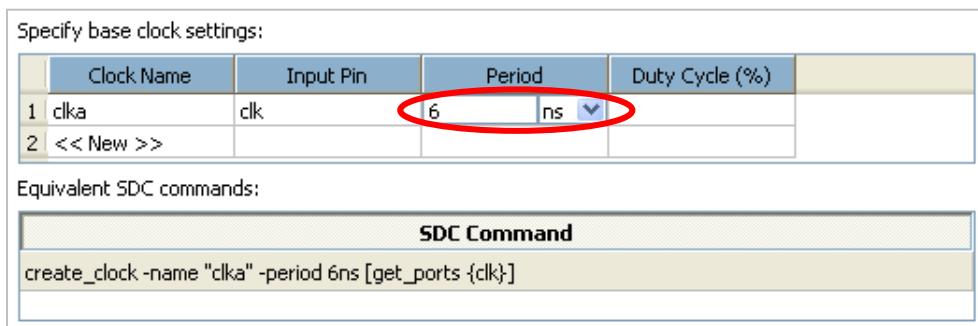

- 4) Period 欄にクロック制約値をキーボード入力し、単位をプルダウンリストから選択します。

- 5) Duty Cycle (%) 欄に Duty 比を入力します。Duty 比が 50% の場合は、空欄で構いません。

- 6) クロック制約を設定するピンが他にあれば、同様に設定を入力します。

- 7) クロック制約の設定が全て完了したら、Next ボタンをクリックします。

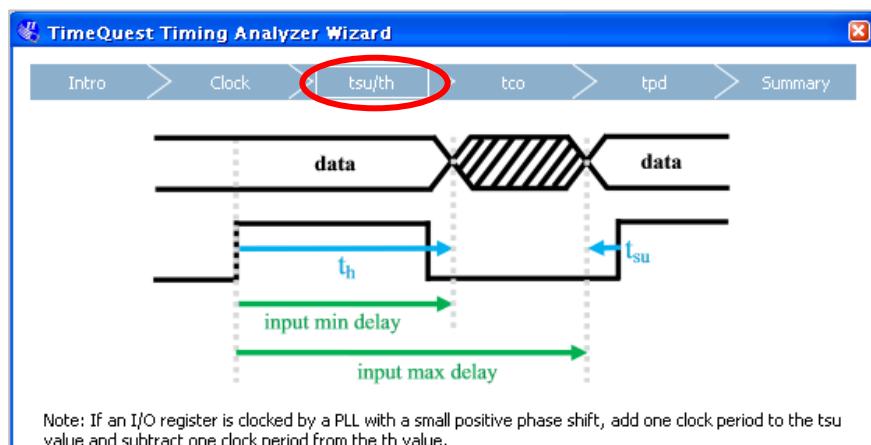

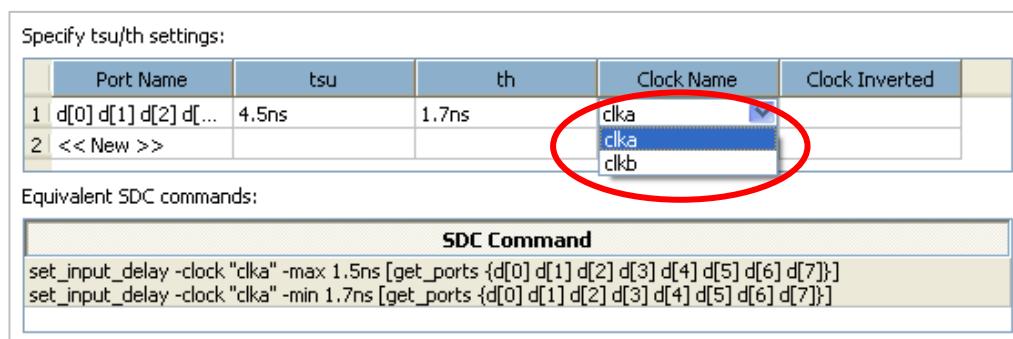

- ④ 入力ピン全てのタイミング制約をそれぞれ作成します。

<Note>

- セッタップタイム tsu … SDC では、デバイス外部からの全ての最大入力遅延(input max delay)のこと

- ホールドタイム th … SDC では、デバイス外部からの全ての最小入力遅延(input min delay)のこと

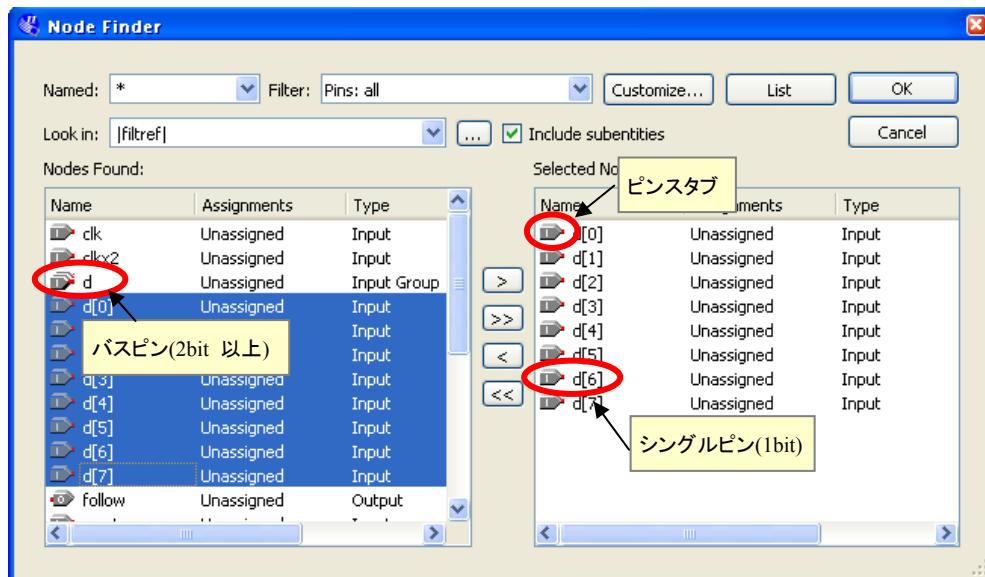

- 1) Port Name 欄に入力ピン名を選択します。Port Name 欄の << New >> 部分をダブルクリックし、 ボタンをクリックします。

- 2) Node Finder が起動しますので、目的の入力ピンを選択します。

<Note>

- ピンは、1 ピンのピンスタブで選択してください。2bit 以上のバスを表すピンスタブを選択しても、ウィザードではバスピンと認識されません。また自動的にワイルドカードも付きませんのでご注意ください。(SDC シンタックス・エラーの要因になります。)

- ワイルドカード(\*)を引用する場合は、Node Finder でピンを選択後、Port Name 欄に入力された後でキーボードにより手入力してください。

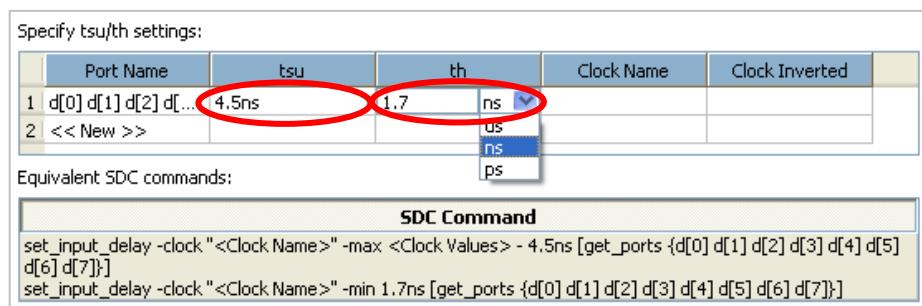

- 3) セットアップタイム tsu と ホールドタイム th の制約値をそれぞれキーボード入力し、単位をプルダウンリストより選択します。

- 4) Clock Name 欄をダブルクリックし、先に設定したクロック定義名を選択します。(入力ピンに接続されている初段レジスタのドライブ・クロックが該当します。)

- 5) そのレジスタがクロックの立ち下がりでドライブする場合は、Clock Inverted 欄をダブルクリックし、Yes を選択します。

- 6) デザイン上に存在する全ての入力ピンに、同様の設定を行います。設定完了後、Next ボタンをクリックします。

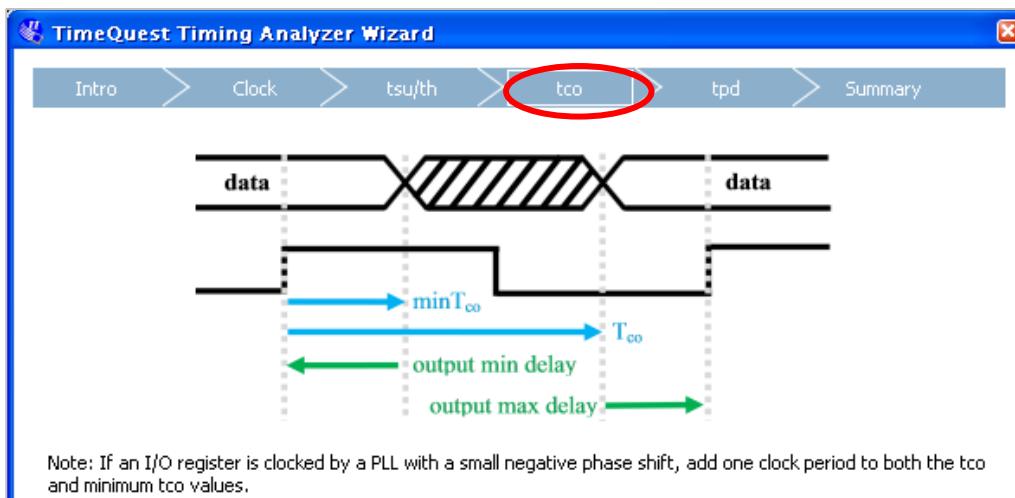

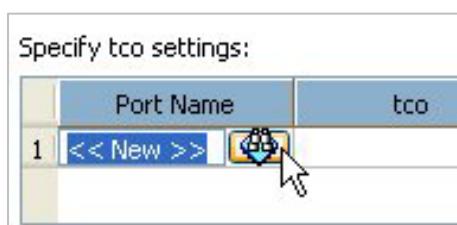

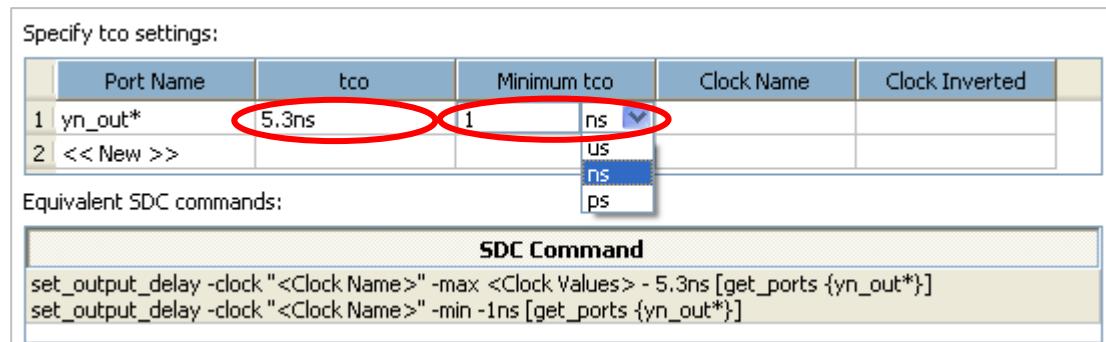

⑤ 出力ピン全てのタイミング制約を作成します。

<Note>

- クロック to アウトプット Tco

- SDC では、デバイス外部の全ての最大出力遅延(output min delay)のこと

- 最小クロック to アウトプット mim Tco

- SDC では、デバイス外部の全ての最小出力遅延(output min delay)のこと

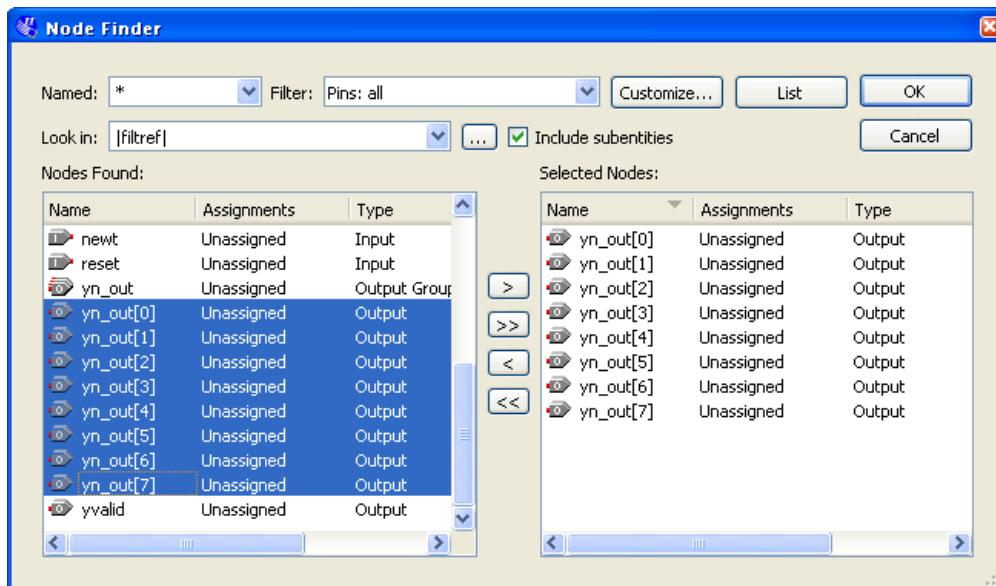

- 1) Port Name 欄に出力ピン名を選択します。Port Name 欄の << New >> 部分をダブルクリックし、 ボタンをクリックします。

- 2) Node Finder が起動しますので、目的の出力ピンを選択します。

<Note>

- ピンは、1ピンのピンstabで選択してください。2bit 以上のバスを表すピンstabを選択しても、ウィザードではバスピンと認識されません。また自動的にワイルドカードも付きませんのでご注意ください。(SDC シンタックス・エラーの要因になります。)

- ワイルドカード(\*)を引用する場合は、Node Finder でピンを選択後、Port Name 欄に入力された後でキーボードにより手入力してください。

- 3) クロック to アウトプット tco と Minimum tco の制約値をそれぞれキーボード入力し、単位をプルダウンリストより選択します。

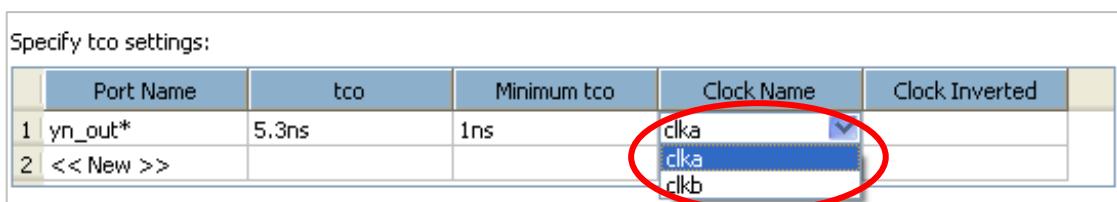

- 4) Clock Name 欄をダブルクリックし、先に設定したクロック定義名を選択します。(出力ピンに接続されている最終段レジスタのドライブ・クロックが該当します。)

- 5) そのレジスタがクロックの立ち下がりでドライブする場合は、Clock Inverted 欄をダブルクリックし、Yes を選択します。

- 6) デザイン上に存在する全ての出力ピンに、同様の設定を行います。設定完了後、Next ボタンをクリックします。

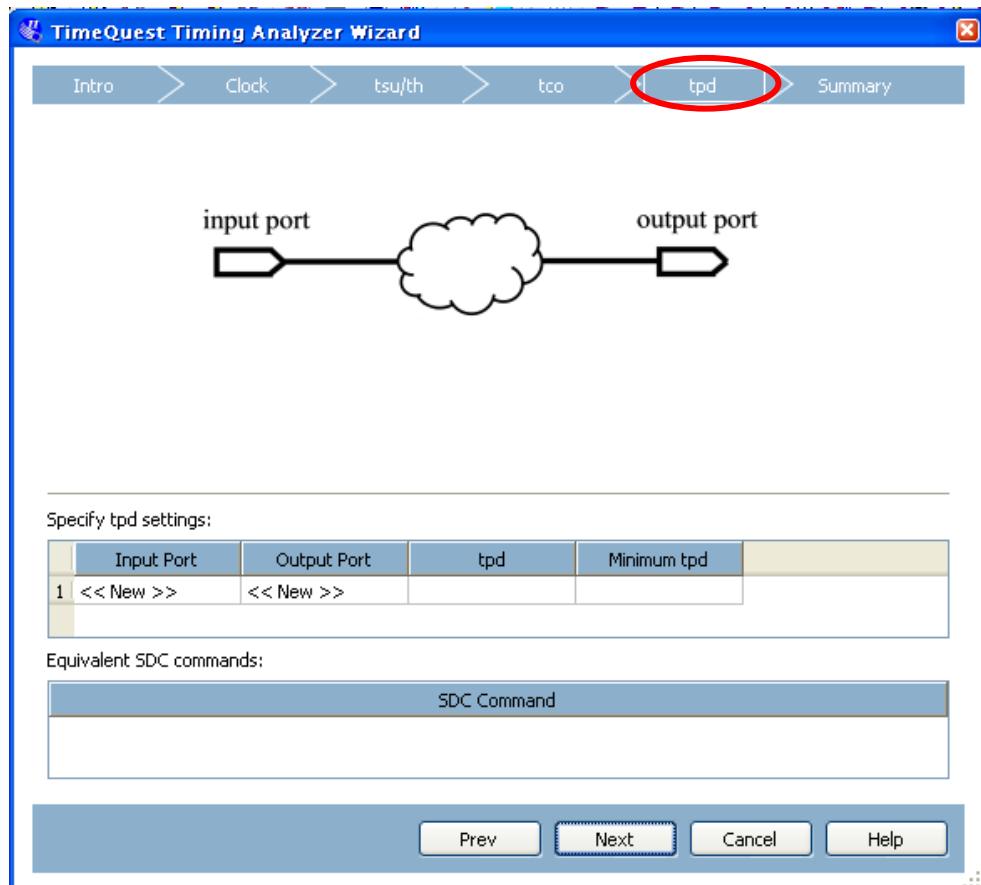

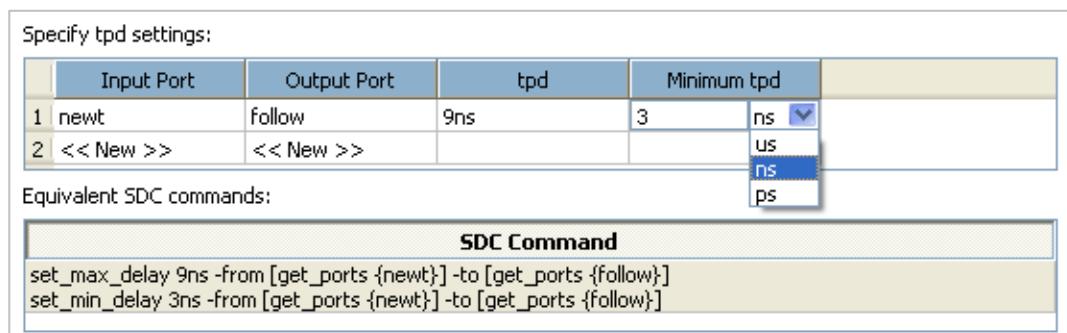

⑥ 入力ピンから出力ピン間にレジスタを一切介さないパスの全てのタイミング制約を作成します。

&lt;Note&gt;

- ピン間ディレイ tpd … SDC では、ポイント間の最大パス遅延(max delay)のこと

- 最小ピン間ディレイ Minimum tco … SDC では、ポイント間の最小パス遅延(min delay)のこと

- 1) Input Port 欄に入力ピン名を選択します。Input Port 欄の << New >> 部分をダブルクリックし、

[ ] ボタンをクリックします。

- 2) Node Finder が起動しますので、目的の入力ピンを選択します。

- 3) 同様に、Output Port 欄に出力ピン名を選択します。Output Port 欄の << New >> 部分をダブルクリックし、[ ] ボタンをクリックします。

- 4) Node Finder が起動しますので、目的の出力ピンを選択します。

- 5) ピン間ディレイ tpd と Minimum tpd の制約値をそれぞれキーボード入力し、単位をプルダウンリストより選択します。

- 6) デザイン上に存在する全てのレジスタを一切介さないピン間遅延に、同様の設定を行います。設定完了後、Next ボタンをクリックします。

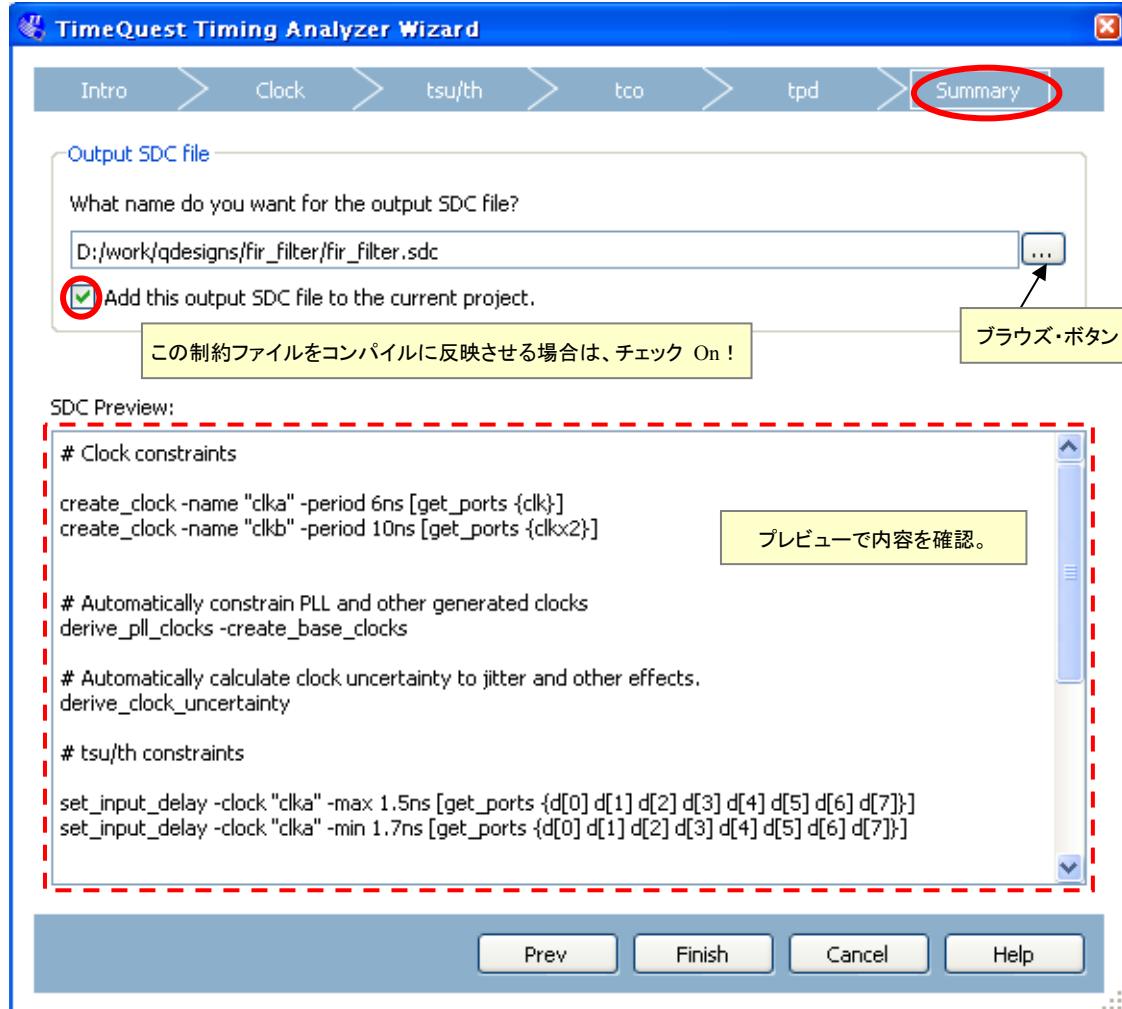

- ⑦ Summary にて、SDC ファイルの保存場所とファイル名を指定し、コマンドの内容を確認します。

- ⑧ Finish ボタンをクリックし、SDC ファイルを生成します。

以上で、SDC ファイルの簡易作成は終了です。

## 2-2. Quartus II に SDC ファイルを登録

作成・保存した SDC ファイルの制約内容を Quartus II のコンパイル実行時に有効にするため登録します。TimeQuest Timing Analyzer Wizard の Summary 画面で、“Add this output SDC file to the current project.” オプションを有効にして作業を完了した場合には、この操作は不要です。

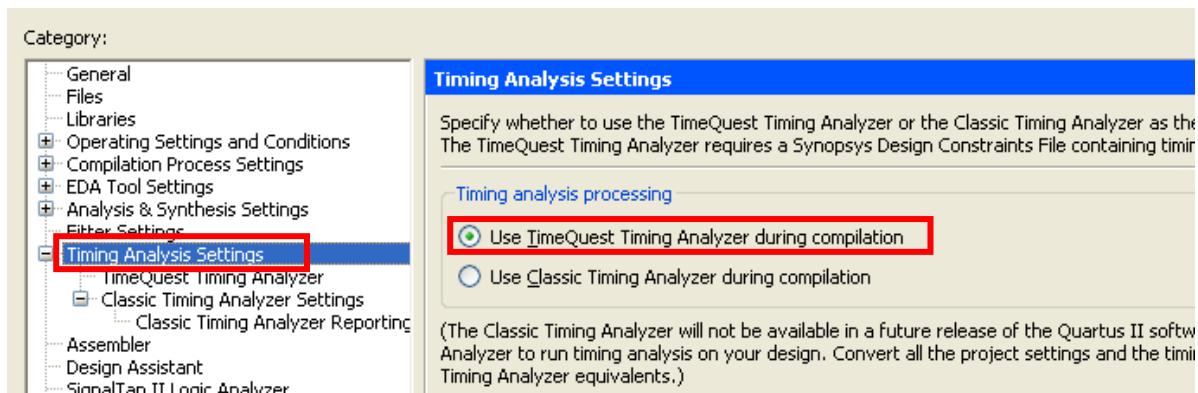

- ① Assignments メニュー ⇒ Settings を選択します。

- ② Settings ダイアログボックスの Category から Timing Analysis Settings を選択し、“Use TimeQuest Analyzer During compilation”を選択します。

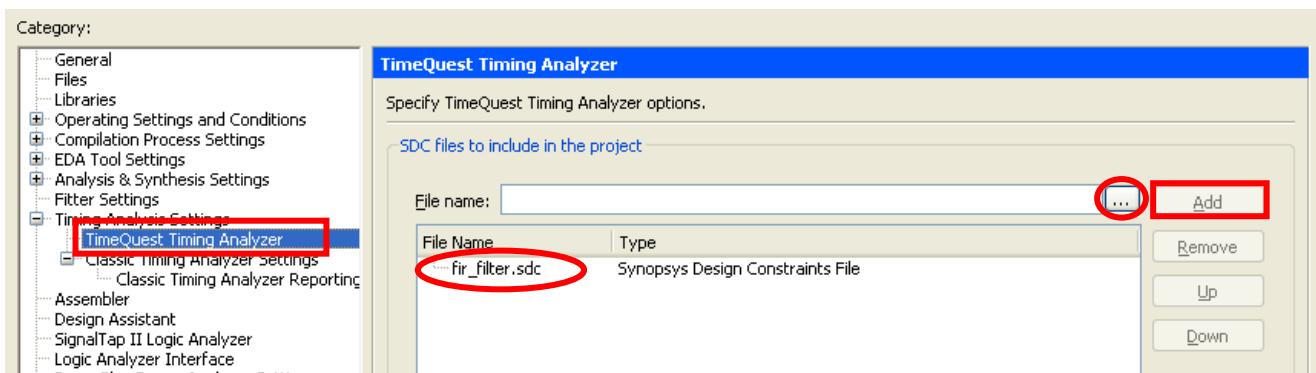

- ③ Category を TimeQuest Timing Analyzer に切り替えます。

④ SDC files to include in the project の File name 欄に、作成した SDC ファイルを指定します。(ブラウズ・ボタンを利用)

⑤ Add ボタンをクリックし、登録します。

- ⑥ 必要な SDC ファイルの登録が完了後、Settings ダイアログボックスの OK ボタンをクリックします。

以上で、SDC ファイルの登録は完了です。

その後の操作やコンパイル後のレポートなどのタイミング解析方法については、本資料をご入手になった販売代理店の技術情報サイトにて、下記資料をご参考ください。

資料タイトル 『Quartus II - TimeQuest クイック・ガイド』

### 免責、及び、ご利用上の注意

弊社より資料を入手されましたお客様におかれましては、下記の使用上の注意を一読いただいた上でご使用ください。

1. 本資料は非売品です。許可無く転売することや無断複製することを禁じます。

2. 本資料は予告なく変更することがあります。

3. 本資料の作成には万全を期していますが、万一ご不明な点や誤り、記載漏れなどお気づきの点がありましたら、本資料を入手されました下記代理店までご一報いただければ幸いです。

株式会社アルティマ：〒222-8563 横浜市港北区新横浜 1-5-5 マクニカ第二ビル TEL: 045-476-2155 HP: <http://www.altima.co.jp>

技術情報サイト EDISON : <https://www.altima.jp/members/index.cfm>

株式会社エルセナ：〒163-0928 東京都新宿区西新宿 2-3-1 新宿モノリス 28F TEL: 03-3345-6205 HP: <http://www.elsena.co.jp>

技術情報サイト ETS : <https://www.elsena.co.jp/elspear/members/index.cfm>

4. 本資料で取り扱っている回路、技術、プログラムに関して運用した結果の影響については、責任を負いかねますのであらかじめご了承ください。

5. 本資料は製品を利用する際の補助的な資料です。製品をご使用になる場合は、英語版の資料もあわせてご利用ください。