# Technical Note

## グランド・バウンス現象の対策

文書管理番号: ELS0319\_S000\_10

2006年3月

株式会社エルセナ

## 1 グランド・バウンス

グランド・バウンスとは、多数の出力がロジック“1”的状態から同時にロジック“0”になった場合に、負荷容量に蓄積されていた電荷がグランドを通して放電される時に引き起こされるグランド電位の変動を言います。回路上に接続された負荷容量(浮遊容量)に蓄積された電荷からの瞬時放電電流をグランドに吸収できない場合やグランド・バス上に寄生する誘導性負荷に流れる電流によって誘起される起電力によって、グランドが弾む「グランド・バウンス」現象が発生します。この現象による影響は、通常、誤動作としてのファンクション不良として現れます。

デジタル・デバイスが高速化することにより、出力のスイッチング時間は更に短くなっています。高速のスイッチング時間によって出力にはより大きな電流遷移が起き、負荷のキャパシタンスがディスチャージされます。複数のデバイス出力が High レベルから Low レベルへ同時に変化した時に発生する高電流は、グランド・バウンスと知られている基板レベルでの現象を引き起こします。時によっては、ロジックのスレッショールド・レベルを超えるようなグランド・バウンスが発生し、回路の誤動作を誘発します。

グランド・バウンスには多くの要因が関係しています。その為、全ての PWB の環境における影響を予測できるような標準的なテスト方法は存在しません。従って、グランド・バウンスの発生要因を極限まで下げる必要があります。

## 2 同時スイッチングによるグランド・バウンス

同時スイッチング・ノイズとは、同一パッケージ内で 1bit を静止させ、その他の bit を同時にスイッチングさせた時に静止 bit に誘起されるノイズをいいます。スイッチング過渡時には出力容量負荷のチャージ/ディスチャージ電流と IC の内部の貫通電流が Vcc 又は GND のリード・フレームのインダクタンス成分によりチップ内の Vcc 又は GND にバウンスが発生し、それが静止 bit にノイズとして現れます。

一般的な例としては、多ビットのデータ・バスが同時にスイッチングする場合や多段純2進カウンタが上げられます。多ビット・データ・バスにおいては、全ビットが“1”あるいは“0”的データが繰り返し出力される場合が最悪な状態です。多段 2 進カウンタにおいては、MSB ビットが“0”でその他のすべての下位ビットが“1”的時が最悪の状態となります。下位ビットが“1”的時に、その出力に接続されている負荷 IC の入力キャパシタやプリント基板上の浮遊容量などに電荷がチャージされています。次に、クロックが来た時に、カウンタの桁上げが発生し、MSB ビットが“1”となり、残りの下位ビットがすべて“0”になります(出力トランジスタがオンになります)。この時、負荷のキャパシタに蓄積されていた電荷が一齊に出力トランジスタを通してグランドへと突入します。この時の突入電流がグランド電位に吸収できない場合にグランド電位が上昇します。それが、結果として他の信号のロジック・レベルに悪い影響を及ぼします。この時に誘起されるグランド電位は、負荷容量( $\omega C$ )の大きさ、プリント基板のトレースやソケットによる誘導性負荷( $\omega L$ )の大きさ、あるいは、出力トランジスタのスイッチング特性( $f$ )に依存します。

### 3 グランド・バウンスの低減対策

#### 3-1 グランド・バウンスの発生メカニズム

CPLD/FPGA がより高速になると、その出力のスイッチング時間は益々小さくなります。そして、この高速度スイッチングによって、負荷容量に蓄積された電荷が放電する時に出力に大きなトランジエント電流が流れます。この高電流がボード・レベルにおいて、グランド・バウンスを引き起こします。そこで、ここでは、グランド・バウンスの発生するメカニズムを説明します。

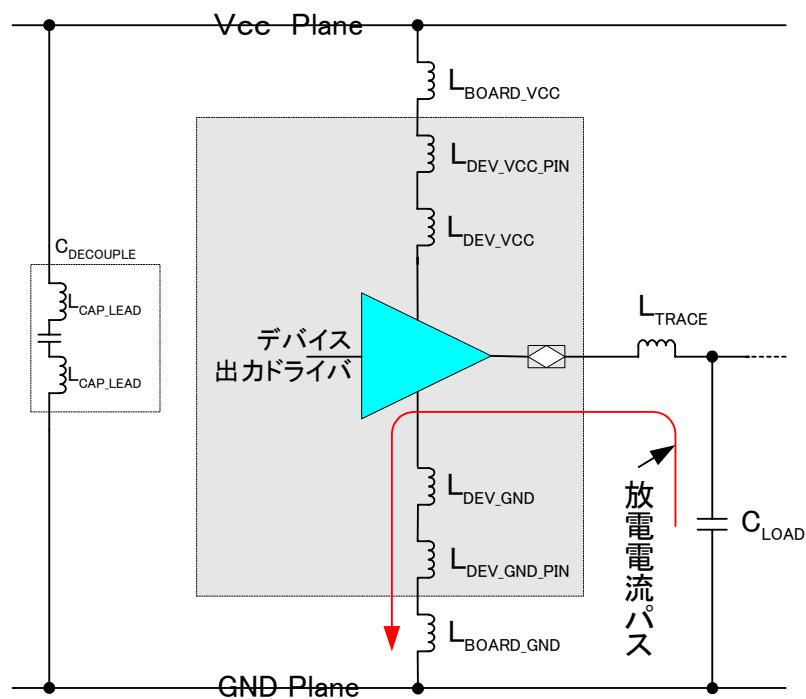

グランド・バウンスを解析するために、デバイスの容量性負荷について考えてみます。図 1 にプリント基板上のデバイスにおける誘導性負荷成分の分布と負荷容量について示します。抵抗成分については割愛しています。

図 1. ボード上に分布する誘導性成分と負荷容量

上図において、容量性負荷に充電される電荷量( $Q$ )は、式 1 で示されます。

$$Q = CV \quad \dots \dots \text{式 1}$$

従って、充電される電荷量( $Q$ )は、ドライブする電圧と負荷容量に依存して増減します。

一方、デバイスの出力ドライバがオンになることにより、負荷容量に蓄積された電荷が、グランド・パスを通して放電します。この時の放電パスに介在するのが各種のインダクタンスです。図1に示すように4つのインダクタンスからなります。

- |                |                                    |

|----------------|------------------------------------|

| ① LTRACE       | → プリント基板の配線によるインダクタンス              |

| ② LDEV_GND     | → デバイスのボンディング線によるインダクタンス           |

| ③ LDEV_GND_PIN | → デバイスのGNDピンからプリント基板間のインダクタンス      |

| ④ LBOARD_GND   | → デバイスとその負荷位置で参照されるグランド位置間のインダクタンス |

グランド・バウンスは、同一デバイス内の複数の出力が“1”から“0”にスイッチした時に発生します。そのトランジションは、負荷容量に蓄積されていた電荷がデバイスに急激に流れ込む際に発生します。そして、その放電電流がデバイスの出力からデバイス内のインダクタンス(LDEV\_GND, LDEV\_GND\_PIN)と参照されるグランド位置にかかるインダクタンス(LBOARD\_GND)を通してボードのグランドに流れ込む際に発生します。この時の電圧(V)は、式2のようになります。

$$V = L \frac{di}{dt} \quad \dots \dots \text{式 2}$$

Where;  $L = L_{DEV\_GND} + L_{DEV\_GND\_PIN} + L_{BOARD\_GND}$

ここで、負荷容量に蓄積された電荷が瞬時に放電すると、誘導性負荷によって誘起される起電力は式3と等価になります。

$$V = \omega L \cdot I = 2\pi f \cdot L \cdot I \quad \dots \dots \text{式 3}$$

Where;  $I$  は、負荷容量の蓄積電荷が放電する場合の総放電電流

$$L = L_{DEV\_GND} + L_{DEV\_GND\_PIN} + L_{BOARD\_GND}$$

式3で分かるように、グランド・バウンスとして誘起される電圧は、グランド・パス上に流れる電流、インダクタンス成分および動作周波数の関数であることが分かります。ですから、流れる電流が多ければ多いほど、グランド・パス内のインダクタンスが大きければ大きいほど、また、デバイスのスイッチング速度が速くなれば速くなるほど誘起電圧は大きくなります。デバイスの入力スレッシホールド電圧を超える電圧になることもしばしばです。

ここで、発生したグランド・バウンス(デバイス・グランドとボード・グランド間との電位差)は、ある信号がデバイスに入力される場合に、その入力点で入力信号に重畠され、ロー・レベルの上昇やハイ・レベルの低下として認識されます。結果として、このグランド・バウンスが入力のスレッシホールド電圧を超えるような場合に誤動作のようなファンクション不良としてシステム上に顔を出します。

ところで、グランド・バウンスの発生に直接影響を及ぼす主要要素について考えてみると、次の4点が挙げられます。

- ① 容量性負荷 → 負荷デバイスの入力容量や浮遊容量

- ② 誘導性負荷 → デバイスのボンディング線、プリント板の配線やソケット実装時の誘導性成分

- ③ 抵抗性負荷 → プリント基板等のグランド・パスに直列に入る抵抗成分

- ④ 動作周波数 → デバイスが持つスイッチング特性

これらの影響変数を管理することでグランド・バウンスをコントロールします。そのためには、概略次のことが言えます。

- ① 周波数を下げる。 → スロー・スルーレート・オプションの採用

- ② 回路抵抗を大きくする。 → グランド・パスに流れる電流を抑制

- ③ 負荷容量を減らす。 → 分割ドライブ等

- ④ 誘導性負荷を減らす。 → ソケット実装の取り止め等

### 3-2 グランド・バウンスの低減対策

それでは、具体的にグランド・バウンスを低減する為のヒントについて、説明します。

- ① ALTERA デバイス(EPM7032/7064/7096 を除く)のデザインに、スロー・スルーレートのロジック・オプションを ON に設定する。(次項参照)

- ② 74244 のようなバス・ドライバの IC を外付けバッファとして使用するか、1 つの負荷を分割ドライブすることにより負荷容量を減らす。 →  $\omega C$  成分の削減

- ③ 可能な限り、ソケットを取り除く →  $\omega L$  成分の削減

- ④ 同時にスイッチングする可能性のある出力信号の本数を減らす。あるいはデバイスの全体にこれらの出力ピンを均等に分配して配置する。

- ⑤ スイッチングする出力をパッケージのグランド・ピンの近傍に移動させる。

- ⑥ スイッチングする出力の隣にプログラマブルなグランド・ピンを設ける。

- ⑦ 出力端子に接続されるプルアップ抵抗を取り除くか、あるいはプルダウン方式に変更する。

- ⑧ Vcc、GND のプレーンが分離されている多層基板を使用する。

- ⑨ 各出力に  $10\sim35\Omega$  の直列抵抗を挿入してスイッチング電流を制限する。

- ⑩ 瞬間的にスイッチングするピンからの影響を受けないような同期設計を行う。

- ⑪ すべての GND - VCC ピン間にデカップリング・キャパシタを挿入する。(0.2  $\mu F$  のキャパシタを用い、なるべくデバイス近傍に置いてください。)

## 4 ソフトウェアによるスロー・スルーレート・オプションの設定

アルテラの開発ソフトウェア MAX+plus II、Quartus II 上でのスロー・スルーレート・オプションの設定方法を説明します。

### 4・1 MAX +plus II による設定方法

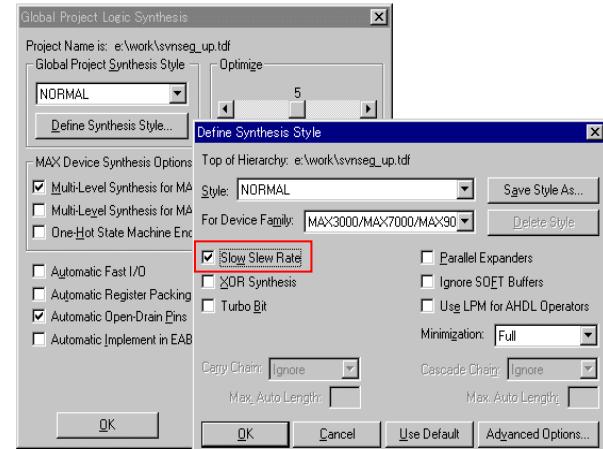

#### 4・1・1 デバイス・レベルでの設定

- Project 指定後 Assign→Global Project Logic Synthesis...→Define Synthesis Style...→Slow Slew Rate にチェック・マークを付けます。

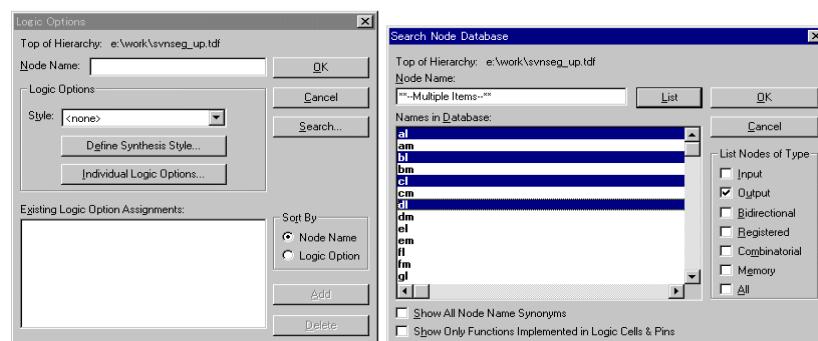

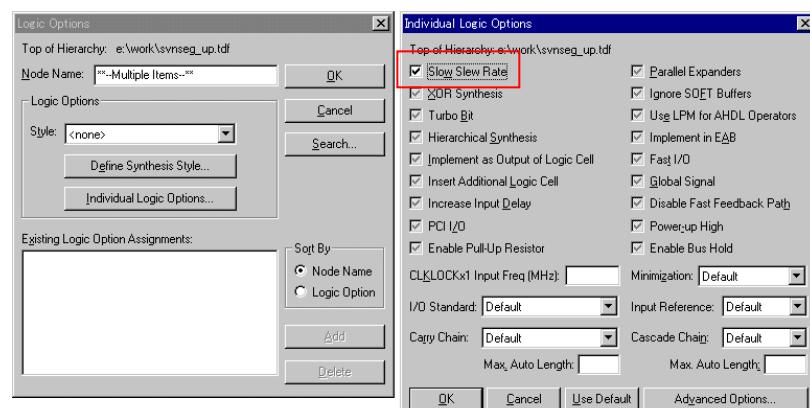

#### 4・1・2 ピン・レベルでの設定

- Project 指定後 File→Project→Save&Check 又は ボタンを選択。

- Assign→Logic Options...→Search...→List Nodes of Type を Output に設定→List→Ctl + クリックで目的のピンを選択→OK

- Individual Logic Options...→Slow Slew Rate をチェック→OK

## 4・2 Quartus II による設定方法

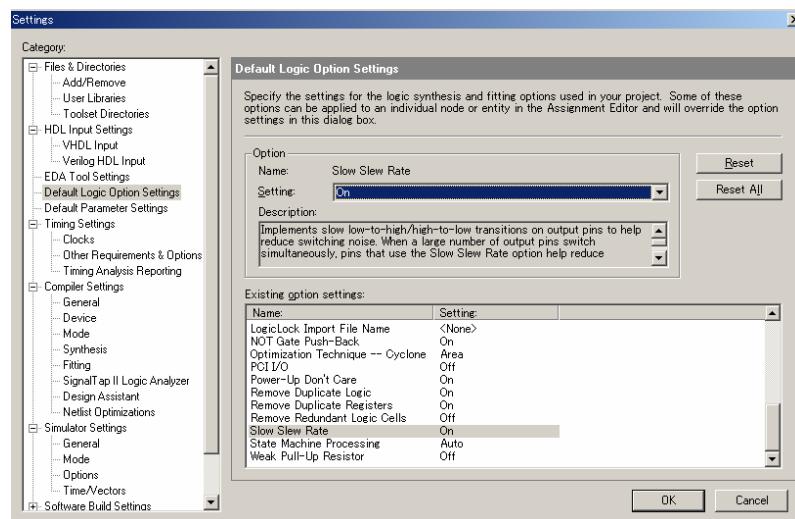

### 4・2・1 デバイス・レベルでの設定

- ① Project 指定後、Assignments → Settings → Default Logic Option Settings を選択

- ② Slow Slew Rate = On

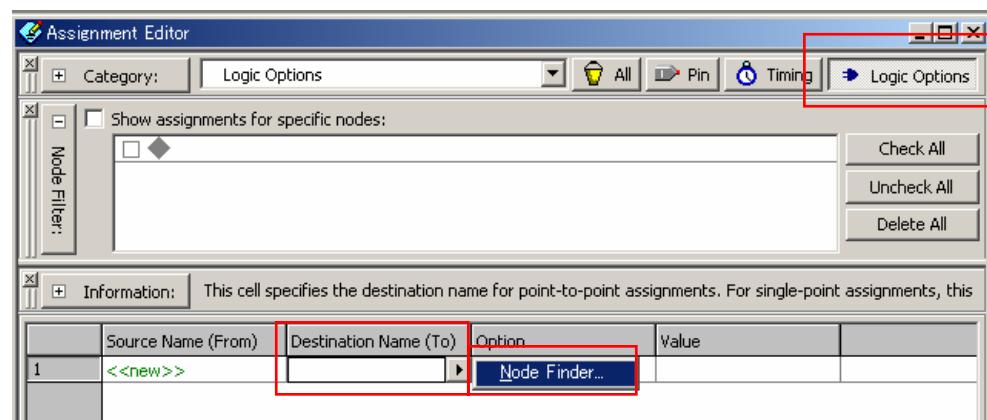

### 4・2・2 ピン・レベルでの設定

- ① Project 指定後 Processing→Start Analysis & Elaboration 又は  ボタンを選択。

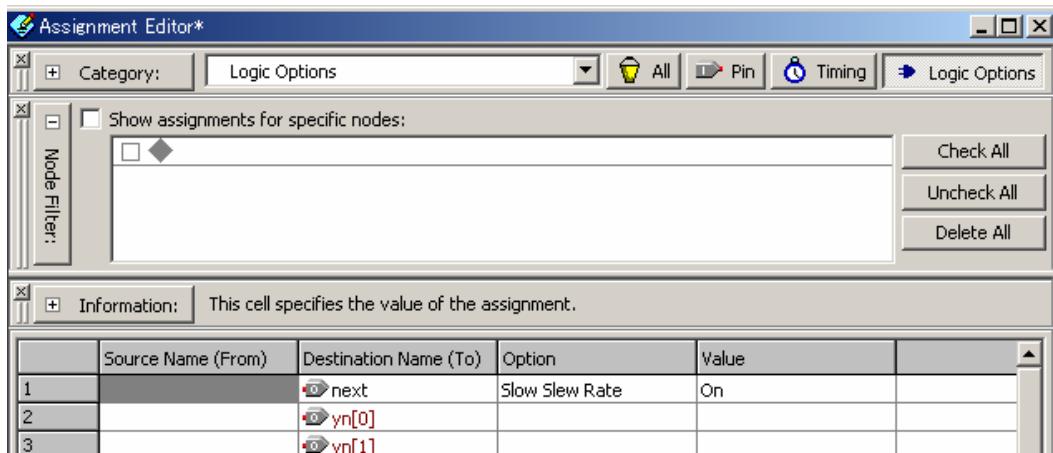

- ② Assignments → Assignment Editor を選択。

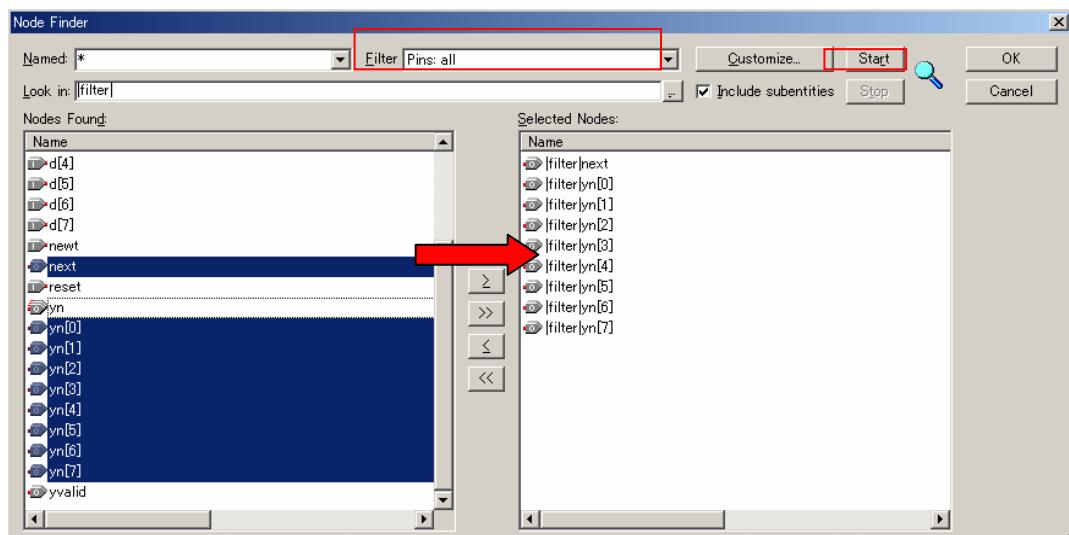

- ③ ウィンドウ内の”Logic Options”ボタンを選択。”Destination Name(To)”欄をダブルクリックし、”Node Finder...”ボタンを選択。(Node Finder ウィンドウが表示されます。)

- ④ Node Finder ウィンドウ内の”Filter:”を”Pins: all”へ変更し、Start ボタンをクリック

- ⑤ 目的のピンを Nodes Found(左枠)から選択して、中央にある  ボタンで Selected Nodes (右枠)へピンを移動、OK ボタン

- ⑥ “Option”欄をダブルクリックし、プルダウンリストより”Slow Slew Rate”を選択。

- ⑦ “Value”欄をダブルクリックし、プルダウンリストより”On”を選択。

- ⑧ File メニュー→Save より、設定内容を保存

## 5 おわりに

グランド・バウンスの現象は、思わぬシステム上の問題を引き起します。この現象は、環境変数(電圧変動、周囲温度変動、プロセス変更、製造ロット変更)によっても影響されます。従って、懸念される回路部分には十分な検討と対策が必要です。

## 改版履歴

| Version | 改定日      | 改定内容  |

|---------|----------|-------|

| 1.0     | 2006年03月 | ・新規作成 |

|         |          |       |

|         |          |       |

|         |          |       |

|         |          |       |

|         |          |       |

|         |          |       |

|         |          |       |

## 免責、及び、ご利用上の注意

弊社より資料を入手されましたお客様におかれましては、下記の使用上の注意を一読いただいた上でご使用ください。

3. 本資料は非売品です。許可無く転売することや無断複製することを禁じます。

4. 本資料は予告なく変更することがあります。

5. 本資料の作成には万全を期していますが、万一ご不審な点や誤り、記載漏れなどお気づきの点がありましたら、弊社までご一報いただければ幸いです。

6. 本資料で取り扱っている回路、技術、プログラムに関して運用した結果の影響については、責任を負いかねますのであらかじめご了承ください。

7. 本資料は製品を利用する際の補助的なものとしてかかれたものです。製品をご使用になる場合は、英語版の資料もあわせてご利用ください。

## 本社

〒163-0928 東京都新宿区西新宿2丁目3番1号 新宿モナリス 28F TEL 03-3345-6205 FAX 03-3345-6209

## 松本営業所

〒390-0815 長野県松本市深志1-1-15 朝日生命松本深志ビル1F TEL 0263-39-6134 FAX 0263-39-6135

## 大阪営業所

〒532-0003 大阪市淀川区宮原3丁目4番30号 ニッセイ新大阪ビル17F TEL 06-6397-1090 FAX 06-6397-1091

## 名古屋営業所

〒450-0002 愛知県名古屋市中村区名駅3丁目11番22号 IT名駅ビル4F TEL 052-566-2513 FAX 052-566-2514