# **Lattice iCE40 Slave SPI Configuration ユーザーガイド**

## Tecstar はじめに

- 本資料は、Lattice社iCE40使用時の注意事項、注意事項をまとめたものです。 実際の動作等詳細、最終の確認は、別途データシート、テクニカルノートを参照 頂けるようお願い申し上げます。

- Lattice社データシートと本資料との間に差異があった場合には、Lattice社データ シートを正としてお取り扱い下さい。

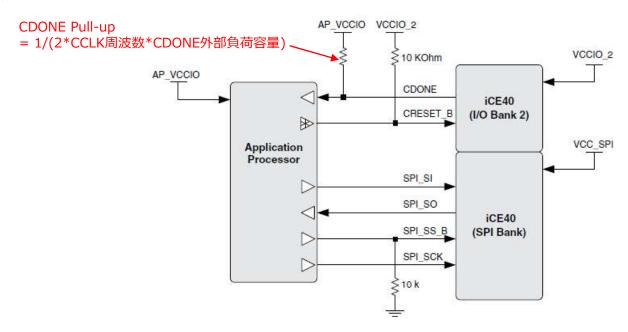

#### **Slave SPI Configuration接続図**

iCE40に対してプロセッサからコンフィグデータを送信し、コンフィグレーションを行う方式を Slave SPI Configurationと呼びます。プロセッサとiCE40を以下の図のようにSPI通信ができるよう 接続して下さい。

- 上図には記載されておりませんが、Slave SPI Configuration時、VPP 2V5には1.71V 3.46Vを入力して下さい。

- SPI SOはSlave SPI Configurationには使用しませんので、接続しなくても問題ございません。

- CRESET BはiCE40に入力されますので、iCE40のBank2のインターフェース電圧(VCCIO\_2)に合わせるか、 プロセッサ側をOpen Drain出力にし、VCCIO 2でプルアップするようにして下さい。

- CDONEはプロセッサに入力されるOpen Drain出力ですので、プロセッサ側のI/O電源でプルアップして下さい。

- プロセッサのSPI I/F電圧はiCE40のVCC SPIに合わせるようにして下さい。

- CDONEのプルアップ抵抗値は1/(2\*CCLK周波数\*CDONE外部負荷容量)で算出して下さい。 ※CCLK周波数 = SPI SCKに入力するプロセッサのSPIクロック周波数

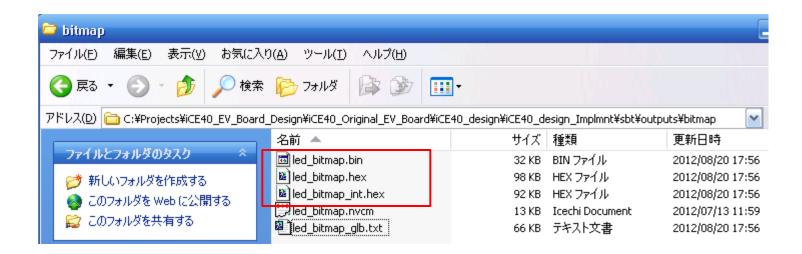

### TecStar コンフィグデータの作成

iCE40のコンフィグデータは設計ツール"iCEcube2"で生成されます。 生成されたコンフィグデータはプロジェクトフォルダ内の以下のフォルダに格納されています。

#### (プロジェクトフォルダ)¥ (プロジェクトフォルダ名)\_Implmnt¥sbt¥outputs¥bitmap

上記フォルダ内に、バイナリ形式(.bin)、HEX形式(.hex)、Intel HEX形式(\_int.hex)でコンフィグデータが生成されますので、お使いのプロセッサが扱いやすいファイルを使い、必要に応じてファイル変換ツール等で変換してお使い下さい。

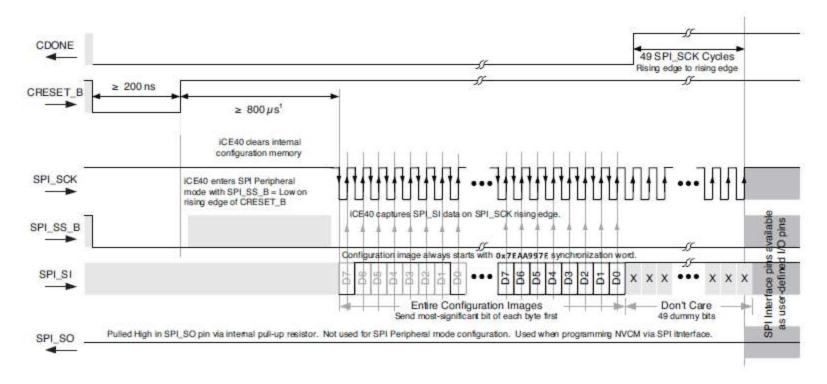

### **Teastal** Slave SPI Configuration通信仕様

Slave SPI Configurationは以下のフローで実施します。

- ①プロセッサからCRESET\_B High -> Low -> High とドライブ(Low期間200ns以上維持)

- ②tCR SCK時間Wait

- ③プロセッサからコンフィグデータ送信

- ④コンフィグ完了後、iCE40からCDONE = High出力

- ⑤CDONE = Highから49Cycle SPI\_SCKを出力続行し、iCE40のI/Oがアクティブ化

#### Tecstal コンフィグデータの送信方法

```

led_bitmap.hex

1|7e aa 99 7e↓

2 51 01↓

3 01 054

4 92 00 204

5 62 01 45↓

6 72 00 904

7 82 00 00↓

8 11 004

9 01 014

16 00 00 00 00 00 04 00 00 00 00 00 10 00 00 00 00 00

```

Configuration Dataは必ず同期ワードの"0x7E AA 99 7E"から始まります。この同期ワードの後、実際の回路データが続きます。

同期ワード含め、コンフィグデータをプロセッサから送信する際には 1Byteずつ、MSBファーストで送信します。

また、コンフィグデータ送信は間欠的ではなく、最初から最後まで データを止めずに送信する必要があります。

After waiting for the configuration memory to clear, the AP sends the configuration image generated by the Diamond Programmer (version 2.0.1 or later). An SPI peripheral mode configuration image must not use the Cold Boot or Warm Boot options. Send the entire configuration image, without interruption, serially to the iCE40's SPI\_SI input on the falling edge of the SPI\_SCK clock input. Once the AP sends the 0x7EAA997E synchronization pattern,

#### **Slave SPI Configurationタイミング規定**

Slave SPI Configurationでは以下のタイミング規定を守る必要があります。

| 3                     | Minimum time from a rising edge                                                                      | iCE40LP384                         | 600  | 74                 |                  | us              |       |                                                     |

|-----------------------|------------------------------------------------------------------------------------------------------|------------------------------------|------|--------------------|------------------|-----------------|-------|-----------------------------------------------------|

| eno.                  | on CRESET_B until the first SPI<br>write operation, first SPI_SCK. Dur-                              | iCE40LP/HX1K                       | 800  | . IS               |                  | us              |       | CRESET_BをLow -> Highと                               |

| t <sub>CR_SCK</sub>   | ing this time, the iCE40 device is                                                                   | iCE40LP/HX4K                       | 1200 |                    |                  | us              | 1 ≻   | 立ち上げてからのWait時間規定                                    |

|                       | clearing its internal configuration memory                                                           | iCE40LP/HX8K                       | 1200 | 29                 | -                | us              | 1     | 立つ上げてからのWall時間が足                                    |

|                       | 8                                                                                                    | Write                              | 1    |                    | 25               | MHz             | 1     |                                                     |

|                       |                                                                                                      | Read<br>iCE40LP384 <sup>2</sup>    |      | 15                 | ā                | MHz             |       |                                                     |

| f <sub>MAX</sub> 1    | CCLK clock frequency                                                                                 | Read iCE40LP/<br>HX1K <sup>2</sup> | 7727 | 15                 | 12               | MHz             |       | プロセッサから出力するSPI_SCK                                  |

|                       |                                                                                                      | Read iCE40LP/<br>HX4K <sup>2</sup> | 127  | 15                 | -                | MHz             |       | の周波数規定                                              |

|                       |                                                                                                      | Read iCE40LP/<br>HX8K <sup>2</sup> | 7065 | 15                 |                  | MHz             |       | プロセッサから出力するSPI SCK                                  |

| t <sub>CCLKH</sub>    | CCLK clock pulse width high                                                                          |                                    | 20   | e <del>i i</del> i | ( ( <del>)</del> | ns              |       | のHigh期間とLow期間規定                                     |

| tcclkl                | CCLK clock pulse width low                                                                           |                                    | 20   | . <del>200</del> 3 | 8==              | ns              |       | _                                                   |

| t <sub>STSU</sub>     | CCLK setup time                                                                                      |                                    | 12   |                    | ( <u>==</u> )    | ns              |       | SPI_SIデータのSPI_SCKに対する                               |

| tstH                  | CCLK hold time                                                                                       |                                    | 12   |                    | 194              | ns              | ا _ [ | Setup/Hold Time                                     |

| tstco                 | CCLK falling edge to valid output                                                                    | 2                                  | 13   | <del>-</del>       |                  | ns              | 1 }   | SPI_SCKがiCE40に入力されてから                               |

|                       | •                                                                                                    |                                    |      |                    |                  | •               |       | データ出力までのTco                                         |

| t <sub>CRESET_B</sub> | Minimum CRESET_B Low pulse width required to restart configuration, from falling edge to rising edge |                                    | 200  | -                  |                  | ns              | }     | CRESET_BのLow維持期間                                    |

| t <sub>DONE_IO</sub>  | Number of configuration clock<br>cycles after CDONE goes High<br>before the PIO pins are activated   | 0 0                                | 49   | 5330               | :===:            | Clock<br>Cycles | }     | CDONE Low -> HighからiCE40 I/O<br>アクティブまでのSPI_SCKサイクル |

# Tecstar コンフィグレーションデータ容量

iCE40シリーズの各デバイスのコンフィグデータ容量は以下の通りです。 Slave SPI Configurationを行う際に、以下の容量のデータを格納できるだけのメモリ容量を確保して下さい。

| Device        | Bytes   | Bits      |

|---------------|---------|-----------|

| iCE40-LP384   | 7872    | 62,976    |

| iCE40-LP/HX1K | 34,112  | 272,896   |

| iCE40-LP/HX4K | 136,448 | 1,091,584 |

| iCE40-LP/HX8K | 136,448 | 1,091,584 |

#### TedStar コンフィグレーション時間について

| t <sub>CRESET_B</sub> | Minimum CRESET_B Low pulse<br>width required to restart configura-<br>tion, from falling edge to rising edge  |                                    | 200  | -    |     | ns              |

|-----------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------|------|------|-----|-----------------|

| t <sub>DONE_IO</sub>  | Number of configuration clock<br>cycles after CDONE goes High<br>before the PIO pins are activated            | 2 S                                | 49   | 5328 |     | Clock<br>Cycles |

|                       | Minimum time from a rising edge                                                                               | iCE40LP384                         | 600  |      | :   | us              |

| t <sub>CR_SCK</sub>   | on CRESET_B until the first SPI<br>write operation, first SPI_SCK. Dur-<br>ing this time, the iCE40 device is | iCE40LP/HX1K                       | 800  |      |     | us              |

|                       |                                                                                                               | iCE40LP/HX4K                       | 1200 |      |     | us              |

|                       | clearing its internal configuration memory                                                                    | iCE40LP/HX8K                       | 1200 | - 2  |     | us              |

| ii                    |                                                                                                               | Write                              | 1    |      | 25  | MHz             |

|                       |                                                                                                               | Read<br>iCE40LP384 <sup>2</sup>    | 23   | 15   | 5   | MHz             |

| f <sub>MAX</sub> 1    | CCLK clock frequency                                                                                          | Read iCE40LP/<br>HX1K <sup>2</sup> | 12/  | 15   | -   | MHz             |

|                       |                                                                                                               | Read iCE40LP/<br>HX4K <sup>2</sup> | 12   | 15   | 25  | MHz             |

|                       |                                                                                                               | Read iCE40LP/<br>HX8K <sup>2</sup> |      | 15   | * - | MHz             |

Slave SPIコンフィグレーションの場合、 HostからSPI\_SCKを供給するため、その クロック周波数に依存したコンフィグ レーション時間になります。

Slave SPIコンフィグレーションの流れは

- ①CRESET\_B High -> Low -> High (Low期間200ns以上維持)

- ②tCR SCK時間Wait

をかけたものになります。

- ③コンフィグデータ送信

- **4**CDONE Low -> High

- ⑤49Cycle SPI\_SCK送信

となっており、上記時間の合計がコンフィグレーション時間になります。 コンフィグデータ送信時間は、SPI\_SCKの 周期にコンフィグデータ容量(4-3項参照)

例えばiCE40LP1Kに対し、SPI\_SCK 10MHz でSlave SPIコンフィグレーションを行う 場合、CRESET\_B = Low出力開始から

200ns + 800us + 100ns x 272896 + 100ns x 49

となります。

### Tecstal Slave SPI Configuration波形サンプル

以下はiCE40HX1Kに対してのSlave SPI Configuration波形サンプルです。

①SPI\_SS\_BとCRESET\_BにLowを出力します。CRESET\_Bは200ns以上(サンプルでは300ns)Lowを維持し、Highに戻します。

| Signal name      | Value | • | 62,00 | • | • | •  | 6400 | •      | • | 66,00 |   |  | 68,00 | • |

|------------------|-------|---|-------|---|---|----|------|--------|---|-------|---|--|-------|---|

| <b>≠</b> CDONE   | 1     |   |       |   |   |    |      |        |   |       |   |  |       |   |

| #CRESET_B        | 1     |   |       |   |   | _[ |      | 300 ns |   |       | _ |  |       |   |

| <b>≖</b> SPI_SCK | 1     |   |       |   |   |    |      |        |   |       |   |  |       |   |

| ≠SPI_SS_B        | 1     |   |       |   |   | l  |      |        |   |       |   |  |       |   |

| ≠SPI_MOSI        | 0     |   |       |   |   |    |      |        |   |       |   |  |       |   |

②CRESET\_BをHighにしてからiCE40HX1KのWait時間800us以上(サンプルでは約1000us) コンフィグデータを送信せずにそのままWaitします。

| Signal name    | Value |  | • | 200 | • | • | 400 |        | •  | 600 | • | • | 800 | • | • | 1000 | • |

|----------------|-------|--|---|-----|---|---|-----|--------|----|-----|---|---|-----|---|---|------|---|

| <b>≖</b> CDONE | 1     |  |   |     |   |   |     |        |    |     |   |   |     |   |   |      |   |

| # CRESET_B     | 1     |  |   |     |   |   |     | 1004.4 | us |     |   |   |     |   |   | 1    |   |

| ■SPI_SCK       | 1     |  |   |     |   |   |     |        |    |     |   |   |     |   |   |      |   |

| #SPI_SS_B      | 1     |  |   |     |   |   |     |        |    |     |   |   |     |   |   |      |   |

| # SPI_MOSI     | 0     |  |   |     |   |   |     |        |    |     |   |   |     |   |   |      |   |

#### **Slave SPI Configuration波形サンプル**

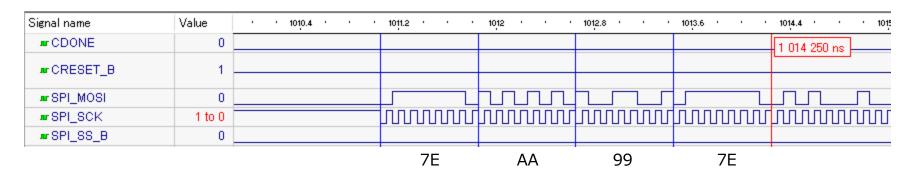

③800us以上Wait後、コンフィグデータを送信します。送信は1ByteずつMSBファーストで送信します。 最初に同期ワード"0x7E AA 99 7E"が現れます。送信データはSPI SCKの立ち上がりエッジで受信されます。

④コンフィグデータ送信完了後iCE40のCDONEがHighになった後、49サイクル以上SPI\_SCKを送信します。 これでSlave SPI Configurationフローは完了です。

| Signal name    | Value  | 30.004 30. | 006 · · · 30.008 · · · 30.01 · · | 30,012        |

|----------------|--------|------------|----------------------------------|---------------|

| <b>≠</b> CDONE | 1      |            |                                  | 30 011 350 ns |

| # CRESET_B     | 1      |            |                                  |               |

| #SPI_SCK       | 1 to 1 |            |                                  |               |

| #SPI_SS_B      | 0 to 1 |            |                                  |               |

| #SPI_MOSI      | 0      |            |                                  |               |

# Tecstar Revision History

| Date       | Revision | Old-page | New-Page | Change information                    | Updated by  |

|------------|----------|----------|----------|---------------------------------------|-------------|

| 2013/3/27  | 1.0      |          |          | First Revision                        | W.Nakatsuka |

| 2013/10/17 | 1.1      | P7, P9   | P7, P9   | コンフィグ関連パラメータの表を更新。                    | W.Nakatsuka |

| 2014/12/15 | 1.2      | P3       | P3       | プロセッサとiCE40の接続図及びCDONEプルアップ抵抗値の記載を更新。 | W.Nakatsuka |

|            |          |          |          |                                       |             |

|            |          |          |          |                                       |             |

|            |          |          |          |                                       |             |

|            |          |          |          |                                       |             |

|            |          |          |          |                                       |             |

|            |          |          |          |                                       |             |

|            |          |          |          |                                       |             |