## 第 8 章 Export Files プロセス

### 8.1 概要

[Export Files] プロセスには、デバイス書き込み用のビットストリーム・ファイル生成および二つのサブプロセスがあります。

#### Bitstream File

FPGA 内のコンフィグレーション SRAM や外付け SPI フラッシュメモリーにコンフィグレーション・データを書く際に使用するビットファイル (\*.bit) です。Nexus シリーズ FPGA では、同時に ”\*.fea” というファイルも生成されます。コンフィグレーション関連ピン (JTAG/PROGRAM/DONE/INIT) のグローバル設定などをフィーチャー行 (Feature Row) に保持します。デバイス制約エディター (DCE) などでデフォルトから変更した場合、\*.fea もプログラムすることが必要です。ただし、フィーチャー行は OTP 構造のため、その場合は十二分の考慮が必要です (第 13.4 節参照)。

#### IBIS Model

インプリメンテーションに使用されている I/O タイプに該当する IBIS モデルのみを抽出して .ibs ファイルとして生成します。”IBIS” という名称のサブフォルダーがインプリメンテーション・フォルダーアー下に生成され、その中に出力されます。インストールされるデバイス・ファミリー毎の IBIS ファイルサイズは非常に大きいですが、ここで出力されるファイルは非常に小さくなります。

#### Gate-Level Simulation File

ゲートレベル・シミュレーション用にネットリストを Verilog HDL 書式に変換して出力します。拡張子は .vo です。同時に遅延ファイル (xxx.vo.sdf) も生成されます。

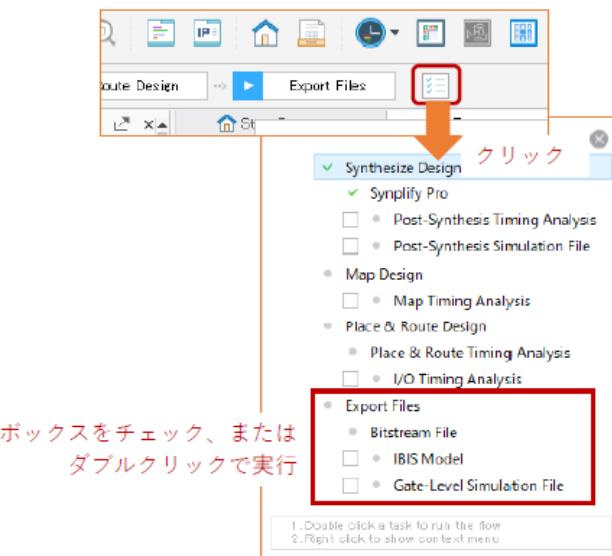

ビットストリーム・ファイル生成以外は、”Task Detail View” アイコンをクリックすると現れるビュー内で (図 8-1) 、該当するサブプロセス行頭のボックスをクリックして有効化してから本プロセスを実行するか、または本プロセス実行後にこれらのサブプロセスのみをダブルクリックして実行します。

図 8-1. サブプロセスの実行

註：本 Lattice Radiant 日本語マニュアルは、日本語による理解のため一助として提供しています。作成にあたっては各トピックについて可能な限り正確を期しておりますが、必ずしも網羅的あるいは最新でない可能性や、オリジナル英語版オンラインヘルプや各種ドキュメントと不一致がある可能性があり得ます。疑義が生じた場合は技術サポート担当者にお問い合わせ頂くか、または最新の英語オリジナル・ソースを参照するようお願い致します。

なお、PAR 実行後にタイミング違反が残っている場合は、デフォルトのストラテジー設定ではウォーニング・メッセージでその旨を通知しますので、適宜対処するようにします。

## 8.2 ストラテジー・オプション設定

### 8.2.1 ストラテジー設定ウィンドウの起動

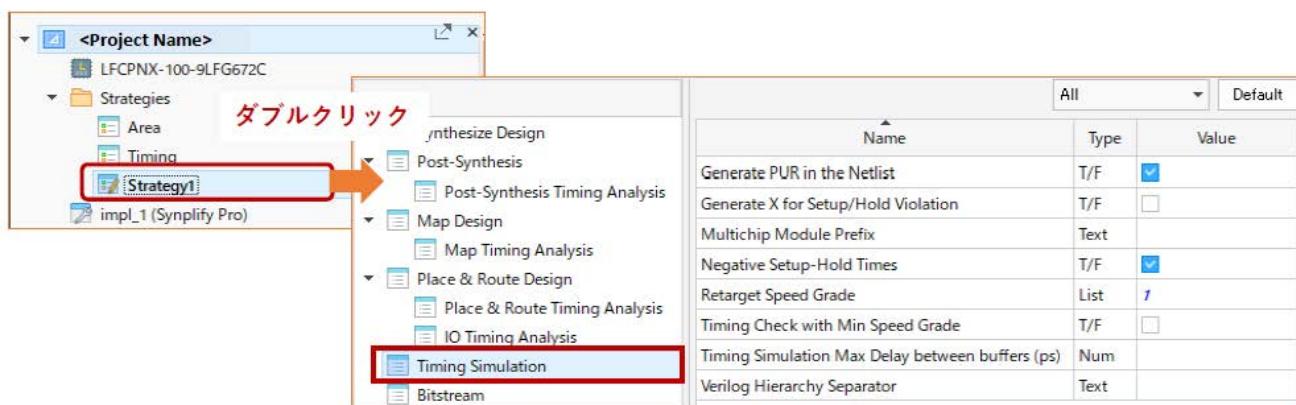

Radiant GUI の ”File List” ビュー最上部は、ストラテジー名のリストが表示されています。太字で表示されているものが、当該インプリメンテーションに有効になっています。ストラテジー名をダブルクリックすると、ストラテジー・オプション設定ウィンドウが開きます（図 8-2）。

プロセスリストで Export Files プロセスに関連するのは [Timing Simulation] と [Bitstream] です。それぞれを選択すると、右側にオプション一式が表示されます。

以下にそれぞれの各ストラテジー・オプションについて記述します。詳細についてはオンラインヘルプで [Reference Guides] → [Strategy Reference Guide] → [Bitstream Options] を選択すると、ご参照いただけます。デバイス・ファミリーによってはサポートされていないオプションもあることにご留意ください。

### 8.2.2 “Timing Simulation” のストラテジー・オプション項目

図 8-2. Timing Simulation/Export Files プロセスのストラテジー・オプション

#### Generate PUR in the Netlist

パラメータ : True / False デフォルト : True

デフォルトではネットリストに ”PUR” を含めます。[False] にした場合は、テストベンチにインスタンスする必要があります。

#### Generate X for Setup/Hold Violation

パラメータ : True / False デフォルト : False

[True] にすると、シミュレーションでフリップフロップのセットアップ / ホールド違反があると ”X” を表示します。

#### Multichip Module Prefix

パラメータ : テキスト デフォルト : ブランク

マルチチップ用途に対応する必要がある場合の接頭語を与えます。

#### Negative Setup-Hold Times

パラメータ : True / False デフォルト : True

論理シミュレーターが負のセットアップ / ホールド時間に対応していない場合は、これを [False] にします。

**Retarget Speed Grade**

パラメータ：リスト

デフォルト：〈プロジェクトでターゲットにしたグレード〉

フィッティングでターゲットにしたネットリストのスピード・グレードと異なるグレードを対象にする場合に指定します。

**Timing Check with Min Speed Grade**

パラメータ：True / False

デフォルト：False

[True] にすると、全パスについて最少タイミングとして出力します。ホールド時間要件の確認のために使用されます。通常のシミュレーションとは異なる実行が必要です。

**Timing Simulation Max Delay between buffers (ps)**

パラメータ：数値

デフォルト：ブランク

信号を分離したりバッファを挿入するなどして配線遅延を分配します。アサインされる遅延値は、各バッファ間の ps 単位での最大遅延です（デフォルトは 1000ps）。

**Verilog Hierarchy Separator**

パラメータ：テキスト

デフォルト：ブランク

Verilog デザインをフラット化する場合の分離文字を指定します。バックスラッシュやピリオドの場合は、"/" や "." のようにダブルクオーテーション・マークで囲みます。

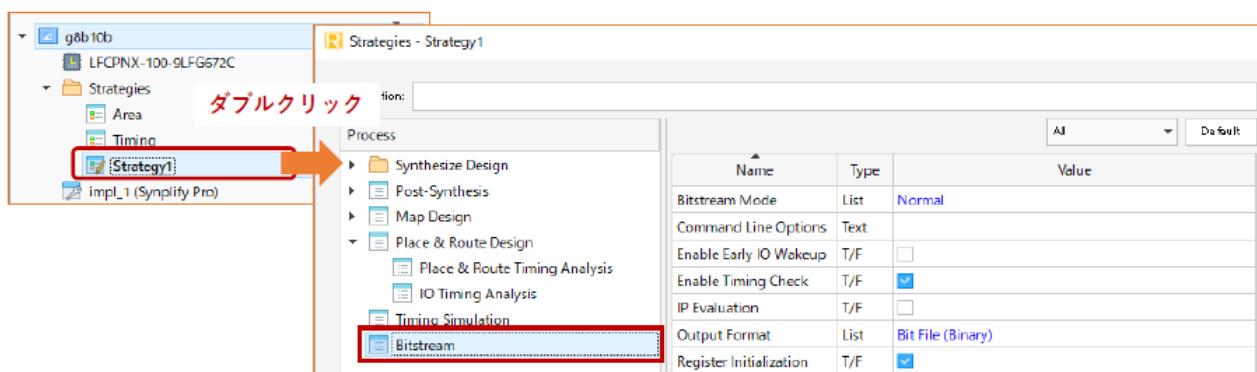

### 8.2.3 “Bitstream” のストラテジー・オプション項目

**図 8-3. Bitstream/Export Files プロセスのストラテジー・オプション****Bitstream Mode**

パラメータ：Normal / Fail Safe デフォルト：Normal

ビットストリーム生成モードです。

**Command Line Options**

パラメータ：文字列

デフォルト：ブランク

規定のオプション以外を使用する場合に、直接引数等を記述します。

**Enable Early IO Wakeup**

パラメータ：True / False

デフォルト：False

**Enable Timing Check**

パラメータ：True / False

デフォルト：True

Export Files 実行時にタイミング・チェックを行うかどうかを設定します。デフォルトはチェックし、エラーがある場合はその旨を小ウィンドウで通知します。[False] にするとチェックは行いません。

### IP Evaluation

パラメータ : True / False

デフォルト : False

デフォルトではインプリメンテーションに何らかの IP が実装されている場合に、ライセンスがないとエラーで処理を停止します。[True] にすると、IP ライセンスを入手前などの機能評価目的のため、期限付きのビットストリーム・ファイルを生成します。

なお、この場合セキュリティ設定ツールでの設定有無に関わらず、ビットストリーム・ファイルは暗号化されます。

### Output Format

パラメータ : Bit File (Binary) / Raw Bit File (ASCII)

デフォルト : Bit File (Binary)

ビットファイルのフォーマット設定で、[Bit File (Binary)] はバイナリ形式のファイル (\*.bit) が、[Raw Bit File (ASCII)] はテキスト形式のファイル (\*.rbt) が生成されます。どちらもプログラマーでの書き込みに使用できます。

### Register Initialization

パラメータ : True / False

デフォルト : True

ビットストリームのレジスター初期化セクションをイネーブルします。

## 8.3 Export Files プロセス・レポート

[Export Files] プロセスを実行すると、レポート・ビューに結果がレポートされます。GUI 上部の [Reports] タブをクリックし、ウィンドウ左側のセクションで [Export Reports] をクリックすると、サブ項目として [Bitstream] と [IBIS Model] の二つがあります。プロセス・レポートは前者であり、主にコンフィグレーション関連の属性のサマリー (Preference Summary) がレポートされます。

図 8-4. Export Files のプロセス・レポート (一部)

The screenshot shows the Lattice Radiant software interface. On the left, there is a sidebar titled 'Reports' with several sections: 'Project Summary', 'Synthesis Reports', 'Map Reports', 'Place & Route Reports', 'Export Reports' (which is expanded), and 'IBIS Model' and 'Misc Reports'. A red box highlights the 'Bitstream' section under 'Export Reports', and an orange arrow points from this box to the main content area. The main content area is titled 'Bitstream' and contains two parts: a log of the bitstream generation process and a 'Preference Summary' table.

**Bitstream Log:**

```

BITGEN: Bitstream Generator Radiant Software (64-bit) 3.1.1.232.1

Copyright (c) 1991-1994 by NeoCAD Inc. All rights reserved.

Copyright (c) 1995-2001 AT&T Corp. All rights reserved.

Copyright (c) 1995-2001 Lucent Technologies Inc. All rights reserved.

Copyright (c) 2001 Agere Systems All rights reserved.

Copyright (c) 2002-2021 Lattice Semiconductor Corporation, All rights reserved.

Mon May  9 18:42:20 2022

```

Command: bitgen -w -g REGISTER\_INIT:ON -ipeval -s C:/usr\_ss/cathandsOct182021/L

WARNING - The IP core used in the design supports Hardware Evaluation Capability

Running DRC.

WARNING - Disconnected tail of routing path on signal pll\_lock from driver R72C1

DRC detected 0 errors and 1 warnings.

**Preference Summary:**

| Preference       | Current Setting |

|------------------|-----------------|

| EARLY_IO_RELEASE | ON              |

| REGISTER_INIT    | ON**            |

| SLAVE_SPI_PORT   | DISABLE**       |

| SLAVE_I2C_PORT   | DISABLE**       |

| SLAVE_I3C_PORT   | DISABLE**       |

[IBIS Model] レポートはデフォルトでは 印になっていて、有効なレポートが閲覧できる状態ではありません。サブプロセスを実行すると、インプリメンテーション・フォルダ下にサブフォルダ “IBIS” が作成され、デザインで使用されている I/O タイプのみについての IBIS モデルが抽出されて \*.ibs ファイルとして生成されます。レポート・ビューで閲覧できるのは、この \*.ibs ファイルそのものです。

なお、ハード IP に接続される I/O ピンについては \*.ibs ファイルに書き出されません。特に MIPI 関連ピンについては以下のようにバッファタイプが定義されています。またレシーバの差動終端抵抗は、(一部アミリー・デバイスについてはドキュメント記述と不一致で) IBIS モデルには含まれていませんので、シミュレーション時のトポロジーとして付加する必要があることにご留意ください。

|                         |                                                  |

|-------------------------|--------------------------------------------------|

| Soft D-PHY Rx ピン        | 1073 mip120axxxeaaaabain mip120axxxeaaaabain     |

| Soft D-PHY Tx ピン        | 1147 mip120a020eaaaaabbio mip120a020eaaaaabbio   |

| Hard D-PHY Rx ピン        | 1196 mip120axxxaaaahaaain mip120axxxaaaahaaain   |

| Hard D-PHY Tx ピン、HS モード | 1197 mip120axxxaaaahaaop mip120axxxaaaahaaou     |

| Hard D-PHY Tx ピン、HS モード | 1198 mip120axxxaaaahaaon mip120axxxaaaahaaou     |

| Hard D-PHY Rx ピン、LP モード | 1199 mip120axxxaaaalaaaain mip120axxxaaaalaaaain |

| Hard D-PHY Tx ピン、LP モード | 1200 mip120axxxaaaalaaaou mip120axxxaaaalaaaou   |

## 更 新 履 歴

| リビジョン    | ページ | 内 容                                          |

|----------|-----|----------------------------------------------|

| 2022.1   | 2   | Rev.3.2.1 からのバージョン・アップに伴い、ストラテジー・オプションについて更新 |

|          | 2-3 | 同、Timing Simulationストラテジー・オプションについて追加        |

|          | 4   | 同、IBISモデルについての記述を加筆                          |

| (r1)     | 4-5 | IBISモデル書き出しについて、特にMIPIについて追加                 |

| 2023.2.1 | --  | Radiant 2023.2バージョン・アップに伴い、一部図の更新            |

|          |     |                                              |

---- \*\*\* ----