## ECP2/ECP2M ユーザーズガイド

# TecStar はじめに

- 本資料は、Lattice社 ECP2/ECP2Mの基板設計時の注意事項、使用時の注意事項をまとめたものです。実際の動作等詳細、最終の確認は、別途データシートを参照頂けるようお願い申し上げます。

- Lattice社データシートと本資料との間に差異があった場合には、 Lattice社データシートを正としお取り扱い下さい。

# TecStar 目次

| ECP2/M保有ピンの機能説明・ピン処理について       |     | ECP2/Mのコンフィグレーション専用ヒン詳細説明          |                 |

|--------------------------------|-----|------------------------------------|-----------------|

| 1-1 電源ピン                       | P5  | 4-1 コンフィグレーション専用ピン詳細説明             | P4:             |

| 1-2 コンフィグ関連ピン                  | P12 | 4-2 JTAGピン                         | P5′             |

| 1-3 クロック専用ピン、PLL専用ピン           | P16 |                                    |                 |

| 1-4 その他のピン                     | P19 | ECP2/Mのコンフィグレーションフロー               |                 |

| 1-5 Serdes信号ピン(ECP2Mのみ)        | P20 |                                    |                 |

| ,                              |     | 5-1 コンフィグレーションフロー(全体)              | P53             |

| ECP2/MのI/O Bankの概念及び汎用I/Oについて  |     | 5-2 Initializeシーケンス(電源ON時)         | P54             |

|                                |     | 5-3 Initializeシーケンス(Programnピン)    | P55             |

| 2-1 I/O Bankの構成                | P22 | 5-4 コンフィグレーションシーケンス                | P56             |

| 2-2 対応可能なI/OのI/F一覧             | P23 | 5-5 Wake Up(コンフィグレーション完了後のデバイスの起動) | P57             |

| 2-3 サポートする標準入力I/Fについて          | P24 | 5-6 WakeUpシーケンス                    | P58             |

| 2-4 ドライブ能力について                 | P25 | 5-7 WakeUp <b>タイムチャー</b> ト         | P59             |

| 2-5 差動LVDS I/F対応について           | P26 | ·                                  |                 |

| 2-6 その他差動 I/Fについて              | P29 | ECP2/MのSPI-Flash,Serial-ROMについて    |                 |

| 2-7 GearingBox使用時の注意点          | P31 |                                    |                 |

| 2-8 電源ON時のI/Oの挙動について           | P32 | 6-1 コンフィグレーションビットサイズ一覧             | P6 <sup>-</sup> |

|                                |     | 6-2 SPI Serial Flash Vendor List   | P62             |

| ECP2/Mのコンフィグレーションについて          |     |                                    |                 |

|                                |     | ispVMsystemを使用したECP2/Mへの書込みについて    |                 |

| 3-1 コンフィグレーションモードについて          | P34 |                                    |                 |

| 3-2 コンフィグレーションモード選択            | P35 | 7-1 ispVM Systemでのコンフィグデータの書き込み    | P64             |

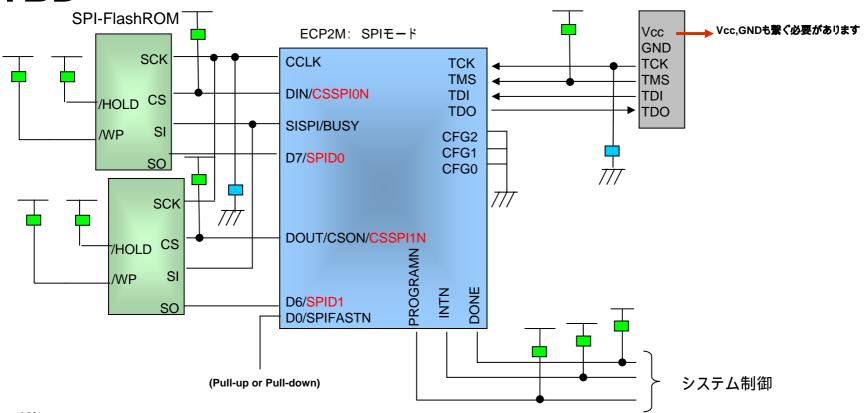

| 3-3 SPIモード詳細(1Flash+1FPGAの場合)  | P36 | 7-2 Bitstreamの圧縮、マージについて           | P69             |

| 3-4 SPIモード詳細 (1Flash+2FPGAの場合) | P37 | 7-3 デュアルプートについて                    | P7′             |

| 3-5 SPImモード詳細                  | P38 |                                    |                 |

| 3-6 SPIモード カスケード方式の詳細          | P40 |                                    |                 |

| 3-7 Slaveシリアルモード詳細             | P41 |                                    |                 |

| 3-8 Slaveパラレルモード詳細             | P42 |                                    |                 |

| 3-9 JTAGモード詳細                  | P43 |                                    |                 |

## ECP2/M保有ピンの機能説明・ピン処理について

| ピン名                 | 電圧                 | 備考                                                                                                                                                                       |

|---------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vcc                 | 1.2V               | 1.2V電源。コア用                                                                                                                                                               |

| Vccaux              | 3.3V               | 3.3V電源。参照電圧を用いる差動入力パッファを動作させるための補助電源です。コンフィグレーション用の電圧としても使われます。                                                                                                          |

| Vccio(0-8)          | 1.2V/2.5V/<br>3.3V | 各バンク毎に用意されています。バンク毎にそこで使用するインターフェースによって、印加する電源を決定します。使用しないBankについても必ず1.2V,2.5V,3.3Vを印加してください。Vccioが3.3Vの場合、Vccauxと同じ電源を使用することを推奨します。(Vccio8は可能な限りVccauxと繋げて使用するようにして下さい) |

| Vccpll              | 1.2V               | PLL用の電源。使用しない場合でも1.2Vを印加してください。Vccと同電源でつなぐことを推奨します。(Vccと同じ電源を使用することを推奨します)                                                                                               |

| VREF1_x,<br>VREF2_x |                    | リファレンス電圧が必要なインターフェース(HSTL等)を使用したときに入力します。各パンクで2種類のVREF(VREF1/VREF2)を設定できます。(例外: Bank3,8のVrefは共通)使用しないときはI/Oとして使用可能ですただし、DDRメモリI/Fを使用する場合はVREF1を使用してください                  |

| Vccj                | 1.2V/2.5V/<br>3.3V | VCCJはLVCMOS JTAGピンの特性を決定します。つまり、JTAGピンの電源となります(VCCIOからは独立しています)3.3Vを繋ぐ場合はVccauxと繋ぐことを推奨します。                                                                              |

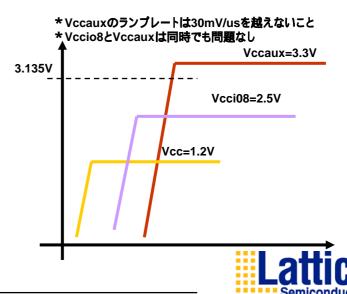

### 【重要】電源ピンの取り扱いに関する注意事項

- 電源投入時の確実なコンフィグレーションの為に、Vccio8電圧(Bank8用電源)はVcc、Vccaux電源のうち、最後に最小電圧(Vccの場合1.14V、Vccauxの場合3.135V)に達する電源とのシーケンスを考慮する必要があります。 もし、VccよりもVccauxが最後に最小電圧に達する場合、Vccio8はVccauxと同時、或いはそれより先に最小電圧に達する必要があります。又、逆にVccauxよりもVccが最後に最小電圧に達する場合にはVccio8はVccと同時、或いはそれより先に最小電圧に達する必要があります。\* Vccio8(BANK8用電源)とVccauxが同じ3.3Vで繋がれている場合は上記を気にする必要はありません。

- Vccauxが0~3.3Vに立ち上がる際のランプレートは、30mV/usを越えないように電源設計する必要があります(次ページの一覧をご覧下さい)

- Vccio 8 以外(Vccio 0-Vccio 7)はVccやVccauxより先に供給する、或いはVcc,Vccauxと同時に供給することを推奨します。

- Vccio8Bankに存在するConfigration専用ピン(PROGRAMN,INIT,DONE等)のPull-up用電源はVccaux,Vccio8と共通に するようにして下さい。

- 確実なコンフィグレーションを行う為に、電源ON後PROGRAMNピンをトグルして使用することを推奨します。(この方法であれば、電源シーケンス、電源立ち上がり時間等を考慮する必要は全くなくなります)

- <u>その他につきましては次ページの一覧をご参照下さい</u>

(注意)暗号化(Encription)対応のデバイス(ECP2M"S"version)を使用する場合は以下についても考慮が必要です。

PowerUp時、VccauxはVccが<u>最小電圧(1.14V)になった後</u>に0Vから立ち上げ始める必要があります。

\*ECP2M"S"Version以外のデバイスにつきましては上記は無視して構いません。

| 項目                                    | 適用                      | 規定値                              | 条件                                                   | コメント                                           |  |

|---------------------------------------|-------------------------|----------------------------------|------------------------------------------------------|------------------------------------------------|--|

| 電源立ち上がり時間                             | Vcc(1.2V)               | 100us-100msの範囲                   | 0から1.26Vまでに達する時間                                     | 単調増加で立ち上がる必                                    |  |

| (RT:Ramp Time<br>RR:Ramp Rate)        | Vccaux(3.3V)            | RT:100us-100msの範囲                | 0か63.465Vまでに達する時間(Linear<br>Ramp Rate)               | 要あり                                            |  |

|                                       |                         | RR:30mV/uS                       | 0.5V ~ (Non-Linear Ramp Rate)                        |                                                |  |

|                                       | Vccio,Vref,Vccj         | 100us-100msの範囲                   | 0から仕様max値に達する時間                                      |                                                |  |

| パワーオンリセット電圧値(POR)                     | Vccの立上がり<br>(POR = On)  | 1.0V                             | RTが上記規定値に入っていること                                     | 左は最悪値を示す。                                      |  |

|                                       | Vccの立下り<br>(POR=Off)    | 0.65V                            |                                                      | Vcc,Vccauxが共に規定値以上<br>になるとPORは開放される<br>(OFF)   |  |

|                                       | Vccauxの立上がり<br>(POR=On) | 2.90V                            |                                                      |                                                |  |

|                                       | Vccauxの立下り<br>(POR=Off) | 1.50V                            |                                                      |                                                |  |

| 電源投入時残留電圧値                            | Vcc,Vccaux              | Vcc=<0.30VかつVccaux=<1.0V         |                                                      | 意図せずPORがトリガされない<br>ようにする為にはPOR電圧値以<br>上を保持すること |  |

| コンフィグデータ保持電圧                          | Vcc, Vccaux             | Vcc>=1.0VかつVccaux>=2.9V          | ・PROGRAMNをPull-upし、Vcc以下にならないこと ・Vccio8がVcc以下にならないこと |                                                |  |

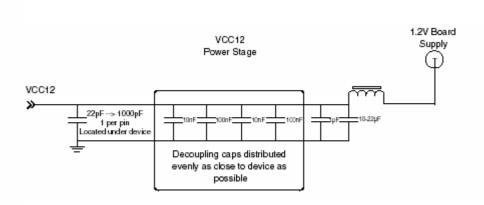

| デカップリング容量推奨値<br>Vcc,Vccaux,Vccj,Vccio |                         | 0.01uFを各PLL電下ピンの極力近<br>〈に配置      |                                                      |                                                |  |

|                                       |                         | 10uF、又はそれ以上を各電源ラインのデバイス近傍へ配置     |                                                      |                                                |  |

| *                                     |                         | 0.1uFを各電源ピン極力近くに配置<br>(チップコンデンサ) | 薛                                                    |                                                |  |

|                                       |                         |                                  |                                                      |                                                |  |

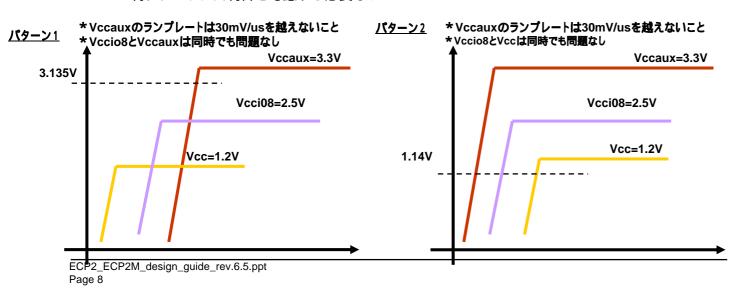

### 電源ピンのシーケンス制御まとめ(暗号化を使用しない場合)

- 1. Vccaux, Vccio8を共通電源で使用している場合

- ·PowerUp時

特にシーケンス制御を考慮する必要なし

·PowerDown時

特にシーケンス制御を考慮する必要なし

- 2. Vccaux,Vccio8を別電源で使用している場合 (基本的にはVccio8はVccauxと同じ電源でお使いください)

- ·PowerUp時

パターン1: VccよりもVccauxが最後に最小電圧に達する場合、Vccio8はVccauxと同時、或いは、それより先に最小電圧に達する必要があります。 パターン2: VccauxよりもVccが最後に最小電圧に達する場合にはVccio8はVccと同時、或いはそれより先に最小電圧に達する必要があります。

·PowerDown時

特にシーケンス制御を考慮する必要なし

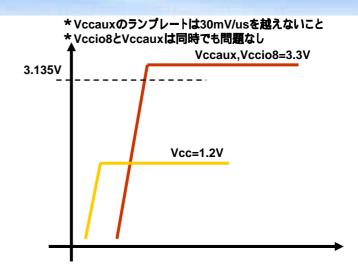

## 電源ピンのシーケンス制御まとめ (暗号化を使用する場合(ECP2M"S"Versionを使用)

- 1. Vccaux, Vccio8を共通電源で使用している場合

- ·PowerUp時

Vccを一番最初に起動 Vccaux,Vccio8を起動

·PowerDown時

特にシーケンス制御を考慮する必要なし

- 2. Vccaux,Vccio8を別電源で使用している場合 (基本的にはVccio8はVccauxと同じ電源でお使いください)

- ·PowerUp時

Vccを一番最初に起動 Vccio8を起動後Vccauxを立ち上げる、 もしくはVccio8とVccauxを同時に起動

·PowerDown時

特にシーケンス制御を考慮する必要なし

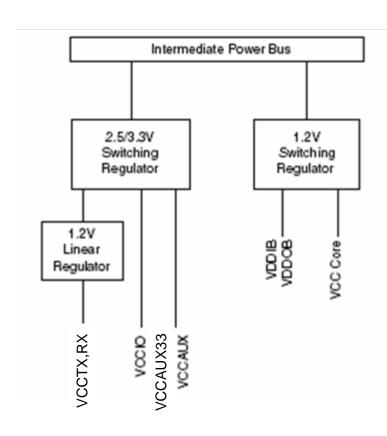

### Serdes周りの電源ピン仕様

| ピン名             | 電圧        | 備考                                                                    |

|-----------------|-----------|-----------------------------------------------------------------------|

| xxx_SQ_VCCAUX33 | 3.3V      | 内部Termination用の電源。(使用しない場合も電圧を供給しておいて下さい。)                            |

| xxx_SQ_VCCP     | 1.2V      | PLL,Referenceクロックバッファー用電源。(使用しない場合も電圧を供給しておいて下さい)                     |

| xxx_SQ_VCCIBm   | 1.2V/1.5V | Channel m用のRXバッファ用電源(使用しない場合、Openにしておいてください)                          |

| xxx_SQ_VCCOBm   | 1.2V/1.5V | Channel m用のTXバッファ用電源(使用しない場合、Openにしておいてください)                          |

| xxx_SQ_VCCTXm   | 1.2V      | 高速mチャネルトランスミッター用アナログ電源(使用しない場合も電<br>圧を供給しておいて下さい)ノイズが小さくなるよう考慮してください。 |

| xxx_SQ_VCCRXm   | 1.2V      | 高速mチャネルレシーバ用アナログ電源(使用しない場合も電圧を供給しておいて下さい)ノイズが小さくなるよう考慮してください。         |

前ページに記載したVCCIB,VCCOB等の電源はSERDESの特性に大きく影響いたします。電源を分離して考える、ノイズの影響を抑えるようフィルターをつける等、できるだけ注意を払うよう注意してください。 (以下、Lattice社ApplicationノートTN1114より抜粋)

| ピン名                          | I/Otype(コンフィグ時) | PinType       | コンフィグモード(*1)               | 備考                                                      |

|------------------------------|-----------------|---------------|----------------------------|---------------------------------------------------------|

| CFG[2:0]                     | 入力              | 専用            | 全て                         | 内部Pullup有効                                              |

| PROGRAMN                     | 入力              | 専用            | 全て                         | 内部Pullup有効                                              |

| INITN                        | 双方向             | 専用            | 全て                         | 内部Pullup有効                                              |

| DONE                         | 双方向             | 専用            | 全て                         | 内部Pullup設定は、DonePinプリファレンスにて指定。<br>(デフォルト、常時内部Pullup有効) |

| CCLK                         | 入力or出力          | 専用            | SPIm,SPI =出力、<br>SLAVE =入力 | 内部Pullup有効                                              |

| DI/CSSPI0N                   | 入力              | I/O or 専用(*2) | シリアJレ/SPI/SPIm             | 内部Pullup有効                                              |

| DOUT/CSON (ECP2)             | 出力              | I/O or 専用(*2) | シリアル/パラレル<br>/SPI          | 内部Pullup有効                                              |

| DOUT/CSON/CSSPI1N<br>(ECP2M) | 出力              | I/O or 専用(*2) | シリアル/パラレル<br>/SPI/SPIm     | 内部Pullup有効                                              |

| CSN                          | 入力              | I/O or 専用(*2) | パラレル                       | 内部Pullup有効                                              |

| CS1N                         | 入力              | I/O or 専用(*2) | パラレル                       | 内部Pullup有効                                              |

| WRITEN                       | 入力              | I/O or 専用(*2) | パラレル                       | 内部Pullup有効                                              |

| BUSY/SISPI                   | 出力orHi-z        | I/O or 専用(*2) | パラレル/SPI                   | 内部Pullup有効                                              |

| D[0]/SPIFASTN                | 入力or出力          | I/O or 専用(*2) | パラレル/SPI/SPIm              | 内部Pullup有効                                              |

| D[1:5]                       | 入力or出力          | I/O or 専用(*2) | パラレル                       | 内部Pullup有効                                              |

| D[6]/SPID1                   | 入力or出力          | I/O or 専用(*2) | パラレJレ/SPOm                 | 内部Pullup有効                                              |

| D[7]/SPID0                   | 入力or出力          | I/O or 専用(*2) | パラレル/SPI/SPIm              | 内部Pullup有効                                              |

| TDI                          | 入力              | 専用            | ispJTAG                    | 内部Pullup有効                                              |

| TDO                          | 出力              | 専用            | ispJTAG                    |                                                         |

| TCK                          | 入力              | 専用            | ispJTAG                    | 外部2.2K でPull-down                                       |

| TMS                          | 入力              | 専用            | ispJTAG                    | 内部Pullup有効                                              |

| XRES                         |                 | 専用            |                            | 10K 精度±1%の抵抗でPull-Down処理 <mark>が必要</mark>               |

(\*1) コンフィグモード = SPI、SPIm,スレーブシリ アル、スレーブパラレル

(\*2) コンフィグ完了後に ユーザーI/Oとして使用で きます。ただしECP2M50、 ECP2M70、ECP2M100 に関してはコンフィグ完了 後も専用ピンのままとなり ユーザーI/Oにはなりませ んのでご注意ください。

コンフィグレーション選択ピンCFG[2:0](後述)を以下のように設定することで、各種コンフィグレーションモードを決定します。 コンフィグモードの詳細は3.ECP2/Mのコンフィグレーションの項目をご覧下さい。

| モード     |               | CFG[2] | CFG[1] | CFG[0] | D[0]/SPIFASTN | 備考                    |

|---------|---------------|--------|--------|--------|---------------|-----------------------|

| SPI3    | Normal (0x03) | 0      | 0      | 0      | PULL-UP       |                       |

|         | Fast (0x0B)   | 0      | 0      | 0      | PULL-DOWN     | SPIフラッシュがサポートしている必要あり |

| SPIm N  | Normal (0x03) | 0      | 1      | 0      | PULL-UP       |                       |

|         | Fast (0x0B)   | 0      | 1      | 0      | PULL-DOWN     | SPIフラッシュがサポートしている必要あり |

| Slave S | erial         | 1      | 0      | 1      | X             |                       |

| Slave P | arallel       | 1      | 1      | 1      | x             |                       |

| ispJTAG |               | x      | x      | х      | D[0]          | CFG[2:0]の設定によらず、常に有効  |

〔注意〕Slave Parallelに関しては144pin,208pin TQFPはサポートしておりません

## 【重要】コンフィグ関連ピンの取り扱いに関する注意事項(ECP2/M共通)

・前ページにおけるI/Oとコンフィグレーション専用ピン両方の機能を持つピンをDual-Purposeピンと呼びます。これらのピンがコンフィグレーション用に用いられると、デフォルト設定ではコンフィグレーション後にI/Oとして利用できます。コンフィグレーション専用ピンとして使用し、コンフィグレーション後にI/Oとして使用できなくする場合は、ispLEVERのPre-Map Preference Editorを開き、Globalタブにある"PERSISTENT"オプションをONに設定してください。設定をONにした場合はコンフィグレーション後に、これらのピンはトライステートになり弱くプルアップされます。

ただしECP2M50、ECP2M70およびECP2M100に関してはDual-Purpose機能がありません。すべてのコンフィグ関連ピンは専用ピンとなり、コンフィグレーション完了後もユーザーI/Oとして使用できないのでご注意〈ださい。

- ・DOUT信号はコンフィグレーション中出力ピンとなります。もし、このピンをUser I/Oとして使用する場合には信号の衝突を回避する為に、出力ピンとして使用することを推奨します。

- ・BANK8はコンフィグ関連のピンがまとまっております。必ず、Vccio8には3.3Vを印加して下さい。

- ・電源立ち上がり中のDoneピンの挙動は安定しない為、コンフィグレーションが終了したかどうかをCPU等に認識させるシステムを構成する場合には、電源が立ち上がり安定した後にDoneピンがHighとなっていることを確認してください。

- ・PROGRAMN,DONE,INITはコンフィグレーションの挙動に深〈影響を与えます。後半ページの参考コンフィグレーション回路をご覧いただき、慎重に扱って〈 ださい。

- 又、PROGRAMNはコンフィグ失敗時や、コンフィグレーションシーケンスから抜け出せないようなイレギュラーな現象が起こった場合にトグルすることでFPGA を初期化し、再コンフィグレーション行なうことができます。CPUに接続して管理、制御できるようにしておくことを推奨します。DONE,INITに関しましてはコンフィグレーションの状態を確認できます。LEDを接続しておくことでデバック時にとても有効です。

- ·XRESピンには必ず10K ±1%の抵抗で外部Pull-down処理してください。しない場合、コンフィグレーション動作に支障をきたす可能性がございます。

- ・D[0]/SPIFASTはお使いになるSPI-FLASHが高速読み出しをサポートしているかどうかを確認頂いた上で、Pull-down,Pull-up処理を行なって〈ださい。

- ·Slave Parallelに関しては144pin,208pin TQFPはサポートしておりません

## 【重要】コンフィグ関連ピンの取り扱いに関する注意事項(ECP2Mのみ)

- ・ECP2MについてはSPI,SPImモードにおけるデイジーチェイン方式でのコンフィグレーションに対応しています。 (SPI-Flashを2つチェーン接続して使用できます。詳細は本資料のコンフィグレーションの項目をご覧下さい)

- ・もし、上記方式でのコンフィグレーションを行なわない場合にはD[6]/SPID1ピンは、NC或いはHigh固定にしてください。もし、このピンをUser I/Oとして使用する場合にはOutputピンとして使用することを推奨します。

- ·DOUT/CSON/CSSPI1Nピンに関してはコンフィグレーション中、出力ピンとなります。もし、Userl/Oとして使用する場合にはOutputピンとして使用することを推奨します。

## Tecstar 1-3 クロック専用ピン、PLL専用ピン

| ピン名                        | 説明                                                                  |

|----------------------------|---------------------------------------------------------------------|

| [LOC][num]_GPLL[T, C]_IN_A | GPLLへのクロック入力ピン。PLL未使用時は通常I/Oとして使用可能.                                |

| [LOC][num]_GPLL[T, C]_FB_A | GPLLへのフィードバック入力ピン。PLL未使用時は通常I/Oとして使用可能                              |

| [LOC][num]_SPLL[T, C]_IN_A | SPLLへのクロック入力ピン。PLL未使用時は通常I/Oとして使用可能                                 |

| [LOC][num]_SPLL[T, C]_FB_A | SPLLへのフィードバック入力ピン。PLL未使用時は通常I/Oとして使用可能                              |

| [LOC][num]_DLL[T, C]_IN_A  | DLLへのクロック入力ピン。 DLL未使用時は通常I/Oとして使用可能                                 |

| [LOC][num]_DLL[T, C]_FB_A  | DLLへのフィードバック入力ピン。DLL未使用時は通常I/Oとして使用可能                               |

| Xxx_PLLCAP                 | 内部VCO周波数可変用専用ピン。(Right,Leftサイドに1ピンづつ備わっている)<br>使用しない場合はOpenで問題ありません |

| PCLK[T,C]_[n:0]_[3:0]      | Globalクロック入力ピン。クロックピンとして使用しない場合、通常I/Oとして使用可能                        |

上記のピンは未使用時はOPENで構いません

[LOC] ・・PLLのロケーション(ULM、LLM、URM、LRM)

··T(True)、C(Complement) 差動のP/N [T/C] [Edge] ··L(Left), B (Bottom), R (Right), T (Top)

[Row/Column] ··行または列の番号

··I/Oセル(PIC)のうちどちらのI/O(PIO)を使っているか [A/B]

# TecStar 1-3 クロック専用ピン、PLL専用ピン

## クロックピンの取り扱いに関する注意事項

- クロックピン、PLLピンについてシングルエンド入力で使用する場合にはT(True),C(Complemen)の**T側**を使用するようにして下さい。(この場合、C側はUserI/Oとして使用できます。クロックピンとしては使用できません)

- クロック信号は必ずクロックピンに入力するようにしてください。I/Oから入力も可能ですが、内部専用クロックラインに乗せるまでの遅延が生じます。(クロックピンから内部専用クロックラインまでのパスは最小遅延になります)

- 基板設計時、PLLを使用するかどうか判断に迷った場合には、PLL専用ピン、クロックピン両方にクロック信号を供給しておくことを推奨します。 (使わない方のピンはパターンがつながっていても特に問題はありません)

# TecStar 1-3 クロック専用ピン、PLL専用ピン

## PLL専用ピンの取り扱いに関する注意事項

- クロックピン、PLLピンについてシングルエンド入力で使用する場合にはT(True),C(Complemen)のT側を使用するようにして下さい。(この場合、C側はUserl/Oとして使用できます。)

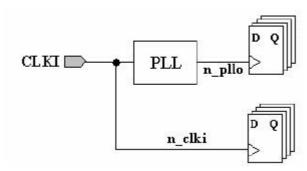

- 下記のようなデザインの場合、n\_clkiを内部専用クロック配線に乗せることができなくなります。ツール上では n\_clkiを内部専用クロック配線に乗せてもエラーにはなりませんが、n\_clkiがPLLの入力に入る形に展開されてしまいます。つまり、一度中央の内部専用クロック配線を経由してからPLLにn\_clkiが入る形になるので、その分遅 延が生じてしまいます。もし、Tco改善のため、このようなデザインを考えた場合には上記の様にPLL入力までの 遅延がかさむ為、逆にTcoが遅くなってしまうことが考えられます。このような場合には、CLKIをPLL専用ピンとクロック専用ピンに入力してあげることで回避することができます。

- PLLCAPに外部キャパシターを接続することでPLLの内部VCOのレンジを変化させることができ、結果出力周波数レンジを変えることができます。但し、このPLLCAPを使用した場合、同一サイドのPLL(GPLL,SPLL)のうちつのPLLは使用できなくなります。(つまり、片側2つのPLLのうち1つしか使えなくなります)

- \*詳細はApplication/ートTN1103参照

# TecStar 1-4 その他のピン

| ピン名           | 説明                                                                                                      |

|---------------|---------------------------------------------------------------------------------------------------------|

| GSRN          | Global RESETピン。(通常I/Oと兼用。)全ての通常I/OはGlobal RESETとして使用可能。特にこの<br>ピンからリセットを入れなければいけないわけではない。未使用時はオープンでOK。. |

| [LOC]DQS[num] | DDR1/2 I/Fで使用するためのDQS信号ピン。(TOPサイドにはDQSは存在しないので注意)                                                       |

- GSRNは基本的には論理合成時に自動で割り当てられます。但し、自動で割り当てられる条件があり、 Distributed-Ramを含む全てのFFの初期化信号であることが条件になります。もし、うま〈GSRNに割り当てられない場合には、ソース中にGSRNマクロブロックを明示する必要があります。

- GSRNに割り当てられたかどうかの確認はPlace & Route ReportのDevice utilization summaryの項目中をご覧下さい。割り当てられた信号がRSTという信号だった場合以下のように記載されます。

- Signal RST is selected as Global Set/Reset

# TecStar 1-5 Serdes信号ピン(ECP2Mのみ)

| ピン名               | 説明<br>· · · · · · · · · · · · · · · · · · ·       |

|-------------------|---------------------------------------------------|

| xxx_SQ_REFCLKP(N) | Serdes用のCMLリファレンスクロック入力ピン。使用しない場合、Openのままで問題ありません |

| xxx_SQ_HDOUTP(N)  | 高速mチャネルCMLバッファOutput。                             |

| xxx_SQ_HDINP(N)   | 高速mチャネルCMLバッファInput。                              |

## ECP2/MのI/O Bankの概念及び汎用I/Oについて

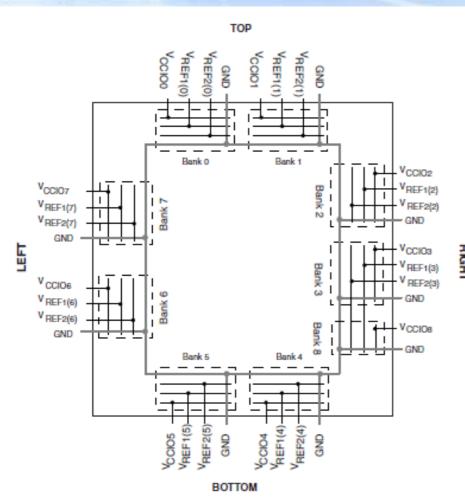

# TecStar 2-1 I/O Bankの構成

- LatticeECP2デバイスには、左図のように各辺の2バンクに加え、バンク3に隣接するバンク8の合計9つのIOバンクがあります。IOバンク0~7は、1つのVCCIO、2つの参照電圧(VREF1、およびVREF2)を持っています。バンク8の参照電圧はバンク3と共用します。

- 下辺のバンク(バンク4,5)のみクランプダイオード付 PCI入力をサポートします。

( ECP2Mは左辺と下辺のバンクがクランプダイオード付PCI入力をサポートしています。)

- TOPバンクは単純な入力レジスタしか用意されておらず、DDR用DQS,或いはGearBoxがありません。又、TQFPパッケージではDDRメモリI/Fは繋げることはできません(DDRレジスタは使用可能です)

- 左右のバンク(8を除く2,3,6,7)の50%のみ真のLVDS 出力ができます。但しそれ以外のバンクにおいても外 部コンポーネントにより、LVDS、LVPECL等のエミュ レーションは可能です。

- LVDS入力に関しては全てのバンクで対応可能です。 次ページに各バンクと対応可能なI/OのI/Fを記します。

## TecStar 2-2 対応可能なI/OのI/F一覧

| 記述           | パンク0-1                                                                                                                                        | パンク2-3                                                                                                                     | パンク4-5                                                                                            | パンク6-7                                                                                                         |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| I/Oバッファ・タイプ  | シングルエンド                                                                                                                                       | シングルエンドと差動                                                                                                                 | シングルエンド                                                                                           | シングルエンドと差動                                                                                                     |

| サポートする出力標準   | LVTTL LVCMOS33 LVCMOS25 LVCMOS18 LVCMOS15 LVCMOS12  SSTL18/7=\textbf{Z},    SSTL2/7=\textbf{Z},    SSTL3/7=\textbf{Z},    HSTL15/7=\textbf{Z} | LVTTL LVCMOS33 LVCMOS25 LVCMOS18 LVCMOS15 LVCMOS12  SSTL18/7=\( \) ,    SSTL2/7=\( \) ,    SSTL3/=\( \) ,    HSTL15/=\( \) | LVTTL LVCMOS33 LVCMOS25 LVCMOS18 LVCMOS15 LVCMOS12  SSTL1875Z I, II SSTL275Z I, II SSTL375Z I, II | LVTTL LVCMOS33 LVCMOS25 LVCMOS18 LVCMOS15 LVCMOS12  SSTL18777X I, II SSTL277X I, II SSTL377X I, II HSTL1577X I |

|              | HSIL15グラス I<br>HSTL18クラス I, II<br>SSTL25Dクラス I, II<br>SSTL33Dクラス I, II                                                                        | HSTL15グラス I<br>HSTL18グラス I, II<br>SSTL25Dグラス I, II<br>SSTL33Dグラス I, II                                                     | HSIL15クラス I<br>HSTL18クラス I, II<br>SSTL25Dクラス I, II<br>SSTL33Dクラス I, II                            | HSTL15クラス I<br>HSTL18クラス I, II,<br>SSTL25Dクラス I, II<br>SSTL33Dクラス I, II                                        |

|              | HSTL15Dクラス I<br>HSTL18Dクラス I, II                                                                                                              | HSTL15Dクラス I<br>HSTL18Dクラス I, II                                                                                           | HSTL15Dクラス I<br>HSTL18Dクラス I, II                                                                  | HSTL15Dクラス I<br>HSTL18Dクラス I, II                                                                               |

|              | LVDS25E 1<br>LVPECL 1<br>BLVDS 1<br>MLVDS 1<br>RSDS 1                                                                                         | LVDS LVDS25E 1 LVPECL 1 BLVDS 1 MLVDS 1 RSDS 1                                                                             | PCI33<br>LVDS25E 1<br>LVPECL 1<br>BLVDS 1<br>MLVDS 1<br>RSDS 1                                    | LVDS PCI33(ECP2Mのみ) LVDS25E 1 LVPECL 1 BLVDS 1 MLVDS 1 RSDS 1                                                  |

| 入力           | 全シングルエンドと差動                                                                                                                                   | 全シングルエンドと差動                                                                                                                | 全シングルエンドと差動                                                                                       | 全シングルエンドと差動                                                                                                    |

| クロック入力       | 全シングルエンドと差動                                                                                                                                   | 全シングルエンドと差動                                                                                                                | 全シングルエンドと差動                                                                                       | 全シングルエンドと差動                                                                                                    |

| PCIサポート      | PCI33クランプなし                                                                                                                                   | PCI33クランプなし                                                                                                                | PCl33クランプあり                                                                                       | PCI33クランプなし<br>(ECP2Mはクランプあり)                                                                                  |

| 真のLVDS出力バッファ |                                                                                                                                               | LVDS (3.5mA) パッファ 2                                                                                                        |                                                                                                   | LVDS (3.5mA) パッファ 2                                                                                            |

- 1.これらの差動I/Fは、外付け抵抗パックと共にコンプリメンタリLVCMOSドライバーを用いることによって、実装されます。

- 2. バンク中のI/Oの50%で使用できます。

## TecStar 2-3 サポートする標準入力I/Fについて

| Input Standard                   | V <sub>REF</sub> (Nom.) | V <sub>CCIO</sub> ¹ (Nom.) |

|----------------------------------|-------------------------|----------------------------|

| Single Ended Interfaces          |                         |                            |

| LVTTL                            | _                       | _                          |

| LVCMOS33                         | _                       | _                          |

| LVCMOS25                         | _                       | _                          |

| LVCMOS18                         | _                       | 1.8                        |

| LVCMOS15                         | _                       | 1.5                        |

| LVCMOS12                         | _                       | _                          |

| PCI 33                           | _                       | 3.3                        |

| HSTL18 Class I, II               | 0.9                     | _                          |

| HSTL15 Class I                   | 0.75                    | _                          |

| SSTL3 Class I, II                | 1.5                     | _                          |

| SSTL2 Class I, II                | 1.25                    | _                          |

| SSTL18 Class I, II               | 0.9                     | _                          |

| Differential Interfaces          |                         |                            |

| Differential SSTL18 Class I, II  | _                       | _                          |

| Differential SSTL2 Class I, II   | _                       | _                          |

| Differential SSTL3 Class I, II   | _                       | _                          |

| Differential HSTL15 Class I      | _                       | _                          |

| Differential HSTL18 Class I, II  | _                       | _                          |

| LVDS, MLVDS, LVPECL, BLVDS, RSDS | _                       | _                          |

|                                  |                         |                            |

- ECP2/Mデバイスの入力バッファは、Mixed Voltage対 応となっております。 LVCMO18,LVCMOS15,PCI33,HSTLxx、SSTLxx以外 に関しましてはVCCIO、VREFに依存せず、入力I/Fをとる ことが可能です。

- 但し、開発ツールにおいて入力するI/Fを選択する必要 はございます。詳しくはDesignPlannerマニュアルをご参 照いただくか、弊社技術担当までご連絡ください。

- 5Vトレラント入力はサポートしておりません。

- 差動I/Fにつきましては本資料のXXXXをご覧下さい。

| 1 | When not specified, | Veelo can | be set an | where in the | valid or | perating range | (page 3- | -1) | i |

|---|---------------------|-----------|-----------|--------------|----------|----------------|----------|-----|---|

|---|---------------------|-----------|-----------|--------------|----------|----------------|----------|-----|---|

|                   |      | Input | syslO Stan | dards |      | Output sysIO Standards |      |      |      |      |

|-------------------|------|-------|------------|-------|------|------------------------|------|------|------|------|

| V <sub>CCIO</sub> | 1.2V | 1.5V  | 1.8V       | 2.5V  | 3.3V | 1.2V                   | 1.5V | 1.8V | 2.5V | 3.3V |

| 1.2V              | Yes  |       |            | Yes   | Yes  | Yes                    |      |      |      |      |

| 1.5V              | Yes  | Yes   |            | Yes   | Yes  |                        | Yes  |      |      |      |

| 1.8V              | Yes  |       | Yes        | Yes   | Yes  |                        |      | Yes  |      |      |

| 2.5V              | Yes  |       |            | Yes   | Yes  |                        |      |      | Yes  |      |

| 3.3V              | Yes  |       |            | Yes   | Yes  |                        |      |      |      | Yes  |

# TecStar 2-4ドライブ能力について

| Input/Output | V <sub>IL</sub> |          | V <sub>IH</sub> |          | Vol                         | Vou                         |                                   |                                   |

|--------------|-----------------|----------|-----------------|----------|-----------------------------|-----------------------------|-----------------------------------|-----------------------------------|

| Standard     | Min. (V)        | Max. (V) | Min. (V)        | Max. (V) | V <sub>OL</sub><br>Max. (V) | V <sub>OH</sub><br>Min. (V) | I <sub>OL</sub> <sup>1</sup> (mA) | I <sub>OH</sub> <sup>1</sup> (mA) |

| LVCMOS 3.3   | -0.3            | 0.8      | 2.0             | 3.6      | 0.4                         | V <sub>CCIO</sub> - 0.      | 20, 16,<br>12, 8, 4               | -20, -16,<br>-12, -8, -4          |

|              |                 |          |                 |          | 0.2                         | V <sub>CCIO</sub> - 0.2     | 0.1                               | -0.1                              |

| LVTTL        | -0.3            | 0.8      | 2.0             | 3.6      | 0.4                         | V <sub>CCIO</sub> - 0.4     | 20, 16,<br>12, 8, 4               | -20, -16,<br>-12, -8, -4          |

|              |                 |          |                 |          | 0.2                         | V <sub>CCIO</sub> - 0.2     | 0.1                               | -0.1                              |

| LVCMOS 2.5   | -0.3            | 0.7      | 1.7             | 3.6      | 0.4                         | V <sub>CCIO</sub> - 0.4     | 20, 16,<br>12, 8, 4               | -20, -16,<br>-12, -8, -4          |

|              |                 |          |                 |          | 0.2                         | V <sub>CCIO</sub> - 0.2     | 0.1                               | -0.1                              |

|              |                 |          |                 |          |                             | l                           | 16 12                             | -16 -12                           |

<sup>\*</sup>ECP2/M DataSheet(sysIO Single-Ended DC Electrical Characteristics)より抜粋

|                |                  | LFE  | 2-6E        |

|----------------|------------------|------|-------------|

| Ball<br>Number | Ball<br>Function | Bank | Dui<br>Fund |

| L1             | PL27A            | 6    |             |

| L5             | PL26B            | 6    |             |

| M1             | PL27B            | 6    |             |

| GND            | GNDIO            | 6    |             |

| N1             | PL29A            | 6    |             |

| N2             | PL28A            | 6    | LDQS        |

| P1             | PL29B            | 6    |             |

| P2             | PL28B            | 6    |             |

| R1             | PL30A            | 6    |             |

| GND            | GNDIO            | 6    |             |

| R2             | PL30B            | 6    |             |

| N4             | TDI              | - 1  |             |

| M4             | TCK              | - 1  |             |

| P3             | TDO              | -    |             |

| N3             | TMS              | - 1  |             |

| K7             | VCCJ             | - 1  |             |

| M5             | PB2A             | 5    | VREF        |

| K6             | NC               | - 1  |             |

| M6             | PB2B             | Б    | VREF        |

| R3             | NC               | -    |             |

| P4             | NC               | - 1  |             |

- 上記の表のように、ECP2/Mのドライブ電流値は可変させることが可能です。設定したI/Fによって、設定できる値は異なりますので、データシートで御確認ください。

- ECP2/MのI/Oバッファーのドライブ可能電流は以下のような制約があります。

<sup>1</sup>The average DC current drawn by I/Os between GND connections, or between the last GND in an I/O bank and the end of an I/O bank, as shown in the logic signal connections table shall not exceed n \* 8mA, where n is the number of I/Os between bank GND connections or between the last GND in a bank and the end of a bank.

BankのGND間にあるI/O、もしくはI/O Bank内にある最後のGNDからI/O Bankの端までにあるI/Oの本数において、(その本数)×8mAのドライブ電流を超えてはいけない

- 例えば、LFE2-6E 256fpBGAのピンリストを見ますと左のようになっております。赤枠を注目してください。 ここでI/Oバンクの端からGNDまでのI/Oの本数を数えますと3本になっております。よって、8mA×3本 = 24mAとなり、この3本のI/Oは合計で最大24mAまでドライブすることができます。例えば、この場合、 BallNo.L1のI/Oが20mAドライブする場合には、残り2本は4mAまでしかドライブできません。

- 次に青枠をご覧下さい。ここではGND、GND間のI/Oの本数を数えますと5本となっております。よって、 8mA×5本 = 40mAとなり、5本のI/Oは合計で最大40mAまでドライブすることができます。

\* ECP2/M DataSheet (LFE2-6E and LFE2-12E Logic Signal Connections: 256 fpBGA (Cont.))より抜粋

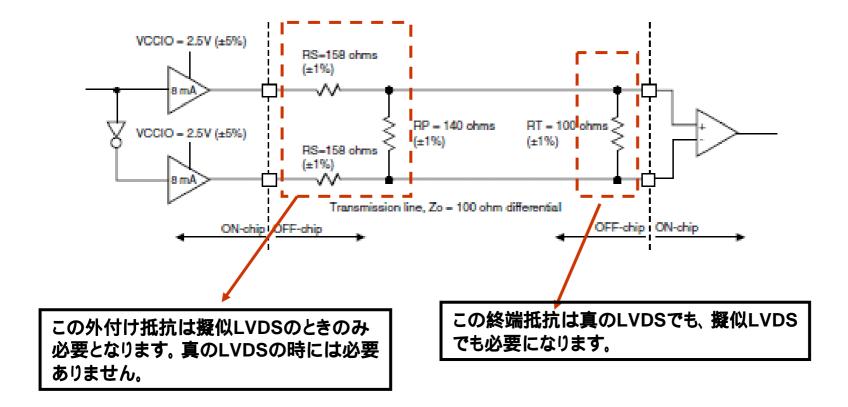

## TecStar 2-5 差動LVDS I/F対応について

## 差動LVDS入力について

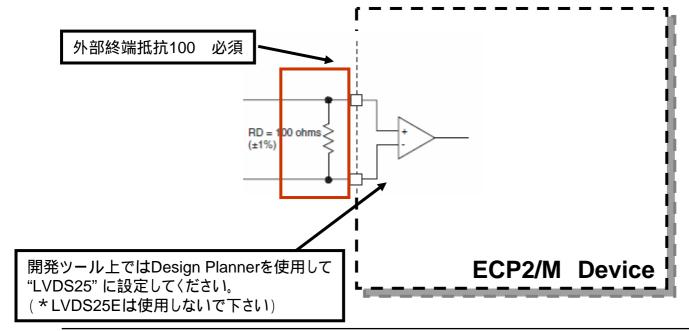

- Top,Bottom,Right,Left全てのバンクで差動LVDS入力として使用 できます。

- 但し、使用するI/Oは必ず差動ペアにしてください。差動ペアとは右のピンリストのPL2A,PL2Bになります。T側がTrue,C側がComplementaryになります。

- 差動LVDS入力で使用する場合、<u>外部に終端抵抗100</u>が必ず必要になります。

- 差動LVDS入力として扱った場合、内部Pull-upが有効となりません。 その為、転送用ケーブルが外れるようなアプリケーションの場合に は、Floating防止の為、外部で処理が必要になります。処理については弊社FAEまでお問い合わせ下さい。

|                | LFE2-6E          |       |   |      |                  |              |  |  |  |

|----------------|------------------|-------|---|------|------------------|--------------|--|--|--|

| Ball<br>Number | Ball<br>Function |       | E | Bank | Dual<br>Function | Differential |  |  |  |

| C3             | PL2A             |       | T | 7    | VREF2_7          | T*           |  |  |  |

| C2             |                  | PL2B  |   | 7    | VREF1_7          | ċ            |  |  |  |

| D3             | П                | PL5A  | V | 7    |                  | Т            |  |  |  |

| D4             |                  | PL4A  | П | 7    |                  | T*           |  |  |  |

| D2             | П                | PL5B  | П | 7    |                  | С            |  |  |  |

| GND            |                  | GNDIO | П | 7    |                  |              |  |  |  |

| E4             |                  | PL4B  | Т | 7    |                  | ò            |  |  |  |

|                |                  |       |   |      |                  |              |  |  |  |

# TecStar 2-5 差動LVDS I/F対応について

## 差動LVDS出力について

差動LVDS出力は真のLVDSと擬似LVDSの2つが存在します。

### 真のLVDS出力

- LEFT,Rightバンクの50%のみ対応しております。ピンリストで確認した場合 Differencialの項目に\*印がついてる個所が真のLVDS対応I/Oです。

- 使用するI/Oは、差動入力と同じ〈差動ペアにして下さい。

- 真のLVDSで使用する場合、VCCIOには2.5Vを印加する必要がございます。 必然的に、LVDSを使用するこのバンクは2.5Vインターフェイスでしか使用できませんのでご注意ください。

- 開発ツール上では、DesignPlannerを使用してI/O Typeを"LVDS25"に設定してください。

- 外付け抵抗は必要ありません。

## 擬似LVDS出力(Emulated LVDS)

- Top,Bottom,Left,Right全てのバンクで擬似LVDS出力として使用できます。

- 使用するI/Oは、差動入力と同じ〈差動ペアにして下さい。(真のLVDSと違い\*印がついていなくとも問題ございません)

- 擬似LVDSで使用する場合、VCCIOには2.5Vを印加する必要がございます。 必然的に、LVDSを使用するこのバンクは2.5Vインターフェイスでしか使用で きませんのでご注意ください。

- 開発ツール上では、DesignPlannerを使用してI/O Typeを"LVDS25E"に設定してください。ドライブ電流は8mAにしてください。

- <u>外付け抵抗が必要になります。詳細は次ページをご覧下さい。</u>

|                | LFE2-6E          |      |                  |              |  |  |  |  |  |

|----------------|------------------|------|------------------|--------------|--|--|--|--|--|

| Ball<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differential |  |  |  |  |  |

| C3             | PL2A             | 7    | VREF2_7          | T*           |  |  |  |  |  |

| C2             | PL2B             | 7    | VREF1_7          | C.           |  |  |  |  |  |

| D3             | PL5A             | 7    |                  | Т            |  |  |  |  |  |

| D4             | PL4A             | 7    |                  | T*           |  |  |  |  |  |

| D2             | PL5B             | 7    |                  | С            |  |  |  |  |  |

| GND            | GNDIO            | 7    |                  |              |  |  |  |  |  |

| E4             | PL4B             | 7    |                  | C.           |  |  |  |  |  |

## 差動LVDSブロック図

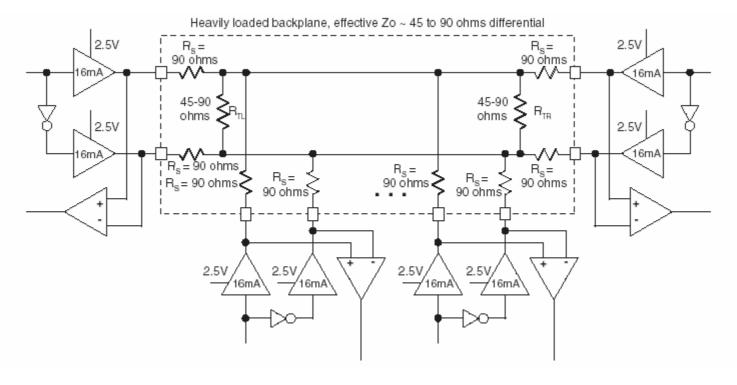

# TecStar 2-6 その他差動 I/Fについて

## 差動BLVDSブロック図

\*詳細はデータシートをご覧下さい。

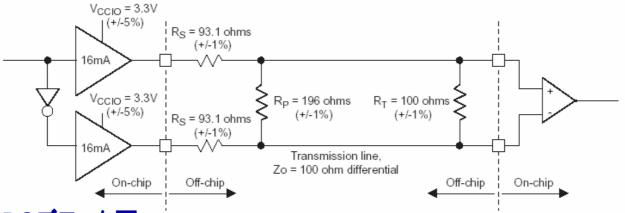

## TecStar 2-6 その他差動 I/Fについて

### 差動LVPECLブロック図

\*詳細はデータシートをご覧下さい。

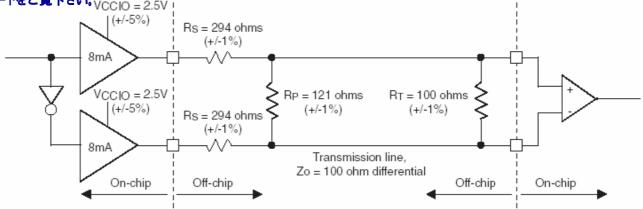

## 差動RSDSブロック図

\* 詳細はデータシートをご覧下さい。<sub>VCCIO = 2.5V</sub>

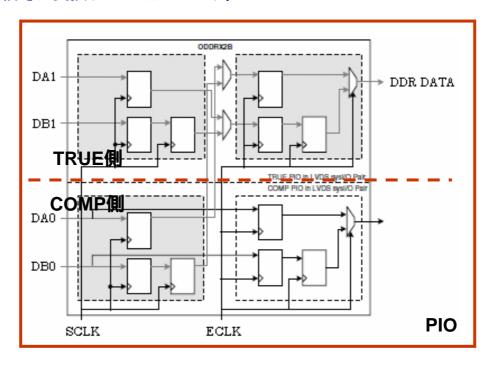

## 「ecstar 2-7 GearingBox使用時の注意点

ECP2/MデバイスはGearingBoxが内蔵されており、この機能を使用することで外部からの高速シリア ル信号をパラレル信号に変換することができます。

### 〔注意点〕

GearingBoxを使用した場合、出力信号はPIOのTRUE側になります。この場合、COMP側は 使用できなくなりますのでご注意ください。

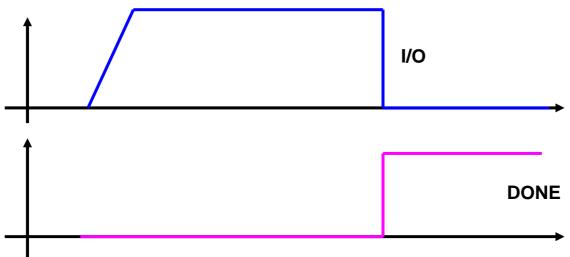

## Tecstar 2-8 電源ON時のI/Oの挙動について

上の図はECP2デバイスにおける電源ON時のI/Oピンの挙動を示しております。 注意すべき点は・・・

電源ON時(まだコンフィグレーションされていない状態)には、I/Oピンは必ず内部プルアッ プでハイインピーダンスの状態になります。

よってコンフィグレーションが完了するまでの間は(DONEがHigh)、上記のように電源の立 ち上がりにつられて内部プルアップ抵抗の影響で、Hign信号が観測されます。 よって、もし、Low極性を期待しており、このHigh信号を無くしたい場合は、少なめの抵抗 (1k 等)で外部プルダウン処理を施すようにして下さい。

電源ON時、Low極性したNI/Oピンに関して、内部Pull-Down設定や、I/Oピンに繋がるFF の極性をReset(PowerOnReset)時、Lowにしておいても上記の事が影響して必ずHigh が出力されますのでご注意ください。

Corporation

**Bringing the Best Together**

## ECP2/Mのコンフィグレーションについて

# TecStar 3-1 コンフィグレーションモードについて

### ECP2/Mデバイスがサポートしているコンフィグレーションモードは以下の通りです

#### •SPIモード

SPI I/Fを保有しているFlashメモリと直接接続し、コンフィグレーションを行います。

#### •SPImモード

SPIフラッシュメモリの記憶領域を2つに分け、デュアルブート機能を用いたコンフィグレーションを行います。 デュアルブートに関しての詳細はデータシート及びテクニカルノート(TN1108)を参照して〈ださい。

#### •スレープシリアルモード

FPGAがスレーブ(クロックCCLKから入力)となり、外部シリアルROM,或いはCPUからのデータを読み込みコンフィグレーションを行うモードです。

#### •スレーブパラレルモード

FPGAがスレーブ(クロックCCLKから入力)となり、外部シリアルROM、或いはCPUからのデータを読み込みコンフィグレーションを行うモードです。

### •ispJTAGモード

ispJTAGポートを介してコンフィグレーションを行うモードです。

## TecStar 3-2 コンフィグレーションモード選択

コンフィグレーション選択ピンCFG[2:0](後述)を以下のように設定することで、各種コンフィグレーションモードを決定します。

| モード            |               | CFG[2] | CFG[1] | CFG[0] | D[0]/SPIFASTN | 備考                    |

|----------------|---------------|--------|--------|--------|---------------|-----------------------|

| SPI            | Normal (0x03) | 0      | 0      | 0      | PULL-UP       |                       |

|                | Fast (0x0B)   | 0      | 0      | 0      | PULL-DOWN     | SPIフラッシュがサポートしている必要あり |

| SPIm           | Normal (0x03) | 0      | 1      | 0      | PULL-UP       |                       |

|                | Fast (0x0B)   | 0      | 1      | 0      | PULL-DOWN     | SPIフラッシュがサポートしている必要あり |

| Slave S        | Slave Serial  |        | 0      | 1      | X             |                       |

| Slave Parallel |               | 1      | 1      | 1      | x             |                       |

| ispJTAG        |               | x      | x      | х      | D[0]          | CFG[2:0]の設定によらず、常に有効  |

<sup>-</sup>SPIFASTNがHighのとき、ECP2はSPIフラッシュに対して読み出しオペコードとして0x03(hex)を与えます。0x03はSPIフラッシュ25シリーズ全てにおいて使用されている、標準的な読み出し命令です。

**Bringing the Best Together**

-144pin,208pinTQFPはスレープパラレルはサポートしておりません。

<sup>-</sup>SPIFASTNがLowのとき、ECP2はSPIフラッシュに対して、より高い周波数の読み出しクロックに対応する高速読み出しオペコード0x0B(hex)を与えます。なお、0x0B(hex)をサポートしていないSPIフラッシュもありますので、その点に関しましてもメーカーのデータシートを参照してください。また、PCBレイアウトの整合性に違反するような設計にならないようご注意ください。

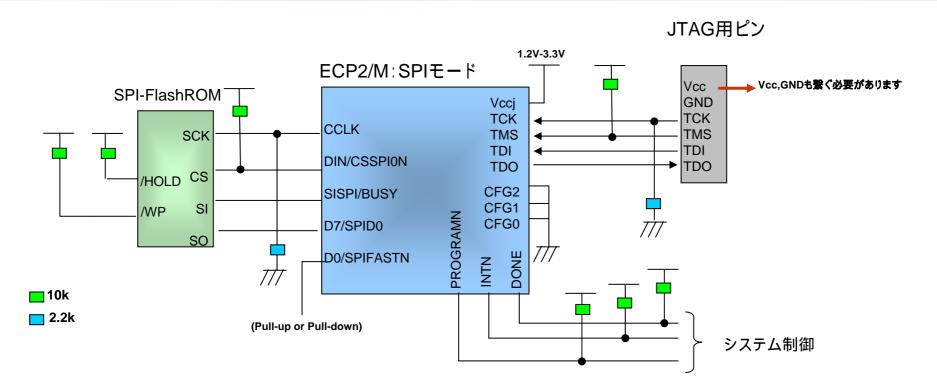

## 「ecstar 3-3 SPIモード詳細(1Flash+1FPGAの場合)

- ·DOUT信号はコンフィグレーション中出力ピンとなります。もし、このピンをUser I/Oとして使用する場合には出力ピンとして使用することを推奨します。

- ・D[0]/SPIFASTはお使いになるSPI-FLASHが高速読み出しをサポートしているかどうかを御確認頂き、Pull-down,Pull-up処理を行なってください。

- ・PROGRAMNはコンフィグ失敗時や、コンフィグレーションシーケンスから抜け出せないようなイレギュラーな現象が起こった場合にトグルすることでFPGAを 初期化し、再コンフィグレーション行なうことができます。CPUに接続して管理、制御できるようにしておくことを推奨します。DONE,INITに関しましてはコンフィ グレーションの状態を確認することができます。LEDを接続しておくことでデバック時にとても有効です。

- ・D[0]/SPIFASTはお使いになるSPI-FLASHが高速読み出しをサポートしているかどうかを御確認頂き、Pull-down,Pull-up処理を行なってください。

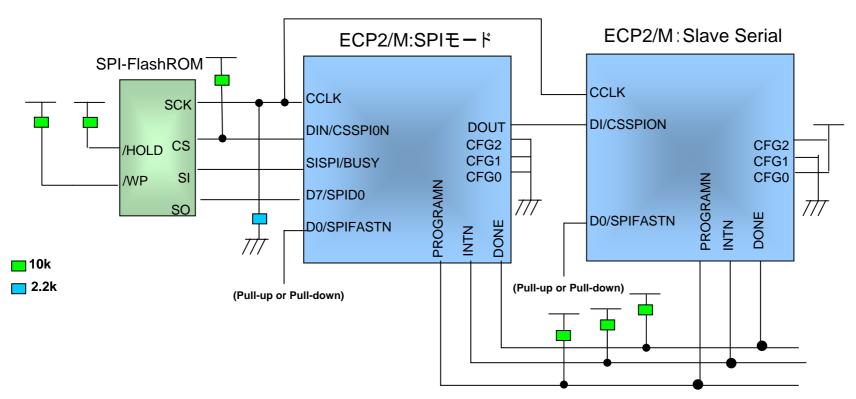

## TecStar 3-4 SPIモード詳細(1Flash+2FPGAの場合)

- ·FPGAを二つ以上繋ぐ場合、CFGピンを 1番目のデバイスはSPIモードに、2番目からはスレーブシリアルモードに設定する必要があります。

- ・1番目FPGAは、DesignPlannerにおいてDONE\_EXの扱いをONにしておく必要があります。それに伴って、Wakeupシーケンスを4に変更してください。

# TecStar

## Star 3-5 SPImモード詳細 (ECP2)

#### JTAG用ピン ECP2:SPImモード Vcc.GNDも繋ぐ必要があります Vcc GND SPI-FlashROM **TCK** TCK **TMS** TMS CCLK SCK TDI TDI TDO TDO DIN/CSSPION CFG<sub>2</sub> CS /HOLD CFG1 SISPI/BUSY CFG0 SI /WP **PROGRAMN** D7/SPID0 SO D0/SPIFASTN NTN 10k 2.2k (Pull-up or Pull-down) システム制御

- ·DOUT信号はコンフィグレーション中出力ピンとなります。もし、このピンをUser I/Oとして使用する場合には出力ピンとして使用することを推奨します。

- ・D[0]/SPIFASTはお使いになるSPI-FLASHが高速読み出しをサポートしているかどうかを御確認頂き、Pull-down,Pull-up処理を行なってください。

- ・PROGRAMNはコンフィグ失敗時や、コンフィグレーションシーケンスから抜け出せないようなイレギュラーな現象が起こった場合にトグルすることでFPGAを 初期化し、再コンフィグレーション行なうことができます。CPUに接続して管理、制御できるようにしておくことを推奨します。DONE,INITに関しましてはコンフィ グレーションの状態を確認することができます。LEDを接続しておくことでデバック時にとても有効です。

- ・D[0]/SPIFASTはお使いになるSPI-FLASHが高速読み出しをサポートしているかどうかを御確認頂き、Pull-down,Pull-up処理を行なってください。

- ·DualBootイメージの作成方法、概念に関しましてはデータシート及びテクニカルノート(TN1108)をご参照ください。

**Bringing the Best Together**

# TecStar

## Star 3-5 SPImモード詳細 (ECP2M)

#### JTAG用ピン ECP2:SPImモード Vcc.GNDも繋ぐ必要があります Vcc GND SPI-FlashROM **TCK** TCK **TMS** TMS CCLK SCK TDI TDI TDO TDO DIN/CSSPI1N CFG<sub>2</sub> CS /HOLD CFG1 SISPI/BUSY CFG0 SI /WP **PROGRAMN** D7/SPID0 SO D0/SPIFASTN NTN 10k 2.2k (Pull-up or Pull-down)

- ·DOUT信号はコンフィグレーション中出力ピンとなります。もし、このピンをUser I/Oとして使用する場合には出力ピンとして使用することを推奨します。

- ・D[0]/SPIFASTはお使いになるSPI-FLASHが高速読み出しをサポートしているかどうかを御確認頂き、Pull-down,Pull-up処理を行なってください。

- ・PROGRAMNはコンフィグ失敗時や、コンフィグレーションシーケンスから抜け出せないようなイレギュラーな現象が起こった場合にトグルすることでFPGAを 初期化し、再コンフィグレーション行なうことができます。CPUに接続して管理、制御できるようにしておくことを推奨します。DONE,INITに関しましてはコンフィ グレーションの状態を確認することができます。LEDを接続しておくことでデバック時にとても有効です。

- ・D[0]/SPIFASTはお使いになるSPI-FLASHが高速読み出しをサポートしているかどうかを御確認頂き、Pull-down,Pull-up処理を行なってください。

- ·DualBootイメージの作成方法、概念に関しましてはデータシート及びテクニカルノート(TN1108)をご参照ください。

**Bringing the Best Together**

システム制御

## IecStar 3-6 SPIモードカスケード方式の詳細 (ECP2Mのみ適用)

## \*TBD

2.2k

# TecStar 3-7 Slaveシリアルモード詳細

**TBD**

## TecStar 3-8 Slaveパラレルモード詳細

**TBD**

(注意) Slave Parallelに関しては144pin,208pin TQFPはサポートしておりません

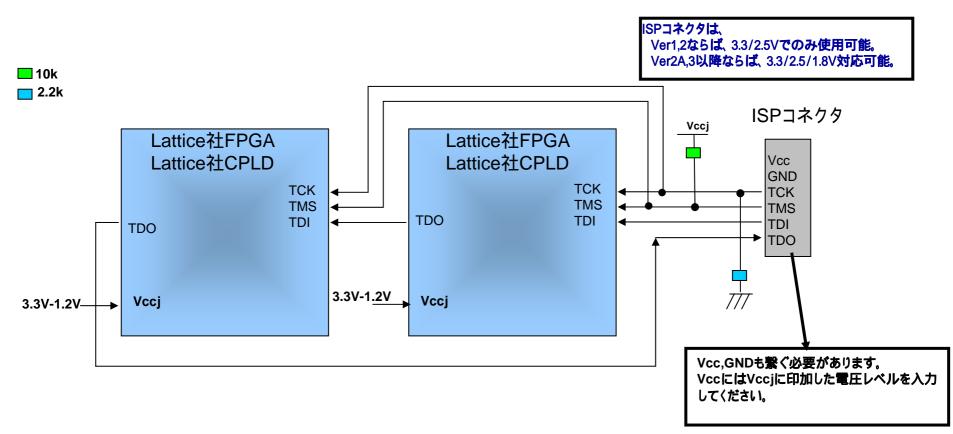

# TecStar 3-9 JTAGモード詳細

- •Vcciは、JTAGチェインで統一してください。

- •もし、チェイン上に3.3Vデバイスと1.2Vデバイスが混在している場合などは、3.3VデバイスのTDOと1.2VデバイスのTDIのI/F取るためにVccjを3.3Vにする必要があります。

- •その他、詳細につきましては、弊社作成のマニュアルJTAG基板設計時資料をご覧下さい。

## ECP2/Mのコンフィグレーション専用ピン詳細説明

# TecStar 4-1 コンフィグレーション専用ピン詳細説明

以下はコンフィグレーションを制御するのに用いられるLatticeECP2のsysCONFIG専用ピンの記述です。

## CFG[2:0]

- コンフィグレーション・モード・ピンCFG[2:0]は入力ピンです。これらは、コンフィグレーション・モードを選択 するのに用いられます。パワーオン・リセット時やPROGRAMNピンがLowレベルにされたときに、これら のピンをサンプリングし、コンフィグレーションモードを決定します。

#### PROGRAMN

PROGRAMNピンはプログラミング・シーケンスを起動するため用いるデバイスへの入力です。このピンに与えられる信号がHighからLowになると、デバイスはコンフィグレーション・モードに設定されます。パワーアップ時を除いてプログラミングのきっかけとするのにPROGRAMNピンを用いることができます。デバイスがJTAGを用いている場合、デバイスはJTAGモードから解放されるまで、PROGRAMNピンを無視します。

#### INITN

- INITNピンは双方向のオープン・ドレイン制御ピンです。これはLowパルスを駆動することができると共に、Lowパルス入力を検出することができます。PROGRAMNピンがLowにされたとき、またはパワーアップ時パワーオン・リセット信号が解放されたときに、INITNピンはコンフィグレーション回路と外部PROMをリセットするためにLowにドライブされます。PROGRAMNピンがLowである間、コンフィグレーション・メモリはクリアされます。このときINITNピンはLowのままです。外部からにINITNピンにLowをドライブすることで、コンフィグレーションを遅らせることが可能です。INITNピンがLowに保たれている限り、デバイスはコンフィグレーション・モードには入りません。

- コンフィグレーションの間、INITNピンはエラー検出ピンになります。コンフィグレーション・エラーが発生すると、Lowにドライブされます。

# TecStar 4-1 コンフィグレーション専用ピン詳細説明

#### DONE

DONEピンは双方向の制御ピンです。オープン・ドレインかアクティブ・ドライブ制御ピンとして構成することができます。デバイスがコンフィグレーション・モードにあるとき、または、内部DONEビットがプログラムされていないとき、DONEピンはLowになります。INITNとPROGRAMNピンがHighで、DONEビットがプログラムされると、DONEピンは解放されます。オープン・ドレインのDONEピンは外部的にLowにすることができ、そして、選択されたウェイクアップ・シーケンスによって、DONEピンが解放されるまで、デバイスは動作しません。

### CCLK

- CCLKピンはコンフィグレーションモード選択により、入力/出力何れかに設定されます。CFGピンがサンプルされたときにSPIモードかSPImモードが選択されていると、CCLKピンは出力ピンになります。そうでなければ、CCLKは入力ピンになります。CCLKピンが出力ピンになる場合、内部プログラマブル・オシレータがCCLKに接続されて、スレーブ・デバイス用に出力されます。CCLKは、DONEピンがHighにされ、デバイスのウェイクアップ・シーケンスが完了した後100~500クロック・サイクルで止まります。これら余分なクロックは、チェーン内の他デバイスが確実にウェイク・アップするために十分なクロックとして出力されます。CCLK出力が止まると、入力としてトライステートになります。なお、PROGRAMNピンがトグルされるなど、次のコンフィグレーション初期化シーケンスではCCLKピンは再度出力ピンとなり、クロック出力を再開します。ispLEVERのDesign Planner上のMCCLK\_FREQパラメータはCCLKマスタ周波数を制御します。

# TecStar 4-1 コンフィグレーション専用ピン詳細説明

## DI/CSSPION

- シリアル・ビットストリーム・コンフィグレーションでは常に、DI/CSSPIONピンはDI(データ入力)となり、内部で弱くプルアップされています。データはCCLKの立ち上がりエッジで取られます。シリアル・モードが選択され、コンフィグレーション・モードで用いられないとき、DI/CSSPIONピンはUser I/Oとして使用することができます。

- SPIかSPImモードのどちらかで、DI/CSSPIONはSPIフラッシュのチップ・セレクトをドライブするための専用チップ・セレクト出力になります。ECP2デバイスがSPIポートを通してのコンフィグレーション・プロセスにない場合、DI/CSSPIONはHighにドライブされます。

#### DOUT/CSON/CSSPI1N

- DOUT/CSON/SCCP1Nピンは、出力ピンとして使用されます。シリアルおよびパラレル・コンフィグレーション・モードにおいて Bypassモードが選択されたとき、このピンはDOUTになります。Bypassモードにあるデバイスが完全にコンフィグレーションされ ると、Bypass命令が実行されます。次に、DIかD[0:7]にあるデータがDOUTピンに送られ、シリアルデータを次のデバイスに渡 します。パラレル・コンフィグレーション・モードでは、D0が初めにシフトアウトされ、次いでD1、D2と続きます。

- パラレル・コンフィグレーション・モードでは、FIOW\_THROUGHモードが選択されたとき、このピンはチップ・セレクト出力 (CSON)になります。デバイスが完全に構成されたると FIOW\_THROUGHモードで、フロースルー命令は実行され、CSONピンは次のデバイスのチップ・セレクト・ピンをイネーブルするためLowをドライブします。

- SPImモードではデイジーチェーン方式のコンフィグレーションがサポートされておりませんが、ECP2Mでのみ、このピンが2番目のSPIフラッシュのチップ・セレクト出力となります。(ECP2では使用できません。)

- DOUT/CSON/CSSPI1Nピンは、パワーアップ時にHIGHをドライブし、ビット・ストリーム中のBypass/Flowthrough命令の実行されるか、ユーザーコードによってI/Oタイプが変更されない限り、そのままの状態を維持します。

# TecStar 4-1 コンフィグレーション・I/O兼用ピン詳細説明

### CSN and CS1N

- CSNとCS1Nは弱く内部プルアップされたLowアクティブの制御入力ピンで、パラレルモードでのみ使用されます。これらの入力信号の論理和によって、D[0:7]のデータの受け取りや出力が制御されます。

- CSNとCS1NピンのいずれかがHighのとき、D[0:7]、INITN、およびBUSYはトライステートになります。CSNとCS1NはD[0:7]、INITN、およびBUSYピンを制御しているとき、信号の交換が可能です。

- CSNとCS1Nピンが共にHighのとき、フロースルー/バイパス・レジスタがリセットされ、BypassモードまたはFlow-Throughモードが解除されます。BypassモードもFlow-Throughモードも使用していない場合は、CSNとCS1NピンはLowに固定されます。

#### WRITEN

WRITENピンはLowアクティブの制御入力ピンで、パラレルモードでのみ使用されます。WRITENピンは、データ・ピンD[0:7]の方向を決定するのに用いられます。プログラミングの間、バイト・データがデバイスにシフトされるときに、WRITENピンはLowにドライブされます。データがデバイスからパラレルモードで読まれるときには、WRITENピンはHighにドライブされます。

#### BUSY/SISPI

- BUSY/SISPIピンはデュアル・ファンクションのピンです。パラレルモードでは、BUSYピンはトライステート出力となります。D[0:7]ピンでバイト・データを受ける準備ができているとき、またはバイト・データが読み出す準備ができているときのみ、BUSYピンはデバイスによってLowにドライブされます。

- SPIまたはSPImモードでは、BUSY/SISPIピンは読み出し制御データをSPIフラッシュにドライブする出力ピンになります。また、制御データはCCLKの立下りエッジで出力されます。

# TecStar 4-1 コンフィグレーション・I/O兼用ピン詳細説明

#### BUSY/SISPI

- BUSY/SISPIピンはデュアル・ファンクションのピンです。パラレルモードでは、BUSYピンはトライステート出力となります。 D[0:7]ピンでバイト・データを受ける準備ができているとき、またはバイト・データが読み出す準備ができているときのみ、BUSY ピンはデバイスによってLowにドライブされます。

- SPIまたはSPImモードでは、BUSY/SISPIピンは読み出し制御データをSPIフラッシュにドライブする出力ピンになります。また、制御データはCCLKの立下りエッジで出力されます。

### D[0]/SPIFASTN

- パラレルモードのとき、D[0]ピンは後述のD[1:5]ピンと同じ機能となります。D[0:7]がパラレル・データ・バスからデータを受け取る時に、D[0]は先頭ビットとなります。

- SPIまたはSPImモードのとき、D[0]/SPIFASTNピンは入力ピンとなります。SPIFASTNはINITNの立上がりエッジでサンプリングを行います。SPIFASTNがHighのとき、ECP2はSPIフラッシュに対して読み出しオペコードとして0x03(hex)を与えます。0x03はSPIフラッシュ25シリーズ全てにおいて使用されている、標準的な読み出し命令です。SPIFASTNがLowのとき、ECP2はSPIフラッシュに対して、より高い周波数の読み出しクロックに対応する高速読み出しオペコード0x0B(hex)を与えます。正確なクロックスピードに関してはSPIフラッシュのデータシートを参照してください。なお、0x0B(hex)をサポートしていないSPIフラッシュもありますので、その点に関しましてもメーカーのデータシートを参照してください。また、PCBレイアウトの整合性に違反するような設計にならないようご注意ください。

# TecStar 4-1 コンフィグレーション・I/O兼用ピン詳細説明

### • D[1:5]

- D[1:5]ピンはパラレルモードでのみ使用します。D[1:5]ピンはデータのリード、ライトを行う双方向トライステートピンです。

WRITENがLowで、かつCSN、CS1NがLowのとき、D[1:5]ピンは入力ピンとなります。WRITENピンにHighがドライブされており、かつCSN、CS1NがLowのとき、D[1:5]ピンは出力ピンとなります。CSNまたはCS1NがHighのときはD[1:5]はトライステートとなります。

- ー デバイス動作中にEBRまたはディストリビュートRAMからリードバックを行う際には、データが壊れる可能性がありますので、十分に注意してください。

## D[7]/SPID0 and D[6]/SPID1

- パラレルモードのとき、これらのピンは上記のD[1:5]ピンと同様の機能となります。D[0:7]がパラレル・データ・バスからデータを受け取る時に、D[7]は最後尾ビットとなります。

- SPIまたはSPImモードのとき、D[7]/SPID0ピンは入力ピンとなります。このとき、D[7]/SPID0ピンをSPIフラッシュのデータ出力 ピンに繋いでください。なお、D[7]/SPID0ピンに入力されたデータはCCLKの立上がりエッジで叩かれます。

- ECP2Mのみ、SPIまたはSPImモードにおけるデイジーチェーン方式でのコンフィグレーション時に、D[6]/SPID1ピンが後続の SPIフラッシュの出力データ入力ピンになります。なお、D[6]/SPID1ピンに入力されたデータはCCLKの立上がりエッジで叩かれます。

# TecStar 4-2 JTAGピン

ispJTAGピンは標準のIEEE1149.1TAPピンです。LatticeECP2デバイスがパワーアップされるとき、ispJTAGピンは常にアクセス可能となっています。なお、ispJTAGピンを用いるとき、sysCONFIG専用ピンはJTAG動作には必要なく、PROGRAMNピンの挙動も無視されます。

#### TDO

テストデータ出力ピンTDOは、シリアルのテスト命令とデータをシフトアウトするのに用いられます。TDOが内部回路によってドライブされていないとき、ピンはハイ・インピーダンス状態にあります。

### TDI

- テストデータ入力ピンTDIは、シリアルのテスト命令とデータをシフトインするのに用いられます。TDIピンには内部プルアップ抵抗があります。内部抵抗はVCCJにプルアップされています。

#### TMS

- テストモード・セレクト・ピンTMSはTAPコントローラのテスト動作を制御します。TCKの立ち下がりエッジで、 TMSがHighかLowかによって、TAPコントローラ・ステート・マシンの状態遷移が行われます。TMSピンに は内部プルアップ抵抗があります。内部抵抗はVCCJにプルアップされています。

### TCK

テスト・クロック・ピンTCKは、TAPコントローラを走らせ、データをおよび命令レジスタへのロード、リロードのためのクロックを提供します。TCKはHighまたはLow状態で止めることができ、デバイス・データシートで示される周波数まで動作させることができます。TCKピンはデータシートのDCパラメータ・テーブルに示される値でヒステリシスをサポートします。

### VCCJ

- VCCJは、JTAGピンに対し電源を供給する他、JTAGデバイスでチェーンを作るのを許容するために、独立した電源をJTAGポートに供給します。

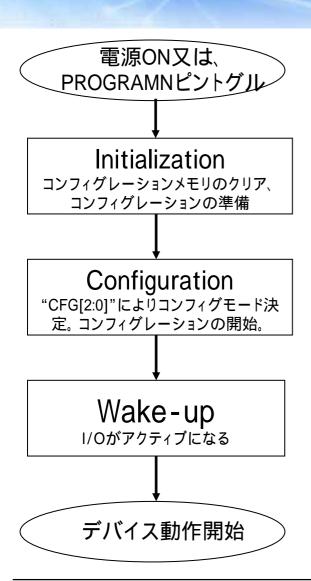

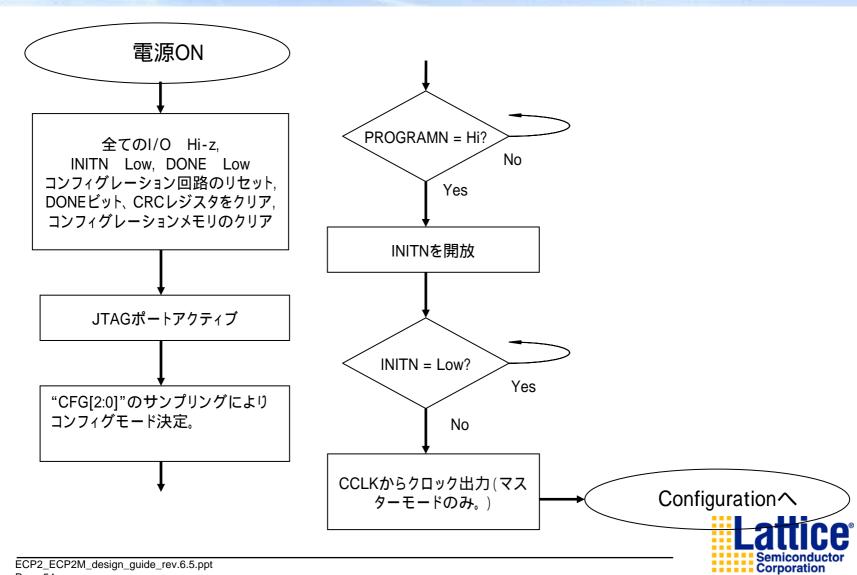

## ECP2/Mのコンフィグレーションフロー

# TecStar 5-1 コンフィグレーションフロー(全体)

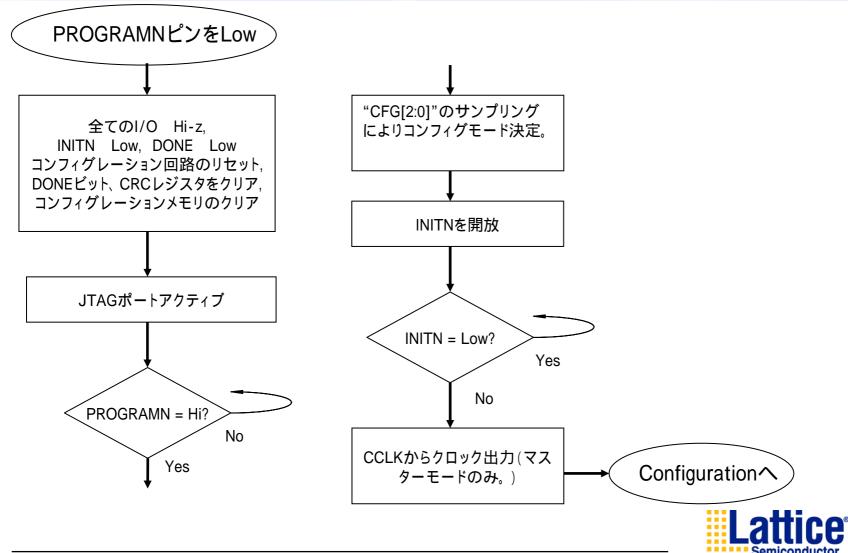

## Initialization

電源投入又はPROGRAMNピンをLowにトグルすることで、FPGA内部コンフィグレーション・メモリ領域がクリアされます。コンフィグレーション・メモリ領域とDoneビットをクリアし終えると、INITNピンはEC/ECPデバイスによって開放されます。外部からINITNピンをLowにドライブすることで、コンフィグレーション・プロセスを遅らせることができます。

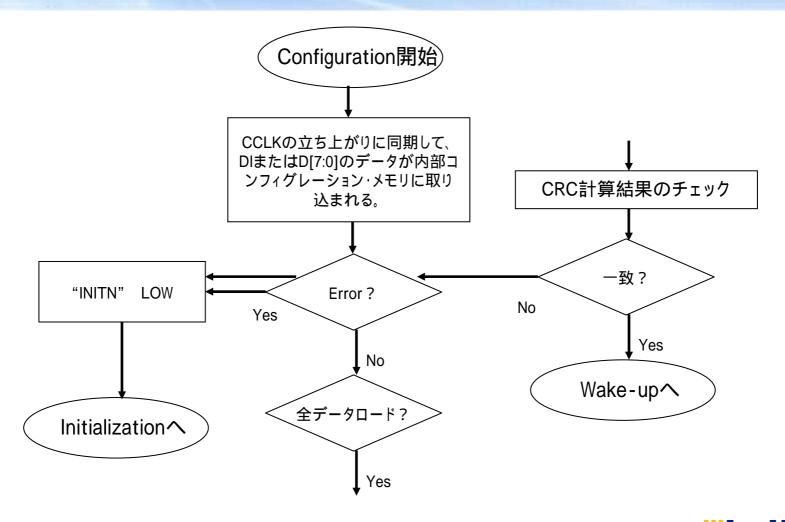

## Configuration

選択されたコンフィグレーション・モードにより、DIかD[0:7]からビット・ストリームをロードします。何らかのエラーがあるとINITNピンはLowになり、エラー発生を知らせます。

## Wake-up

ウェイクアップ・シーケンスは、コンフィグレーションの完了後にデバイスを 機能モードに投入します。

適切なウェイクアップ・シーケンスを選ぶことは、コンテンションを防ぐために重要です。

## TecStar 5-2 Initializeシーケンス(電源ON時)

# TecStar 5-3 Initializeシーケンス(Programnピン)

# TecStar 5-4 コンフィグレーションシーケンス

# TecStar 5-5 Wake Up(コンフィグレーション完了後のデバイスの起動)

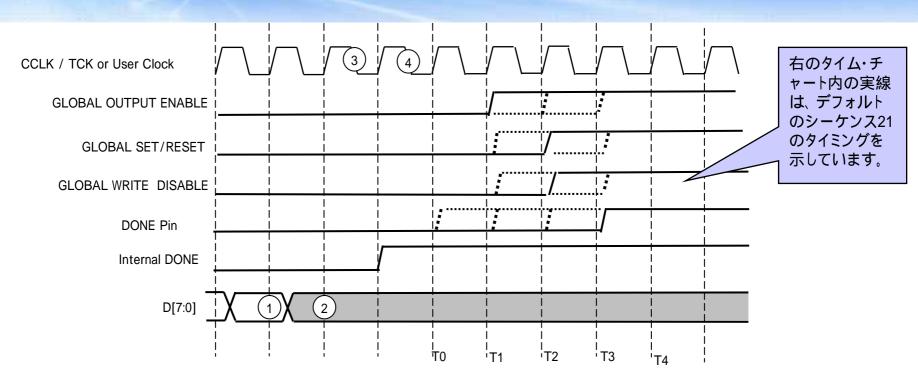

## ●ウェイク・アップは25通りのシーケンスから1つを選択

ビット・ストリーム生成時のWAKE\_UPプリファレンスにて指定制御される信号は、

- •GOE (グローバル・アウトプット・イネーブル)

- •GSR (グローバル・セット・リセット)

- •GWD (グローバル・ライト・ディセーブル)

- •DONE (DONEピン)

## ●ウェイク・アップのためのクロックを選択

ビット・ストリーム生成時のWAKEUP\_CLKプリファレンスにて指定 指定できるクロックは、

- •CCLK(デフォルト)

- ・ユーザクロック(任意のクロック入力ピン、もしくは任意のネットで指定可能

## ●ウェイク・アップ・シーケンス開始をPLLロック後に設定可能

WAKE\_ON\_PLLプリファレンスを用いることで、ウェイク・アップ・シーケンス開始をPLLのLock信号が出力するまで待機させることが可能

# TecStar 5-6 WakeUpシーケンス

| Sequence     | Phase T0 | Phase T1        | Phase T2        | Phase T3        |

|--------------|----------|-----------------|-----------------|-----------------|

| Default      |          | GOE             | GSR, GWDIS      | DONE            |

| 1            | DONE     | GOE, GWDIS, GSR |                 |                 |

| 2            | DONE     |                 | GOE, GWDIS, GSR |                 |

| 3            | DONE     |                 |                 | GOE, GWDIS, GSR |

| 4            | DONE     | GOE             | GWDIS, GSR      |                 |

| 5            | DONE     | GOE             |                 | GWDIS, GSR      |

| 6            | DONE     | GOE             | GWDIS           | GSR             |

| 7            | DONE     | GOE             | GSR             | GWDIS           |

| 8            |          | DONE            | GOE, GWDIS, GSR |                 |

| 9            |          | DONE            |                 | GOE, GWDIS, GSR |

| 10           |          | DONE            | GWDIS, GSR      | GOE             |

| 11           |          | DONE            | GOE             | GWDIS, GSR      |

| 12           |          |                 | DONE            | GOE, GWDIS, GSR |

| 13           |          | GOE, GWDIS, GSR | DONE            |                 |

| 14           |          | GOE             | DONE            | GWDIS, GSR      |

| 15           |          | GOE, GWDIS      | DONE            | GSR             |

| 16           |          | GWDIS           | DONE            | GOE, GSR        |

| 17           |          | GWDIS, GSR      | DONE            | GOE             |

| 18           |          | GOE, GSR        | DONE            | GWDIS           |

| 19           |          |                 | GOE, GWDIS, GSR | DONE            |

| 20           |          | GOE, GWDIS, GSR |                 | DONE            |

| 21 (Default) |          | GOE             | GWDIS, GSR      | DONE            |

| 22           |          | GOE, GWDIS      | GSR             | DONE            |

| 23           |          | GWDIS           | GOE, GSR        | DONE            |

| 24           |          | GWDIS, GSR      | GOE             | DONE            |

| 25           |          | GOE, GSR        | GWDIS           | DONE            |

# TecStar 5-7 WakeUpタイムチャート

- 1. PROGRAM DONEコマンド・フレームの最終バイト

- 2. PROGRAM\_DONEコマンドの実行最終ステート。もしPROGRAM\_DONE命令にCRCが付加されていた場合、CRC比較はこの時点で完了される。

- 3. 内部DONEビット(\*)が開放されるには、複数のクロック・サイクルが必要となる場合がある。

- 4. PLLがロックするまで、複数のクロック・サイクルが必要。もしPLLのロック信号に依存しない(Wake\_on\_lockを未設定)場合は、1 クロック・サイクルのみ。

\*: 内部DONEビットはデバイス内部の制御用で、DONEピンと区別されています。またそれらの信号遷移タイミングも異なります。

## ECP2/MのSPI-Flash,Serial-ROMについて

# TecStar 6-1 コンフィグレーションビットサイズ一覧

| 型番      | LUT数 | 圧縮なし<br>デバイスコンフィグレーション容量<br>(MBits) | 圧縮あり予想<br>デバイスコンフィグレーション容量<br>(MBits) |

|---------|------|-------------------------------------|---------------------------------------|

| ECP2-6  | 6K   | 1.6                                 | TBD                                   |

| ECP2-12 | 12K  | 3.0                                 | TBD                                   |

| ECP2-20 | 20K  | 4.7                                 | TBD                                   |

| ECP2-35 | 35K  | 6.6                                 | TBD                                   |

| ECP2-50 | 50K  | 9.4                                 | TBD                                   |

| ECP2-70 | 70K  | 14                                  | TBD                                   |

| ECP2M35 | 35K  | 10.3                                | TBD                                   |

- •"Generate Bitstream Data"の"PropertiesにあるCompress bit stream"をTrueとすることで、生成されるファイル(BITファイル)が圧縮モードで生成されます。圧縮あり時の圧縮率は、設計により変わります。一般的に小規模の設計では、圧縮率が高くなり、大規模で複雑な設計では、圧縮率が低くなります。

- •上記に記載されていないデバイスに関しましては、弊社営業或いは技術までお問い合わせください。

## 5 tar 6-2 SPI Serial Flash Vendor List

| Vendor                     | Part Number |   |

|----------------------------|-------------|---|

| ST Microelectronics        | M25Pxx      | H |

| Winbond                    | W25Pxx      | Н |

| Spansion                   | S25FLxx     | H |

| NexFlash                   | NX25Pxx     | П |

| Atmel                      | AT25Fxx     | H |

| Silicon Storage Technology | SST25VFxx   | Н |

|                            | SST25LFxx   |   |

- 上記はLattice社ECP2/Mとダイレクトに繋げることのできるSPI-Flashのベンダーリストになります。

- 上記Flashに書き込む為にはispVMsystemを使用して書込みを行ないます。SPI-Flashの選定の際にはこちらのソフトが対応しているかどうかにも注意をして〈ださい。(可能であれば、SPI-Flashを選定の際に弊社までご一報願います)

- SPI-FLASHは3.3V品をお使いください。Vccio8には3.3Vを供給してください。

## ispVMsystemを使用したECP2/Mへの書込みについて

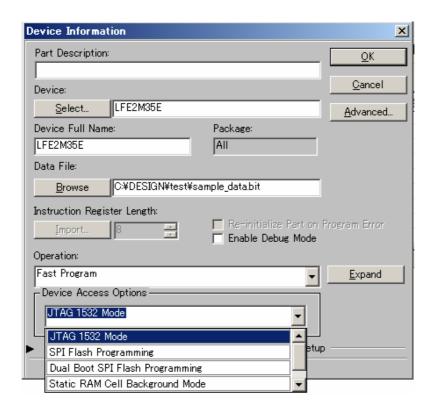

SPIフラッシュ及びデバイスにコンフィグレーションデータを書き込むにはispVM Systemを使用します。この項で はSPIフラッシュ及びデバイスへのアクセス方法について説明します。

Device InformationのウィンドウでDevice Access Optionsの欄でアクセス方法を選択します。

### JTAG 1532 Mode

デバイスのJTAGポートを経由してデバイスのSRAM領域にアクセスします。アクセス中はデバイスはプログラムモード(全I/Oトライステート)になります。

## Static RAM Cell Background Mode

デバイスのJTAGポートを経由してバックグラウンドでデバイスからリード、イレース、ベリファイを行います。デバイスの動作は止まりません。

## SPI Flash Programming

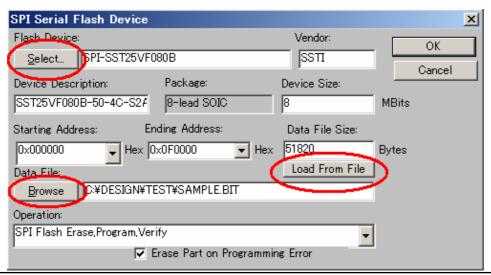

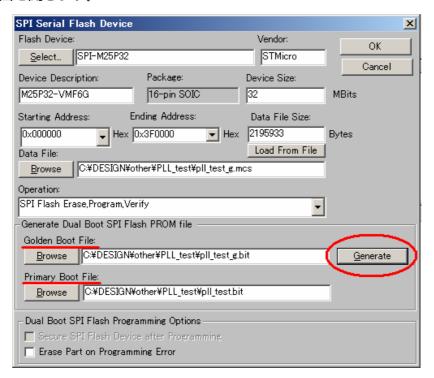

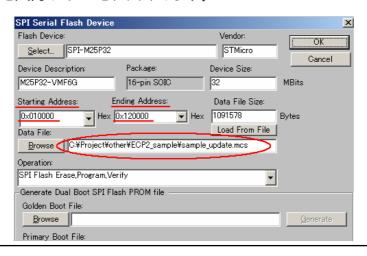

- デバイスのJTAGポートを経由してSPIフラッシュにアクセスします。下図のようなフラッシュROMの設定画面 が現れますので、お使いになるフラッシュROMを選択後、コンフィグレーションデータを入力し、Load From Fileをクリックしてデータサイズを表示します。その後オペレーションを選択してOKをクリックします。

- **Dual Boot SPI Flash Programming**

- デュアルブート機能を使用するときはこのモードで書き込みを行います。 詳細は「7-3 デュアルブートについて」を参照してください。

- Serial Mode

\*TBD

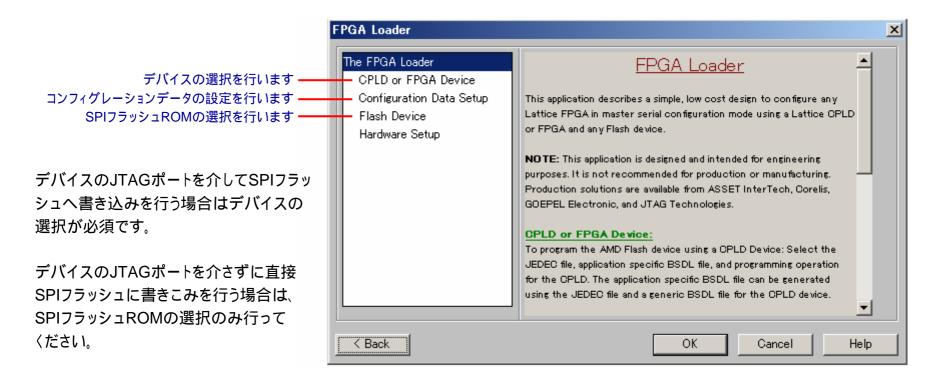

- FPGA Loaderによる書き込み

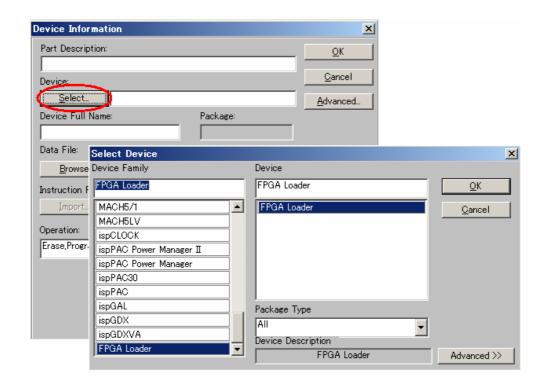

- デバイスのJTAGポートを介してSPIフラッシュへのアクセス、もしくはJTAGポートを介さずに直接SPIフラッ シュにアクセスを行います。

- Device InformationのSelect項目からFPGA Loaderを選択します。

Configuration Data Setupのオプションでファイルのマージ(連結)を行う部分がありますが、 2007/02/06 時点ではFPGA Loaderによるマージは行えませんので、UFWにて行います。 詳細は「3-12 Bitstreamの圧縮、マージについて」の項を参照してください。

## **lecStar 7-2** Bitstreamの圧縮、マージについて

### Bitstreamの圧縮

- 1. ispLEVERで圧縮する

- ➤ Design PlannerのSpreadsheet ViewでGlobalタブを選択し、COMPRESS\_CONFIGをONにして Bitstreamを生成します。

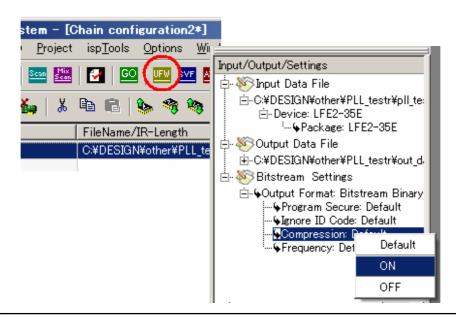

- 2. UFWで圧縮する

- ▶ ispVM SystemからUFWを起動します。 Bitstream SettingsでCompressionの部分を右クリックし、ONにしてジェネレートします。

## TecStar 7-2 Bitstreamの圧縮、マージについて

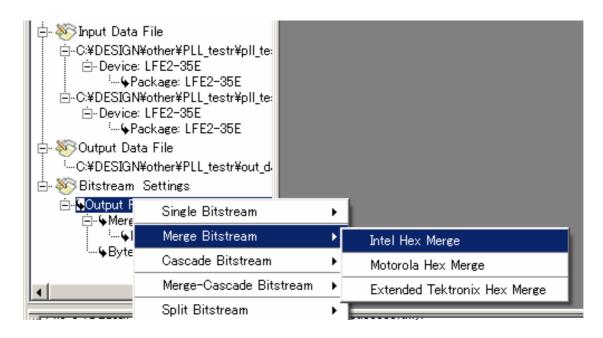

## Bitstreamのマージ(連結)

- UFWで行います。Bitstream SettingsのOutput Formatの部分を右クリックし、Merge Bitstreamから Intel Hex Mergeを選択します。

- Input Data Fileをダブルクリックし、マージするBitstreamを2つ選択し、ジェネレートしてください。

- マージされたファイル(.mcs)が生成されます。

## デュアルブートファイルの生成

- Device InformationのウィンドウでDual Boot SPI Flash Programmingを選択し、以下の画面を開きます。

Golden Boot FileとPrimary Boot Fileを選択し、Generateをクリックすると、自動的に2つのbitstreamがマージされたファイルが生成されます。マージされたファイルはData Fileの欄に自動的に入り、データサイズがData File Sizeの欄に表示されます。OKをクリックすると、Device Informationのウィンドウに戻ります。

Corporation

**Bringing the Best Together**

## デュアルブートモードの注意点

- 前ページで説明した方法はSPIフラッシュROMに初期の書き込みを行う時の方法です。フィールド上でアップデートする場合は、プライマリデータのみアップデートするようにしてください。

- デュアルブートは1つのSPIフラッシュメモリの中にプライマリセクターとゴールデンセクターの2つの領域を確保します。それぞれにビットストリームデータを書き込むのでメモリの容量は通常の倍必要になります。通常サイズのビットストリームを書き込む時に使用するメモリ容量は以下の表及びテクニカルノートTN1108を参照してください。

| Density | Bitstream Size (Mb) | Required Boot Memory (Mb) |

|---------|---------------------|---------------------------|

| ECP2-6  | 1.6                 | 2                         |

| ECP2-12 | 3                   | 4                         |

| ECP2-20 | 4.7                 | 8                         |

| ECP2-35 | 6.6                 | 8                         |

| ECP2-50 | 9.4                 | 16                        |

| ECP2-70 | 14                  | 16                        |

| ECP2M35 | 10.3                | 16                        |

- デュアルブート用に用意するビットストリームファイルを暗号化する場合は2つのbitstream共に暗号化 する必要があります。その際の共通鍵は両方のbitstreamで共通のものを使うようにしてください。

- 電源立上がり時にPROGRAMNピンがトグルされるか、JTAG経由でリフレッシュがかけられた場合に、ECP2MはPrimary Boot Fileを呼び出し、コンフィグレーションが開始されます。このときにCRCチェックが行われエラーが確認された場合、Golden Boot Fileを呼び出してコンフィグレーションが行われます。Golden Boot Fileにもエラーが確認された場合は、コンフィグレーションは中止されます。(このとき、INITNピンはLowにドライブされます。)

- フィールドアップデートの行い方

- フィールドでアップデートする際は、プライマリデータのみアップデートします。

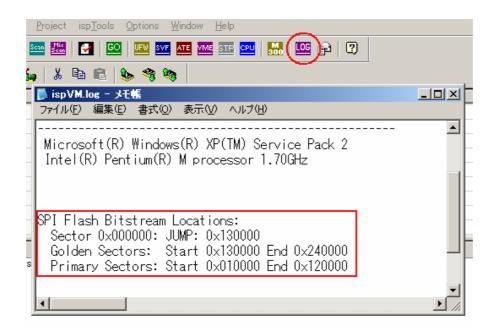

- デュアルブートファイルを生成すると、下図に示すLogファイルにプライマリファイルと ゴールデンファイルのスタート/エンドアドレスが表示されます。

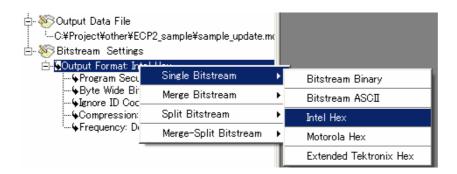

アップデートするプライマリファイルをUFWで圧縮してmcsファイルにします。

Bitstream Setting Single Bitstream IntelHexを選択してからCompressionをONにして生成します。

Device InformationのウィンドウでDual Boot SPI Flash Programmingを選択し、Data Fileとして プライマリデータのmcsファイルを選択し、ログファイルに表示されているプライマリデータのスタート アドレスとエンドアドレスを入力してOKをクリックします。

# TecStar Revision History

| Revision:      | Data:     | Author:           | Modify:                                                                                              |

|----------------|-----------|-------------------|------------------------------------------------------------------------------------------------------|

| First Revison0 | 2006/1/25 | Machida/Tecstar   |                                                                                                      |

| Revision.1     | 2007/2/1  | Machida/Tecstar   | 1-1項目の電源ピン扱い一覧の修正(Update)<br>2-1項目のDDRメモリI/Fの扱い追記                                                    |

| Revision.2     | 2007/2/6  | Nakatsuka/Tecstar | 1-2項目のD[7:0],DOUTピンに関して内部pull-up追記<br>(Update)<br>7-項目新規追加 ispVM Systemの扱い及びBitstream<br>の圧縮、マージについて |

| Revision.3     | 2007/3/20 | Machida/Tecstar   | 1-1項目へ暗号化使用の場合のシーケンス制御につい<br>て追加<br>1-1項目へ電源シーケンスまとめを追加                                              |

| Revision.4     | 2007/4/3  | Nakatsuka/Tecstar | 7-3項目デュアルブートの使用法を追加                                                                                  |

| Revision.5     | 2007/4/16 | Machida/Tecstar   | 1-1項目へConfiguration専用ピンのPull-up処理について追加                                                              |

| Revision.5.1   | 2007/7/23 | Machida/Tecstar   | 1-1項目電源ピンの取り扱いに関する注意事項に<br>PROGRAMNに関する事項追加。<br>2-2項目対応するI/OのI/F一覧のPCIサポート修正                         |

| Revision 5.2   | 2007/8/6  | Machida/Tecstar   | 2-7項目 GearingBox使用時の注意点追加<br>コンフィグレーション項目にスレーブパラレル時の注意<br>点追加                                        |

# TecStar Revision History

| Revision:    | Data:      | Author:             | Modify:                                                              |

|--------------|------------|---------------------|----------------------------------------------------------------------|

| Revision6.0  | 2007/9/11  | Machida/Tecstar     | 2-8 I/Oピンの挙動の項目追加<br>3-4 SPIモード詳細にDONE_EXの設定を追加                      |

| Revision 6.1 | 2007/11/14 | Cho / TecStar       | 3-3から3-6まで、SPI各モード各方式の接続図を訂正<br>3-4 Wake-upシーケンス変更を追加                |

| Revision 6.2 | 2007/12/10 | Nakatsuka / Tecstar | 3-3から3-9まで、Pull up / Pull down抵抗の値を修正                                |

| Revision6.3  | 2008/6/9   | Machida/Tecstar     | 1-1電源ピンの扱いにおいてVCCIB,VCCOBの扱いを<br>修正(Openで問題ありません Openにしておくべきに<br>変更) |

| Revision6.4  | 2008/8/8   | Matsuo/Tecstar      | 1-2コンフィグ関連ピンにおいてECP2M50/70/100の<br>DualPurposeピンの挙動について追記            |

| Revision6.5  | 2009/1/6   | Kitayama/Tecstar    | 3-4~3-6 Pull-up抵抗値を修正<br>目次追加                                        |

|              |            |                     |                                                                      |

|              |            |                     |                                                                      |

|              |            |                     |                                                                      |

|              |            |                     |                                                                      |