CrossLink-NX LVDS to MIPI DSI (Hard D-PHY) リファレンスデザインユーザーマニュアル

Aug-2022

### 免責事項

本ドキュメントに含まれる情報、及び本ドキュメントの対象であるリファレンスデザインの内容、動作、特性、品質に対して、マクニカはいかなる保証も行いません。また、本ドキュメントに含まれる情報、及び本ドキュメントの対象であるリファレンスデザインは全て現状有姿にて提供され、これに対する改版や技術サポートのご依頼に関しては理由の如何を問わずお控え頂くようお願いしております。お客様ご用途における使用可否の判断、使用の際の動作確認、お客様製品への実装における適合性や安全性の確認、法的要件の確認はお客様にて実施頂きますようお願いいたします。これらに対してもマクニカは一切の責任を負うことが難しく、いかなる保証もいたしかねます。また、本ドキュメントの情報、及びドキュメントの対象であるリファレンスデザインはマクニカの所有物であり、予告なしに変更を加えることがございますので予めご了承ください。

### **Table of Contents**

- デザイン概要

- デザインフォルダ構成

- 回路ブロック図 3.

- デザインポート説明

- 各モジュール概要

- ファンクションシミュレーション 6.

### 1. デザイン概要

- ◆ 本デザインはCrossLink-NXのHard D-PHYを用いたLVDS to DSIリファレンスデザインです。

- Full-HD(1080 60p)のデータをOdd/Evenピクセルに分離された形で7:1 LVDS 2chで受信することを想定しています。

また、LVDS側のデータパッキングはOpenLDIの形式を取っています。

- LVDS受信クロックレートは74.25MHz、データレートは74.25MHz x 7 = 519.75Mbps/Laneとなっています。

- 受信したOdd/Evenピクセルデータを内部回路で結合し、MIPI DSIで送信します。

- MIPI DSI Txレーン数は4Lane、D-PHYでのシリアライズ設定は8:1としており、バイトデータは32bitの設定です。

- 送信データレートは、2200(H) x 1125(V) x 24(bit) x 60(fps) / 4(lane) = 891Mbps/Laneとなっています。

- 本デザインではLattice社IP "CSI-2/DSI D-PHY Transmitter (v1.7.1)" と "Pixel to Byte Converter (v1.4.0)" を使用しています。IPのユーザーガイドについては以下を参照してください。

CSI-2/DSI D-PHY Transmitter

http://www.latticesemi.com/view\_document?document\_id=52453

Pixel to Byte Converter

http://www.latticesemi.com/view\_document?document\_id=52809

- デザイン動作はModelSim Lattice Editionでのファンクションシミュレーションにて確認しています。実機上での確認はしておりません。

- 本デザインはRadiant3.2でコンパイルされており、論理合成ツールはSynplify Proを使用しています。

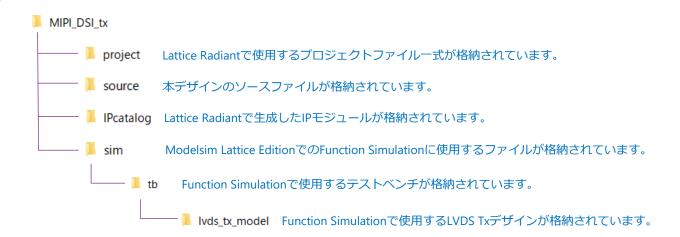

## 2. デザインフォルダ構成

本デザインのフォルダ構成を以下に示します。

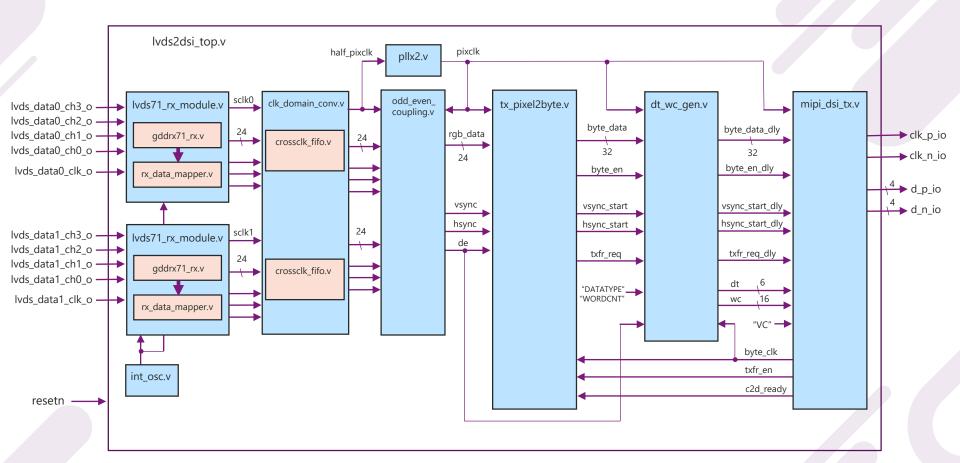

## 3. 回路ブロック図

# 4. デザインポート説明

| ポート名                 | 入出力方向 | 説明                           |

|----------------------|-------|------------------------------|

| resetn               | 入力    | リセット入力(Active-Low)           |

| lvds_data0_ch[3:0]_i | 入力    | LVDS ch0入力データ                |

| lvds_data0_clk_i     | 入力    | LVDS ch0入力クロック               |

| lvds_data1_ch[3:0]_i | 入力    | LVDS ch1入力データ                |

| lvds_data1_clk_i     | 入力    | LVDS ch1入力クロック               |

| clk_p_io             | 出力    | MIPI D-PHY差動クロック出力(Positive) |

| clk_n_io             | 出力    | MIPI D-PHY差動クロック出力(Negative) |

| d_p_io               | 出力    | MIPI D-PHY差動データ出力(Positive)  |

| d_n_io               | 出力    | MIPI D-PHY差動データ出力(Negative)  |

#### ■ top.v

本デザインのトップモジュールです。DSIパケットで使用するVC、DT、WCはトップモジュールからパラメータとして与えます。

#### ■ int osc.v

内部オシレータモジュールです。gddrx71\_rx.vのイニシャライズシーケンス用のクロックを生成しています。

#### ■LVDS71\_rx\_module

7:1LVDS受信モジュールです。内部に7:1デシリアライズを行うgddrx71\_rx.vとrx\_data\_mapper.vを持っており、受信したOpenLDI形式のLVDSデータをRGB888のパラレルデータの形で出力します。

#### ■ gddrx71\_rx.v

LVDS受信データを7:1デシリアライズするモジュールです。Odd/Evenピクセルに分けられたFull-HDデータをOpen-LDI形式で受信するため、 148.5MHz/2 x7 = 519.75Mbpsのデータを4Lane受信する設定になっています。

■ rx\_data\_mapper.v

gddrx71\_rx.vから出力された28bitのデータをRGB888のパラレルデータ形式に並べ替えを行うモジュールです。並べ替えはOpenLDI形式のLVDSをgddrx71\_rx.vでデシリアライズされたものをRGB888のパラレルデータの形に変換するように設計されています。

■ clk\_domain\_conv.v

LVDSで受信した2chのデータを片方のchのクロックに同期させるモジュールです。本デザインではch0(Oddピクセル)のクロックに同期させています。

**■** crossclk fifo.v

clk\_domain\_conv.v内でのクロック載せ替えに使用するFIFOモジュールです。

■ pllx2.v

Odd/Evenピクセル結合後のピクセルクロックを生成するPLLモジュールです。入力クロック(74.25MHz)に対して 2 倍(148.5MHz)の周波数の クロックを生成しています。

■ odd\_even\_coupling.v

Odd/Evenピクセルデータ及び同期信号を結合するモジュールです。結合後のピクセルデータ及び同期信号は148.5MHzクロックに同期して出力されます。

2022/12/23

#### ■ dt\_wc\_gen.v

Data Type(dt)とWord Count(wc)をショートパケットのパケットヘッダ、ロングパケットのパケットヘッダそれぞれに対して生成します。 また、CSI-2/DSI D-PHY Transmitterが要求する以下の入力タイミングを満たすようにタイミング調整を行います。

#### 3.2. Short Packet Transmission in CSI-2/DSI Interfaces

Figure 3.3. D-PHY Tx Input Bus for Short Packet Transmission in CSI-2/DSI Interfaces

#### 3.3. Long Packet Transmission in CSI-2/DSI Interface

Figure 3.4. D-PHY Tx Input Bus for Long Packet Transmission in CSI-2/DSI Interface

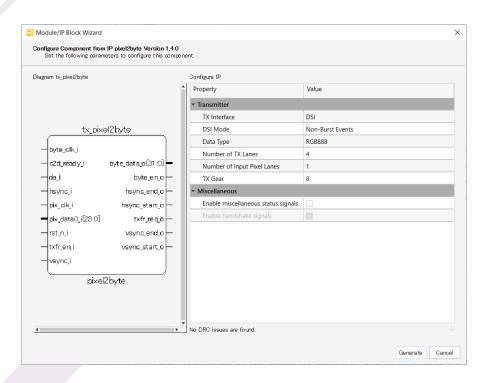

#### ■ tx pixel2byte.v

CSI-2/DSI D-PHY Transmitter IPに入力するバイトデータと同期信号タイミングパルスをピクセルデータとV Sync, H Syncから生成するモジュールです。 Pixel to Byte Converter IPを使用しています。設定は以下の通りです。

- Tx Interface DSIを選択しています。

- DSI Mode "Non-Burst Events"を選択しています。DSI規格の"Non-Burst with Sync Events"に相当し、V Sync, H Syncの開始エッジのみショートパケットを生成 するモードです。

- DataType RGB888を選択しています。

- Number of TX Lanes 4Laneに設定しています。

- Number of Input Pixel Lanes 本デザインではRGB888入力1chのため、1Laneに設定しています。

- TX Gear 8に設定しています。D-PHYモジュールにて8:1シリアライズを行う設定です。

2022/12/23

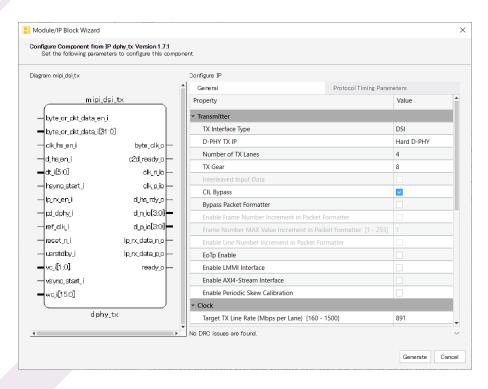

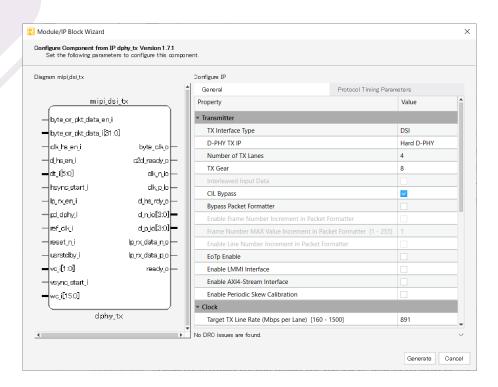

#### ■ mipi dsi tx.v

Pixel to Byte Converter IPにて生成されたバイトデータとvsync\_start/hsync\_startパルス、及びパケットヘッダで使用するVC、DT、WCからDSIパケットを 生成してD-PHYで送信するモジュールです。 CSI-2/DSI D-PHY Transmitter IPを使用しています。設定は以下の通りです。

- **■** Tx Interface DSIを選択しています。

- **D-PHY TX IP** "Hard D-PHY"を選択しています。

- Number of TX Lanes 4Laneに設定しています。

- TX Gear **8に設定しています。D-PHYモジュールにて8:1シリアライズを行う設定です。**

- **CIL Bypass**

Control and Interface Logic (CIL)のバイパス設定です。デフォルトのままチェックを入れており、バイパスする設定にしています。CILはデータとクロッ クの状態遷移のコントロールを行うハードブロックで、使用しない場合はソフ トロジックが使用されます。

■ Bypass Packet Formatter バイトデータからDSIパケットを生成する際に規格上必要なSync Code (0xB8) とtHS-TRAIL期間のデータ反転を自動で行う回路のバイパス設定です。 本デザインではIPに自動生成することを意図してチェックを外しています。

2022/12/23

#### **■ EoTp Enable**

End of Transmission packet (EoTp)の付与設定です。 デフォルト設定(チェック無し)で、EoTpを付与しない設定にしています。

#### **■** Enable LMMI Interface

Hard D-PHYモジュール内蔵のPLLレジスタ設定用のLMMI Interface使用有無の 設定です。使用しないためチェックを外しています。

#### **■** Enable AXI4-Stream Interface

バイトデータおよびパケットヘッダ情報をAXI4-Stream Interfaceで入力する場 合にチェックを入れます。本デザインでは使用しないためチェックを外してい ます。

#### ■ Enable Periodic Skew Calibration

チェックを入れるとSkew Calibrationパターンの送信トリガ用ポートが追加さ れます。本デザインでは使用しないためチェックを外しています。

2022/12/23

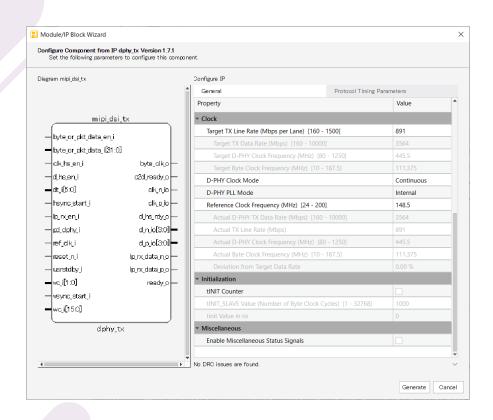

■Target TX Lane Rate (Mbps per Lane)

RGB888 1080 60pを4Laneで送信するため、

2200(H) x 1125(V) x 24(bit) x 60(fps) / 4(lane) = 891 と設定しています。

#### ■ D-PHY Clock Mode

Clock LaneでLPモードを使用するかどうかの設定です。LPモードに入れず常に 出力するため"Continuous"を選択しています。

- D-PHY PLL Mode D-PHYモジュール内部のPLLを使用するため"Internal"を選択しています。

- Reference Clock Frequency RGB888 1080 60pパラレル入力のピクセルクロックを使用する構成のため、148.5MHzに設定しています。

#### **■ tINIT Counter**

D-PHYモジュールのイニシャライゼーション完了を遅らせるディレイカウンタの使用有無設定です。D-PHY Rxデバイスが起動時に要求するStop State(LP-11)の時間を満たすための調整用に必要に応じて使用します。本デザインでは使用していません。

■ Enable Miscellaneous Status Signal デバッグ用途に使用される各種信号をポートに出力するかどうかの設定です。 本デザインではチェックを外しています。

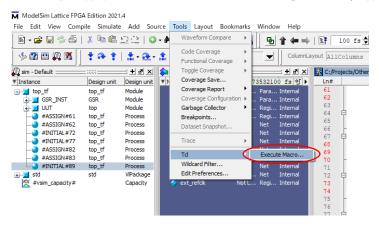

ファンクションシミュレーションを実施するには、ModelSim Lattice Editionを使用します。 シミュレーション開始前にinit.doファイル内の以下のディレクトリ指定をユーザー環境のsimフォルダのパスに変更する必要があります。 Init.doファイルはsimフォルダの中に格納されています。

Model Simを起動後、Tools > Tcl > Execute Macro からinit.doファイルを起動します。

Init.doの編集方法、doファイルでのシミュレーション詳細については、以下のページの「ModelSim Lattice Edition DO マクロ ユーザーガイド」を参照してください。

https://www.macnica.co.jp/business/semiconductor/articles/lattice/132003/

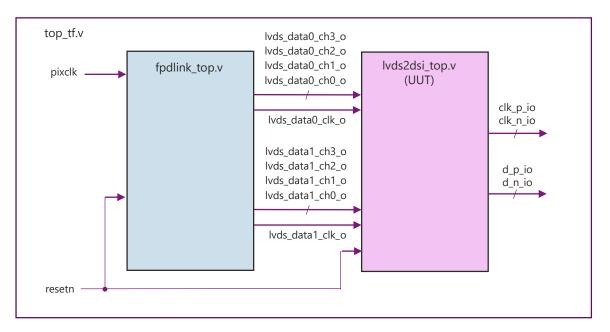

### テストベンチ構成概要図

テストベンチ上でシミュレーション対象のdsi\_tx\_top.vに対し、fpdlink\_top.vから LVDS 2chを出力しています。

fpdlink\_top.v内部ではFull-HD(1080p60)RGB888のカラーバージェネレータから出力されるパラレルデータをOdd/Evenピクセルに分離しており、このデータをOpenLDI形式のLVDS 2chで出力します。

lvds2dsi\_top.vでこのLVDSデータ2chを受信し、Odd/Evenピクセルを結合してMIPI DSIで出力する様子を観測しています。

上図は送信モジュール(fpdlink top.v)にてRGB888データをOdd/Evenピクセルに分割し、OpenLDI形式のLVDSで送信するまでの全体像です。 ※テスト上のモジュールのため、実際のデザインとは関係が無い部分になります。

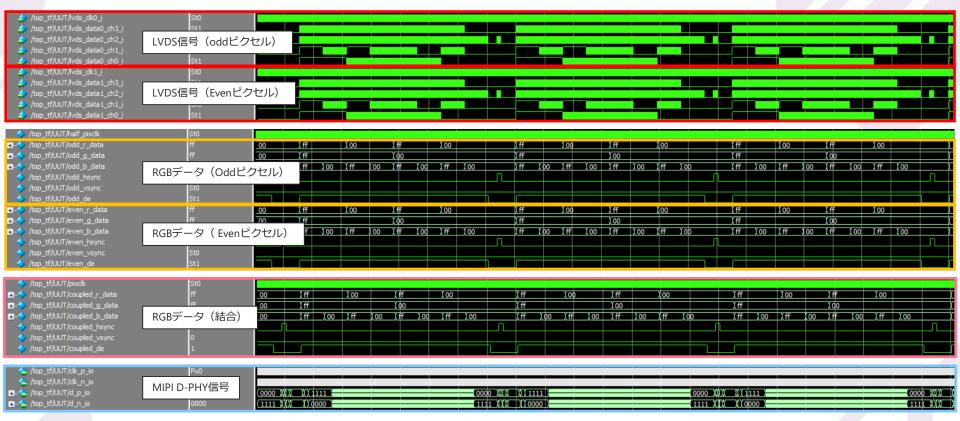

**MACNICA**

上図は本デザインのLVDS受信部からMIPI DSI出力までの段階的なデータの遷移になります。LVDSで受信したOdd/Evenデータはch毎にRGB888データに変換され、 その後連結してFull-HDのRGB888データとなります。このFull-HD RGB888データがMIPI D-PHY(DSI)で送信されています。

**MACNICA**

2022/12/23

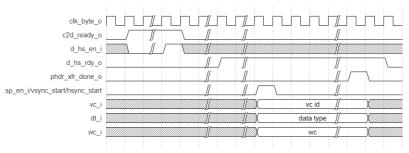

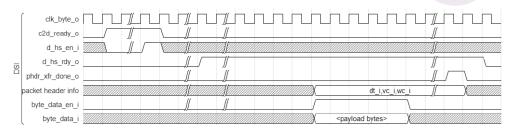

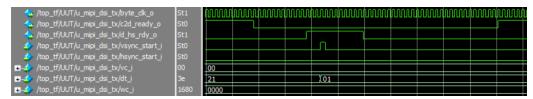

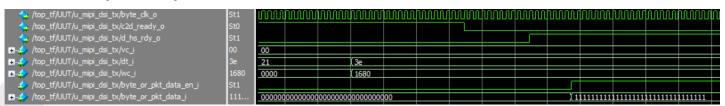

以下はdt\_wc\_gen.vにて生成しているDT, WCのシミュレーション波形です。

■Short Packet (V sync): mipi\_dsi\_tx.vへのvsync\_start\_iパルス立ち上がりタイミングとVC, WC, DT(0x01: V Sync Start)の入力タイミングを合わせています。

■Short Packet (H sync): mipi\_dsi\_tx.vへのhsync\_start\_iパルス立ち上がりタイミングとVC, WC, DT(0x21: H Sync Start)の入力タイミングを合わせています。

| /top_tf/UUT/u_mipi_dsi_tx/byte_dk_o     | St1  |      |     | wwwww | nnunnunn | nnnnnnn | າກການ |

|-----------------------------------------|------|------|-----|-------|----------|---------|-------|

| /top_tf/UUT/u_mipi_dsi_tx/c2d_ready_o   | St0  |      |     |       |          |         |       |

| /top_tf/UUT/u_mipi_dsi_tx/d_hs_rdy_o    | St1  |      |     |       |          |         |       |

| /top_tf/UUT/u_mipi_dsi_tx/vsync_start_i | St0  |      |     |       |          |         |       |

| /top_tf/UUT/u_mipi_dsi_tx/hsync_start_i | St0  |      | ┸   |       |          |         |       |

| - /top_tf/UUT/u_mipi_dsi_tx/vc_i        | 00   | 00   |     |       |          |         |       |

| - /top_tf/UUT/u_mipi_dsi_tx/dt_i        | 3e   | 01   | (21 |       |          |         |       |

| /top_tf/UUT/u_mipi_dsi_tx/wc_i          | 1680 | 0000 |     |       |          |         |       |

■Long Packet: mipi\_dsi\_tx.vに入力されるbyte\_or\_pkt\_data\_en\_iがHigh (Enable) になるよりも前にVC, WC (0x1680), DT(0x3E: RGB888)を合わせています。 ※ WC = 1920 x 3 byte = 5760byte = 0x1680

2022/12/23

# **Revision History**

| Date      | Revision | Page | Change Information |

|-----------|----------|------|--------------------|

| 2022/12/6 | 1.0      |      | First Revision     |

|           |          |      |                    |

|           |          |      |                    |

|           |          |      |                    |