**CrossLink-NX**MIPI DSI (Hard D-PHY) to FPD-LINK

リファレンスデザインユーザーマニュアル

# MACNICA

Aug-2022

### 免責事項

本ドキュメントに含まれる情報、及び本ドキュメントの対象であるリファレンスデザインの内容、動作、特性、品質に対して、マクニカはいかなる保証も行いません。 また、本ドキュメントに含まれる情報、及び本ドキュメントの対象であるリファレンスデザインは全て現状有姿にて提供され、これに対する改版や技術サポートの ご依頼に関しては理由の如何を問わずお控え頂くようお願いしております。お客様ご用途における使用可否の判断、使用の際の動作確認、お客様製品への実装における 適合性や安全性の確認、法的要件の確認はお客様にて実施頂きますようお願いいたします。これらに対してもマクニカは一切の責任を負うことが難しく、いかなる保証 もいたしかねます。また、本ドキュメントの情報、及びドキュメントの対象であるリファレンスデザインはマクニカの所有物であり、予告なしに変更を加えることがご ざいますので予めご了承ください。

### **Table of Contents**

- デザイン概要

- デザインフォルダ構成

- 回路ブロック図 3.

- デザインポート説明

- 各モジュール概要

- ファンクションシミュレーション 6.

© Macnica, Inc.

### 1. デザイン概要

- 本デザインはCrossLink-NXのHard D-PHYを用いたDSI to FPD-Linkリファレンスデザインです。

- 受信データはFull-HD(1080 60p)を想定しており、ピクセルクロックは148.5MHzとして各種IP設定を行っています。

- MIPI DSI Rxレーン数は4Lane、D-PHYでのデシリアライズ設定は1:8としており、バイトデータは32bitの設定です。

- 受信データレートは、2200(H) x 1125(V) x 24(bit) x 60(fps) / 4(lane) = 891Mbps/Laneとなつています。

- 受信したデータはOddピクセル/Evenピクセルに分離され、FPD-Link 2chで送信されます。

- LVDS送信クロックレートは74.25MHz、データレートは74.25MHz x 7 = 519.75Mbps/Laneとなっています。

- 本デザインではLattice社IP "CSI-2/DSI D-PHY Receiver (v1.4.0)" と "Byte to Pixel Converter (v1.5.0)" 、及び"FPD-Link Transmitter (v1.1.0)" を使用しています。IPのユーザーガイドについては以下を参照してください。

CSI-2/DSI D-PHY Receiver

http://www.latticesemi.com/view\_document?document\_id=52445

Byte to Pixel Converter

http://www.latticesemi.com/view\_document?document\_id=52451

**FPD-Link Transmitter**

http://www.latticesemi.com/view\_document?document\_id=53005

- デザイン動作はModelSim Lattice Editionでのファンクションシミュレーションにて確認しています。実機上での確認はしておりません。

- 本デザインはRadiant3.2でコンパイルされており、論理合成ツールはSynplify Proを使用しています。

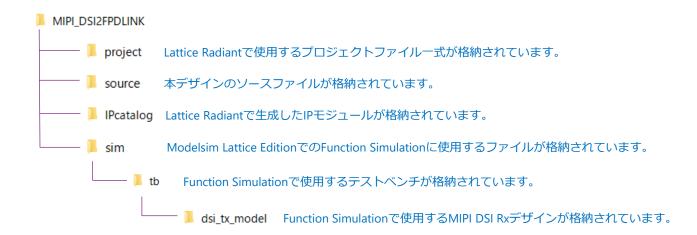

### 2. デザインフォルダ構成

本デザインのフォルダ構成を以下に示します。

Confidential

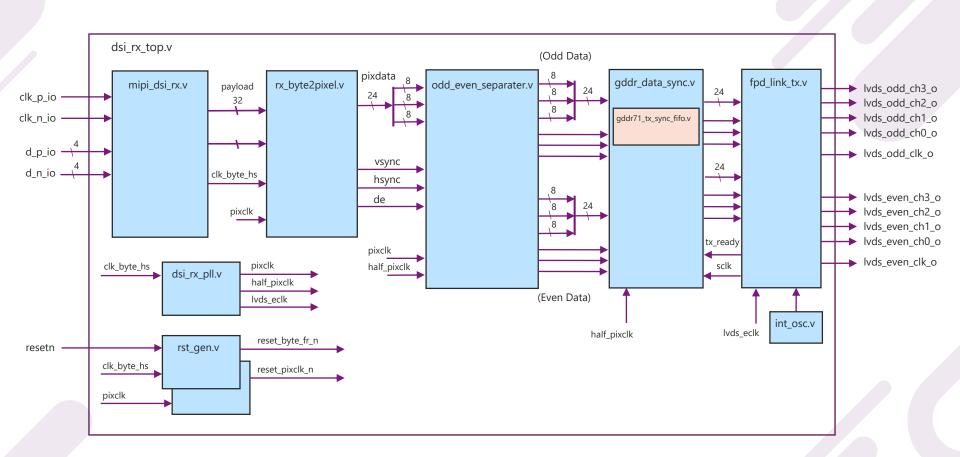

### 3. 回路ブロック図

# 4. デザインポート説明

| ポート名                | 入出力方向 | 説明                           |

|---------------------|-------|------------------------------|

| resetn              | 入力    | リセット入力(Active-Low)           |

| clk_p_io            | 入力    | MIPI D-PHY差動クロック出力(Positive) |

| clk_n_io            | 入力    | MIPI D-PHY差動クロック出力(Negative) |

| d_p_io              | 入力    | MIPI D-PHY差動データ出力(Positive)  |

| d_n_io              | 入力    | MIPI D-PHY差動データ出力(Negative)  |

| lvds_odd_ch[3:0]_o  | 出力    | OddピクセルLVDSデータ出力             |

| lvds_odd_clk_o      | 出力    | OddピクセルLVDSクロック出力            |

| lvds_even_ch[3:0]_o | 出力    | EvenピクセルLVDSデータ出力            |

| lvds_even_clk_o     | 出力    | EvenピクセルLVDSクロック出力           |

#### ■ top.v

本デザインのトップモジュールです。

#### ■ rst\_gen.v

非同期リセットのresetnを入力クロックで同期化するモジュールです。mipi\_dsi\_rx.vとbyte2pixel.vが同期リセット入力を必要とするため、本モジュールで リセットの同期化を行っています。

#### ■ dsi\_rx\_pll.v

mipi\_dsi\_rx.vで生成されたバイトクロックからRGB888パラレルデータのピクセルクロック、ピクセルクロックの1/2周波数のクロック、7:1LVDS送信用の クロック(ピクセルクロック周波数 x 1/2 x 3.5)を生成するPLLモジュールです。

#### ■ even\_odd\_separator.v

RGB888のピクセルデータ及び同期信号をoddピクセルとevenピクセルに分離するモジュールです。分離後のピクセルクロック周波数は元のピクセルクロックの半分(本デザインでは148.5MHzの半分の74.25MHz)となります。

gddr\_data\_sync.v

gddr71\_tx\_sync\_fifo.vのライトイネーブル、リードイネーブルを制御するモジュールです。

■ gddr71\_tx\_sync\_fifo.v

half\_pixclkに同期したピクセルデータをfpd\_link\_tx.vの内部クロックに載せ替えるためのFIFOモジュールです。 fpd\_link\_tx.vモジュールでは最終出力段の DDRレジスタで使用するlvds\_eclkを分周したクロック(sclk)でピクセルデータを運用します。このクロックとfpd\_link\_tx.v入力側のピクセルクロックは、 正しくデザインされた場合同じ周波数になりますが位相が異なるため、正しくデータのラッチができないことがあります。本FIFOモジュールではこの位相差 の吸収を行っています。

■ int osc.v

gddr71\_tx.vのイニシャライゼーションに使用する低速クロックを生成している内部オシレータモジュールです。

■ fpd\_link\_tx.v

RGBパラレルデータをFPD-Linkに変換するモジュールです。

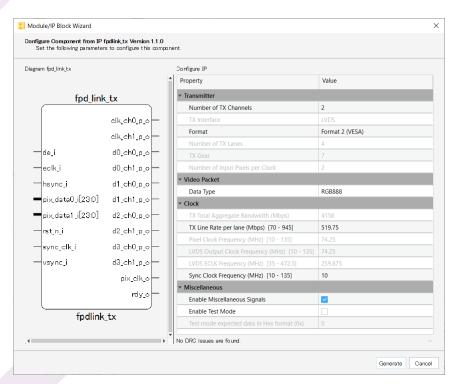

#### **■** fpd\_link\_tx.v

RGBパラレルデータをFPD-Linkに変換するモジュールです。IP Catalogでの設定内容は以下の左図の通りで、Odd/Evenピクセルの2ch送信のためNumber of TX Channelsは "2" に設定しています。変換後のデータフォーマットは右図のようになっています。

2022/12/9

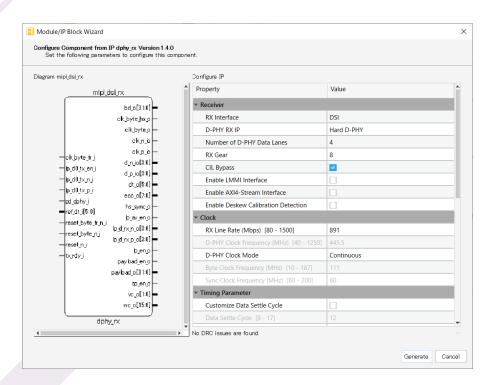

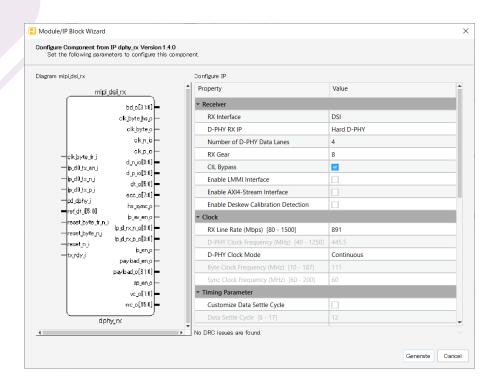

#### ■ mipi\_dsi\_rx.v

MIPI D-PHYシリアルデータをバイトデータに変換するモジュールで、ショートパケット/ロングパケットの検出と、設定によってロングパケット内に含まれるペイロードデータの抽出まで行います。 CSI-2/DSI D-PHY Receiver IPを使用しています。設定は以下の通りです。

- Rx Interface DSIを選択しています。

- D-PHY RX IP Hard D-PHYを選択しています。

- Number of D-PHY Data Lanes 4Laneに設定しています。

- ■RX Gear 8に設定しています。D-PHYモジュールにて1:8デシリアライズを行う設定です。

- **CIL Bypass**

Control and Interface Logic (CIL)のバイパス設定です。デフォルトのままチェックを入れており、バイパスする設定にしています。CILはデータとクロックの状態遷移のコントロールを行うハードブロックで、使用しない場合はソフトロジックが使用されます。

#### **■** Enable LMMI Interface

Hard D-PHYモジュール内蔵のPLLレジスタ設定用のLMMI Interface使用有無の設定です。使用しないためチェックを外しています。

2022/12/9

Confidential

#### ■ Fnable AXI4-Stream Interface

バイトデータおよびパケットヘッダ情報をAXI4-Stream Interfaceで出力する 場合にチェックを入れます。本デザインでは使用しないためチェックを外し ています。

#### ■ Enable Deskew Calibration Detection

チェックを入れるとDeskew Calibration用のポートが追加されます。シリア ルデータレートが1.5Gbps以下のデザインでのみ使用 or 未使用の選択が可能 で、1.5Gbpsより高いレートでは自動で使用する設定になります。本デザイ ンは1.5Gbps以下ですが、使用しないためチェックを外しています。

#### ■ RX Line Rate

Confidential

RGB888 1080 60pを4Laneで受信するため、 2200(H) x 1125(V) x 24(bit) x 60(fps) / 4(lane) = 891 と設定しています。

#### ■ D-PHY Clock Mode

Clock LaneがLPモードを使用するかどうかの設定です。今回はClock Laneで LPモードを使用しないため"Continuous"を選択しています。

#### **■** Customize Data Settle Cycle

D-PHY規格上のtHS-SETTLE時間を満たすためのパラメータのカスタマイズを 行います。デフォルトのまま使用しています。

2022/12/9

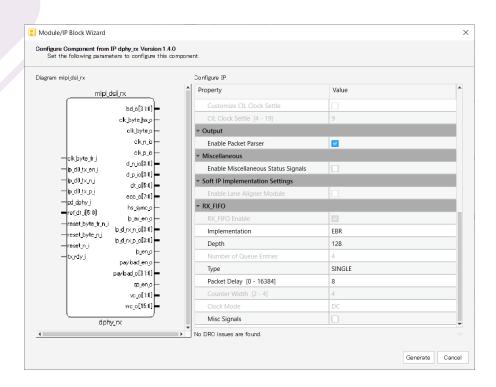

#### **■** Enable Packet Parser

チェックを入れることでバイトデータからペイロードデータを抽出 (Parsing) して出力します。本デザインではチェックを入れています。

### ■ Enable Miscellaneous Status Signals

デバッグ用途に使用される各種信号をポートに出力するかどうかの設定です。 本デザインではチェックを外しています。

#### RX FIFO

clk\_byte\_hs\_oに同期した出力データをclk\_byte\_fr\_iに載せ替えるために用意されたFIFOの設定です。微小な周波数偏差のある非同期クロックを使用する場合にその差分を吸収する用途、及び周波数偏差の無いクロックにおいても位相差を吸収する用途で使用します。本デザインではclk\_byte\_hs\_oをそのままclk\_byte\_fr\_iに接続しているため後者の用途ですが、各種FIFO設定はデフォルト設定のままです。

- ・Implementation FIFOの実装先をLUT(Distributed RAM)かEBRかを選択します。

- ・Depth FIFOの深さを設定します。

- ・Type SINGLE、QUEUE、PINGPONGから選択します。

- ・Packet Delay FIFOのEmpty Flagディアサーションからclk\_hs\_byte\_fr\_iによるリード 開始までのマージンをclk hs byte fr iサイクルで指定します。

- ・Misc Signals デバッグ用途に使用される各種信号をポートに出力するかどうかの 設定です。

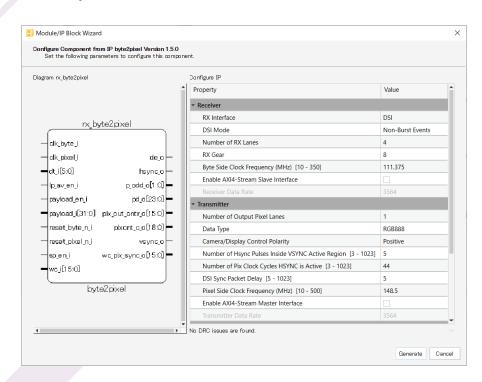

#### ■ rx\_byte2pixel.v

CSI-2/DSI D-PHY Receiver IPから出力されるバイトデータと各種ステータス信号からピクセルデータと同期信号(V Sync, H Sync, DE)を生成するモジュールです。Byte to Pixel Converter IPを使用しています。設定は以下の通りです。

■ Rx Interface DSIを選択しています。

#### ■ DSI Mode

"Non-Burst Events"を選択しています。DSI規格の"Non-Burst with Sync Events"に相当し、ショートパケットとしてV Sync StartとH Sync Startのみ使用するモードです。

- Number of RX Lanes 4Laneに設定しています。

- RX Gear

8に設定しています。D-PHYモジュールにて1:8デシリアライズを行う設定です。

■ Enable AXI4-Stream Slave Interface バイトデータおよびパケットヘッダ情報をAXI4-Stream Interfaceで入力する 場合にチェックを入れます。本デザインでは使用しないためチェックを外して います。

2022/12/9

Confidential

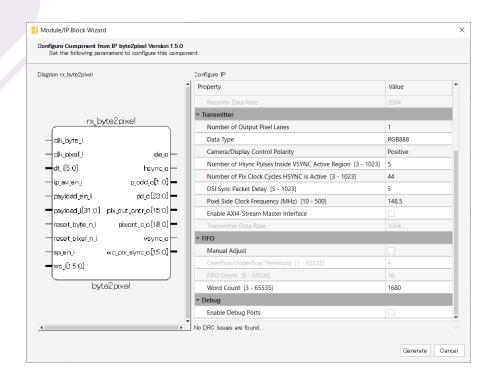

- Number of Output Pixel Lanes 本デザインではRGB888出力1chのため、1Laneに設定しています。

- Data Type RGB888を選択しています。

- Camera/Display/Control Polarity 出力する映像向期信号(V Sync, H Sync, DE)の極性を選択します。Positive (Active High) を選択しています。

- Number of Hsync Pulses Inside VSYNC Active Resion V Syncアクティブ期間のH Syncパルス数を設定します。出力されるV Syncの アクティブ期間に相当します。本デザインでは5と設定しています。

- Number of Pix Clock Cycles HSYNC is Active H Syncアクティブ期間のピクセルクロックサイクル数を設定します。出力され るH Syncのアクティブ期間に相当します。本デザインでは44と設定しています。

- DSI Sync Packet Delay 本モジュール内でのピクセルデータのバッファリングによって生じるピクセル データと同期信号(V Sync, H Sync)のスキューを補うための同期信号遅延設 定です。ピクセルクロックサイクル数で設定します。デフォルトの5に設定し ています。

- Fnable AXI-4 Stream Master Interface ピクセルデータ及びDE信号をAXI-4 Stream Interfaceで出力する場合にチェッ クを入れます。本デザインでは使用しないためチェックを外しています。

- **■** Enable Debug Ports デバッグ用途に使用される各種信号をポートに出力するかどうかの設定です。 本デザインではチェックを外しています。

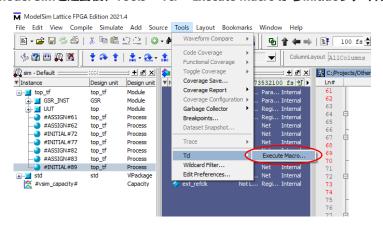

ファンクションシミュレーションを実施するには、ModelSim Lattice Editionを使用します。 シミュレーション開始前にinit.doファイル内の以下のディレクトリ指定をユーザー環境のsimフォルダのパスに変更する必要があります。 Init.doファイルはsimフォルダの中に格納されています。

Model Simを起動後、Tools > Tcl > Execute Macro からinit.doファイルを起動します。

Init.doの編集方法、doファイルでのシミュレーション詳細については、以下のページの「ModelSim Lattice Edition DO マクロ ユーザーガイド」を参照してください。

https://www.macnica.co.jp/business/semiconductor/articles/lattice/132003/

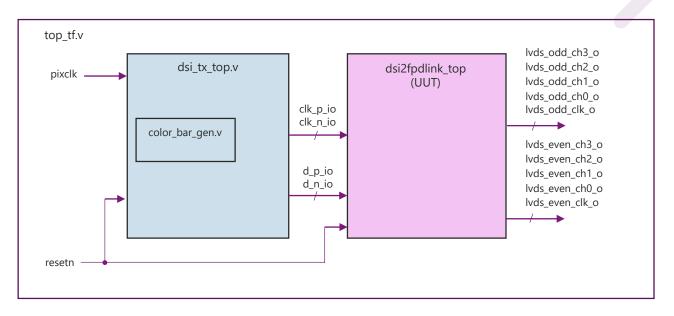

### テストベンチ構成概要図

テストベンチ上でMIPI DSIの送信モデルであるdsi\_tx\_top.vをインプリメントしています。このモジュールにはFull-HD(1080 60p), RGB888のカラーバーデータを 生成するcolor\_bar\_gen.vが組み込まれており、 dsi\_tx\_top.vからはFull-HD, RGB888のデータがMIPI DSI 4Laneで出力されます。 このMIPI DSI 4Laneのデータがシミュレーション対象のdsi rx top.vに入力され、LVDSデータが出力されることを確認しています。

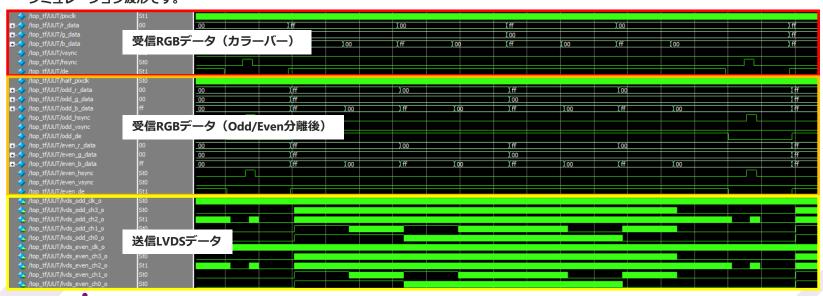

下図は送信モデルにて生成されたRGB888パラレルデータ(カラーバー)がMIPI D-PHYに変換され、本モジュールに入力されている箇所のシミュレーション波形です。

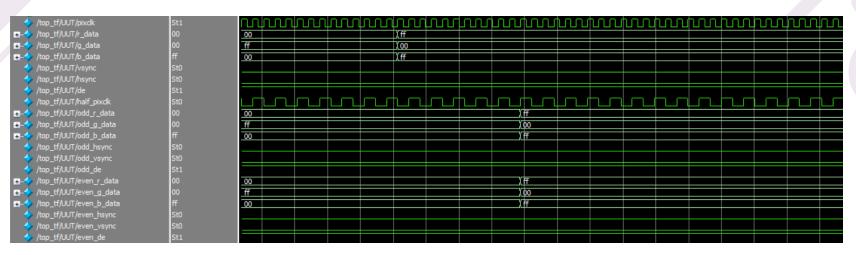

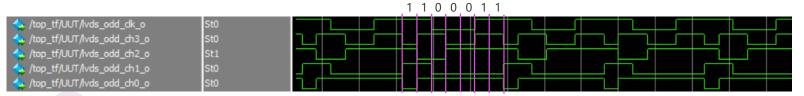

下図はD-PHYにて受信後、RGB888パラレルデータへと変換しその後Odd/Evenピクセルに分離して7:1LVDS送信モジュールにてOpenLDI形式で送信している部分の シミュレーション波形です。

Odd/Even分離後のピクセルデータはピクセルクロック周波数が元の半分になっています。

送信LVDSはFPD-Link (OpenLDI形式) のため、クロックは1Laneあたりのデータ7bit周期に対し、"1100011"の4:3デューティで送信されます。

Confidential

2022/12/9

# **Revision History**

| Date       | Revision | Page | Change Information |

|------------|----------|------|--------------------|

| 2022/12/01 | 1.0      |      | First Revision     |

|            |          |      |                    |

|            |          |      |                    |

|            |          |      |                    |

© Macnica, Inc.