# Nexusシリーズユーザーガイド

### はじめに

- 本資料は、Lattice社 NexusシリーズFPGA の設計時の注意事項をまとめています。

- NexusシリーズFPGAは以下のファミリーを指します。

- CrossLink-NXファミリー

- Certus-NXファミリー

- CertusPro-NXファミリー

- XO5-NXファミリー

- 最終確認として、各Hardware Checklist をご確認ください。

- 実際の動作等の詳細や最終確認は別途データシート、テクニカルノートをご参照ください。

- Lattice 社ドキュメントと本資料との間に差異があった場合、Lattice 社ドキュメントを正とします。

- NX共通のユーザーガイドのため、4ファミリー共通のパラメータについては、出典の名称のみ記載し、バージョン情報はそれぞれ異なるために割愛しています。

### 目次

#### 1. 電源ピン関連

- 1.1 電源ピンの説明

- 1.2 電源ランプレート

- 1.3 電源シーケンス

- 1.4 電源Power-On-Reset

#### 2. sysl/Oピン関連

- 2.1 sysl/Oピンの概要

- 2.2 PCLK/GPLL ピン

- 2.3 内部 Pull up/down の抵抗値

- 2.4 電源起動時のI/O の挙動に関して

#### 3. sysI/O BANK 関連

- 3.1 sysI/O BANK 関連

- 3.1.1 Certus-NX BANK 構成

- 3.1.2 CertusPro-NX BANK 構成

- 3.1.3 CrossLink-NX BANK 構成

- 3.1.4 Mach XO5-NX BANK 構成

- 3.2 BANK 毎のI/O Standard

- 3.3 Mixed Voltage Mode

2025/7/3

### 目次

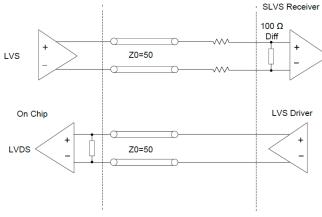

- 4. 差動信号関連

- 4.1 差動信号関連

- 4.2 LVDS の注意事項

- 4.2.1 LVDS

- 4.2.2 LVDS25E (Output Only) の注意事項

- 4.2.3 SubLVDS (Input Only) の注意事項

- 4.2.4 SubLVDSE/SubLVDSEH (Output Only) の注意事項

- 4.2.5 SLVS の注意事項

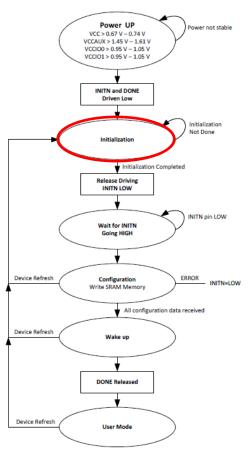

- 5. コンフィギュレーション関連

- 5.1 コンフィギュレーション

- 5.2 コンフィギュレーションモード概要

- 5.3 コンフィギュレーション注意事項

- 5.4 コンフィギュレーションモード選択方法

- 5.5 各コンフィギュレーションモードにおける使用ピン

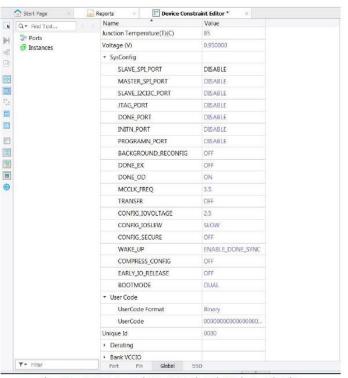

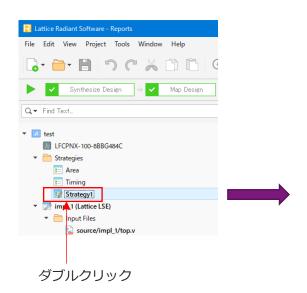

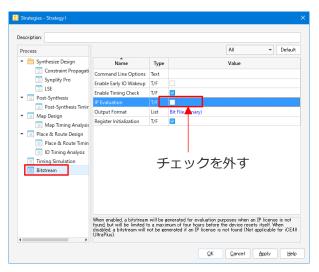

- 5.6 開発ツール上の設定

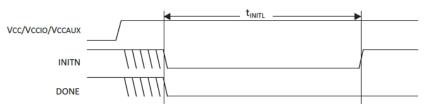

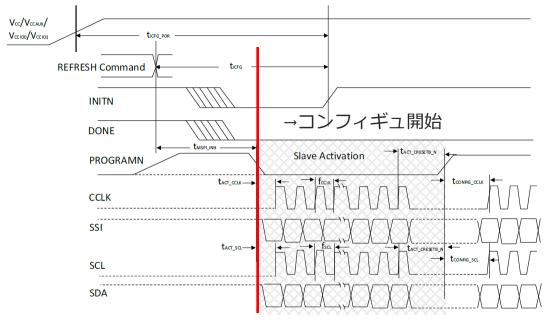

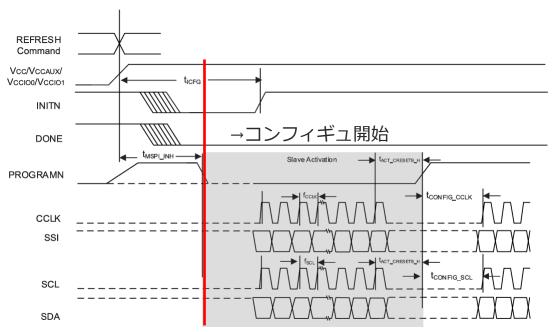

- 5.7 コンフィギュレーションフロー

- 5.8 コンフィギュレーション関連ピン波形

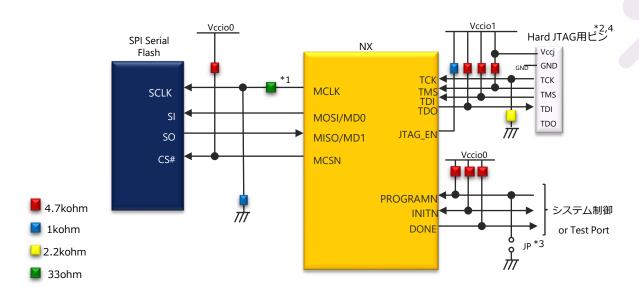

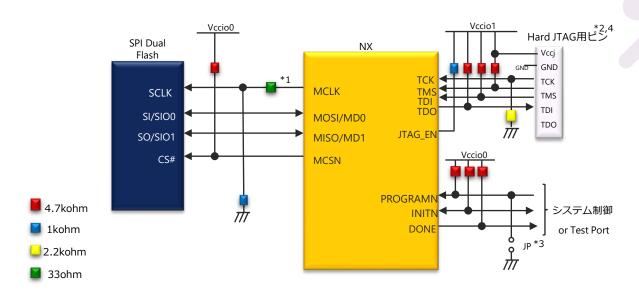

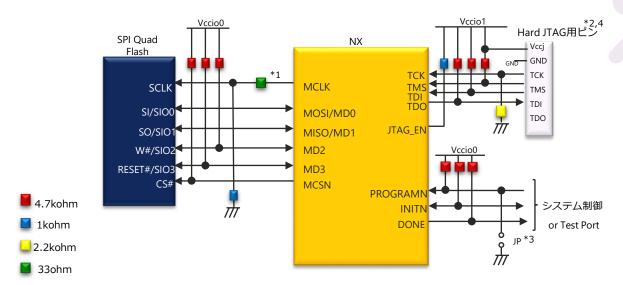

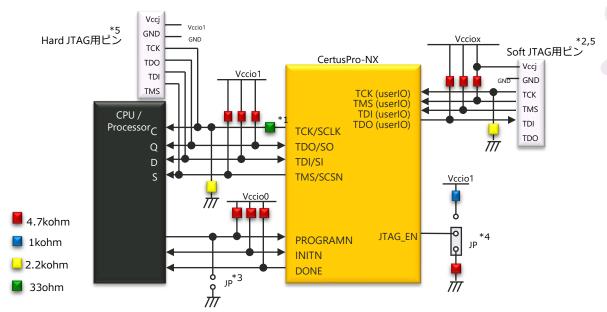

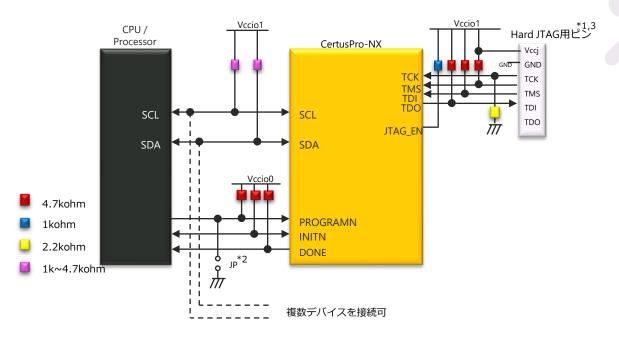

- 5.9 回路例

- 5.10 コンフィギュレーションデータサイズ

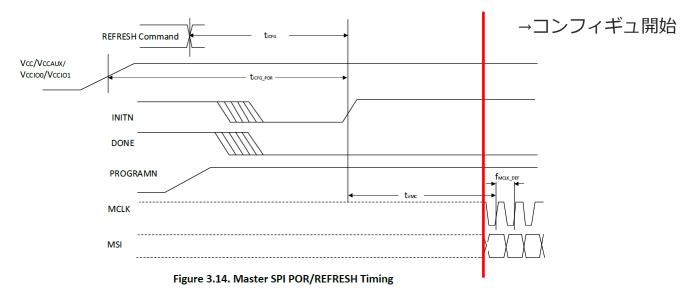

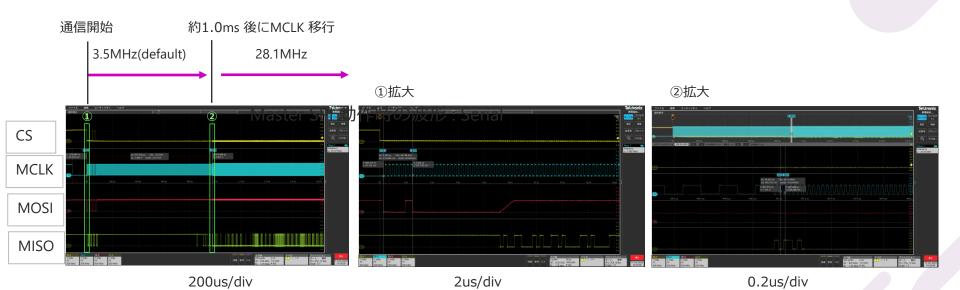

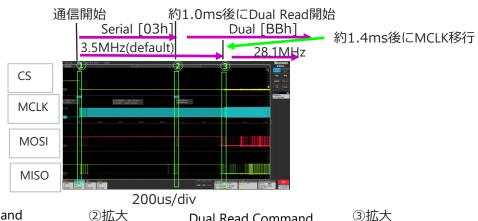

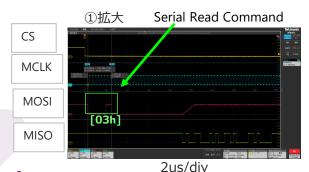

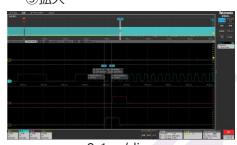

- 5.11 Master SPI 動作時の波形

### 目次

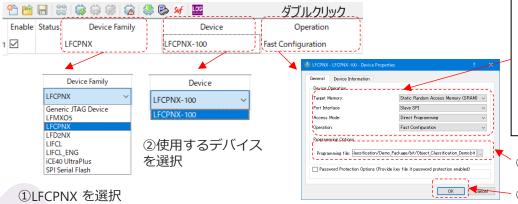

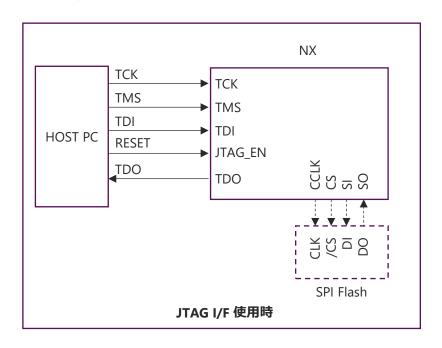

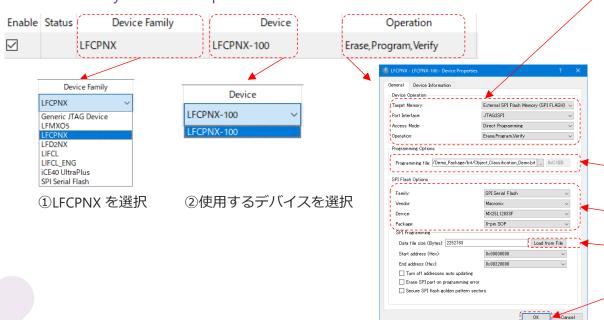

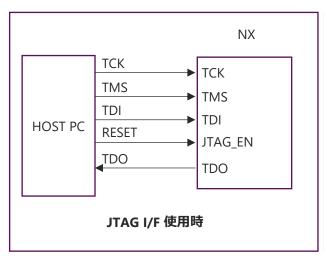

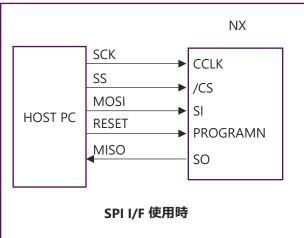

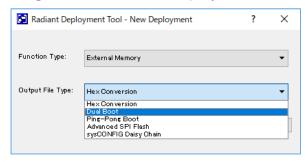

#### 6. Radiant Programmer を用いた書き込み

- 6.1 Download ケーブル

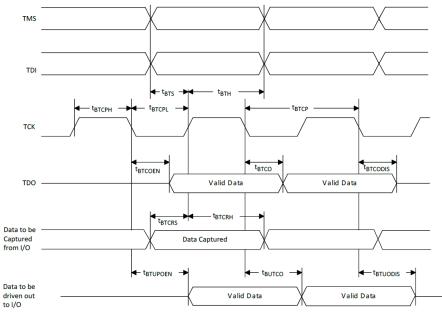

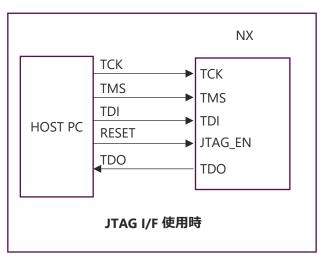

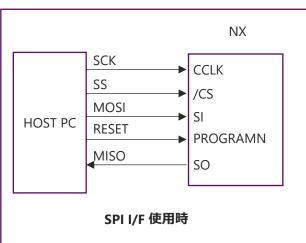

- 6.2 Download ケーブル信号説明

- 6.3 Programmer を用いた書き込みに関しての資料

- 6.4 SRAM 領域への書込み

- 6.5 FPGA 経由でのSPI Flash への書込み

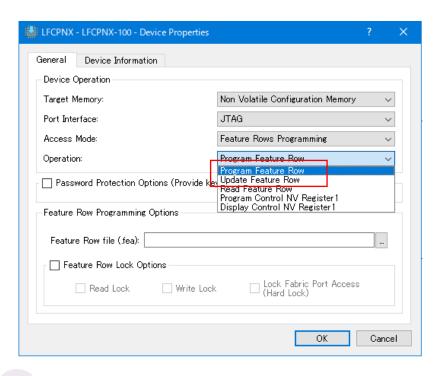

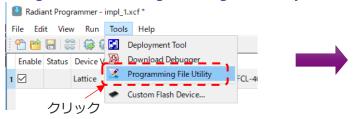

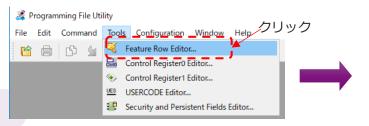

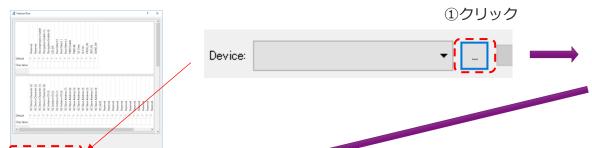

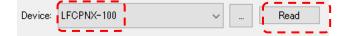

- 6.6 Feature Row への書込み

- 6.7 Program Feature Row での書き込み

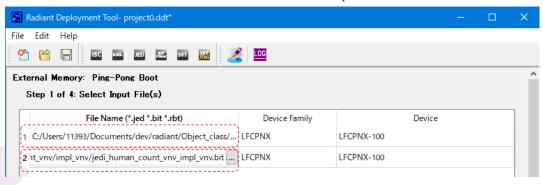

- 6.8 サポートしている特殊Boot Mode

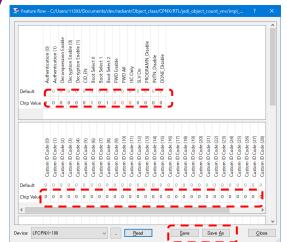

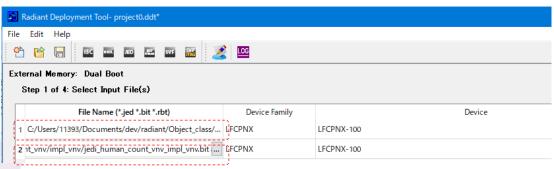

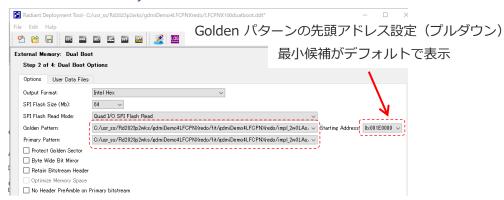

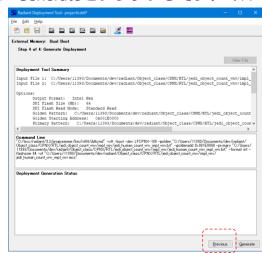

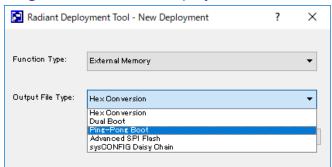

- 6.9 Dual Boot

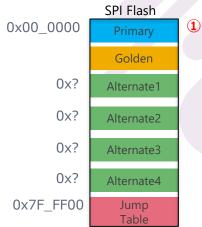

- 6.10 Multi Boot

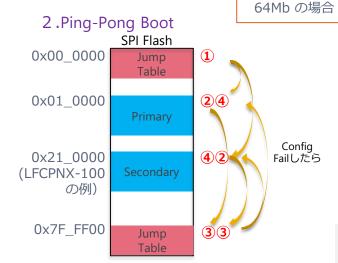

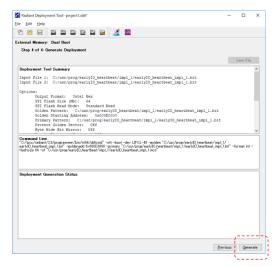

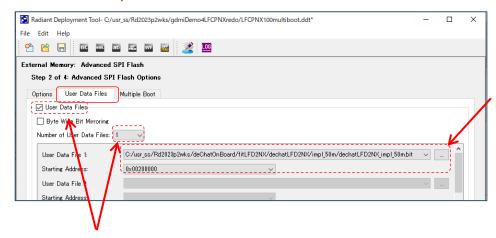

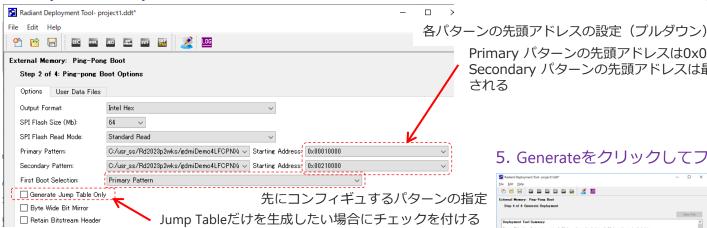

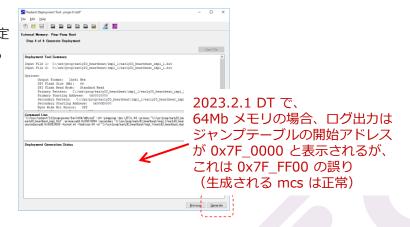

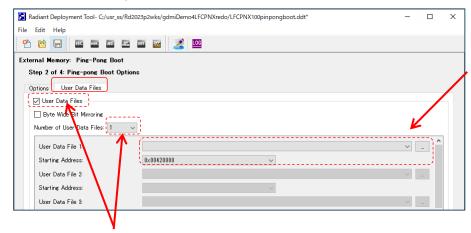

- 6.11 Ping-Pong Boot

#### 7. SerDes/PCS 関連

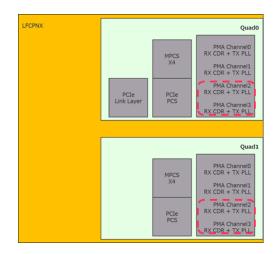

- 7.1 SerDes/PCS の概要

- 7.2 SerDes/PCS の対応プロトコル

- 7.3 SerDes/PCS の電源設計に関して

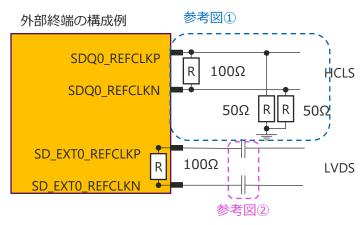

- 7.4 SerDes/PCS の基準クロック入力について

- 7.5 SerDes/PCS の外部入力基準クロック仕様

- 7.6 SerDes/PCS のレシーバー入力仕様

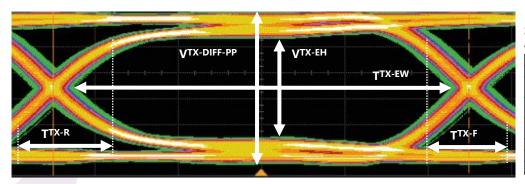

- 7.7 SerDes/PCS のトランスミッター出力仕様

- 7.8 10GBASE-R

# 1. 電源ピン関連

© Macnica, Inc.

## 1.1 電源ピンの説明(Certus-NX,CertusPro-NX/CrossLink-NX/MachXO5-NX,MachXO5T-NX)

本項は、Lattice 社の以下の資料より抜粋した情報です。 なお、Lattice 社の英文資料の情報を正とします。

DC and Switching Characteristics for Commercial and Industrial より抜粋

Certus-NX

Certus-NX Family Data Sheet FPGA-DS-02078-1.9 January 2024

CertusPro-NX

CertusPro-NX Family Data Sheet FPGA-DS-02086-1.8 February 2024

CrossLink-NX

CrossLink-NX Family Data Sheet FPGA-DS-02049-2.0 October 2023

MachXO5-NX

MachXO5-NX Family Data Sheet FPGA-DS-02102-1.5 October 2023

## 1.1 電源ピンの説明(Certus-NX,CertusPro-NX/CrossLink-NX/MachXO5-NX,MachXO5T-NX)

|                                       | Min    | Тур. | Max    | Unit | Certus-NX               | CertusPro-NX          | CrossLink-NX          | MachXO5-NX,<br>MachXO5T-NX                     |

|---------------------------------------|--------|------|--------|------|-------------------------|-----------------------|-----------------------|------------------------------------------------|

| V <sub>CC</sub> , V <sub>CCECLK</sub> | 0.95   | 1.00 | 1.05   | V    | コア電源                    | ,                     | •                     |                                                |

|                                       | 1.71   | 1.80 | 1.89   | V    | -                       | Bank0,1,2,6,7に対する補助電源 | -                     | -                                              |

| Vccaux                                | 1.746  | 1.80 | 1.89   | V    | Bank0,1,2,6,7に対する補助電源   | -                     | Bank0,1,2,6,7に対する補助電源 | Bank0,1,2,3,4,7,8,9に対する補助<br>電源                |

| VCCAUXH3/4/5                          | 1.71   | 1.80 | 1.89   | V    | -                       | Bank3,4,5に対する補助電源     | -                     | -                                              |

|                                       | 1.746  | 1.80 | 1.89   | V    | Bank3,4,5に対する補助電源       | -                     | Bank3,4,5に対する補助電源     | -                                              |

| VCCAUXH5/6                            | 1.746  | 1.80 | 1.89   |      | -                       | -                     | -                     | Bank5,6,に対する補助電源                               |

|                                       | 1.71   | 1.80 | 1.89   | V    | -                       | コアロジック用補助電源電圧         | -                     | -                                              |

| Vccauxa                               | 1.746  | 1.80 | 1.89   | V    | コアロジック用補助電源電圧           | -                     | コアロジック用補助電源電圧         | コアロジック用補助電源電圧                                  |

| VCCA_D-PHY                            | 1.71   | 1.80 | 1.89   | V    | -                       | -                     | MIPI D-PHYアナログ電源      | -                                              |

| Vcc_d-phy                             | 0.95   | 1.00 | 1.05   | V    | -                       | -                     | MIPI D-PHYデジタル電源      | -                                              |

| VCCPLL_D-PHY                          | 0.95   | 1.00 | 1.05   | V    | -                       | -                     | MIPI D-PHY PLL電源      | -                                              |

|                                       | 3.135  | 3.30 | 3.465  | V    | Bank2,6,7               | Bank2,6,7             | Bank0,1,2,6,7         | Bank0,1,2,3,4,7,8,9,Bank 1<br>は VCCIO 3.3 Vのみ可 |

|                                       | 2.375  | 2.50 | 2.625  | V    | Bank2,6,7               | Bank2,6,7             | Bank0,1,2,6,7         | Bank0,2,3,4,7,8,9                              |

|                                       | 1.71   | 1.80 | 1.89   | V    | All Banks               | All Banks             | All Banks             | All Banks except Bank 1                        |

| Vccio                                 | 1.425  | 1.50 | 1.575  | V    | All Banks               | All Banks             | All Banks             | All Banks except Bank 1                        |

|                                       | 1.2825 | 1.35 | 1.4175 | V    | VCCIO=1.35V(For DDR3L O | nly)                  | -                     | · · · · · · · · · · · · · · · · · · ·          |

|                                       | 1.14   | 1.20 | 1.26   | V    | All Banks               | All Banks             | All Banks             | All Banks except Bank 1                        |

|                                       | 0.95   | 1.00 | 1.05   | V    | Bank3,4,5               | Bank3,4,5             | Bank3,4,5             | Bank5,6                                        |

Data Sheet DC and Switching Characteristics for Commercial and Industrial より抜粋

# 1.1 電源ピンの説明(Certus-NX,CertusPro-NX/CrossLink-NX/MachXO5-NX,MachXO5T-NX)

|                 | Min  | Тур. | Max  | Unit | Certus-NX,CertusPro-NX | CrossLink-NX | MachXO5-NX,MachXO5T-NX |

|-----------------|------|------|------|------|------------------------|--------------|------------------------|

| ADC部            |      |      |      |      |                        |              |                        |

| VCCADC18        | 1.71 | 1.80 | 1.89 | V    | ADC用電源                 |              |                        |

| SerDes部         |      |      |      |      |                        |              |                        |

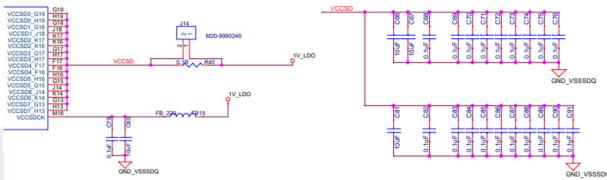

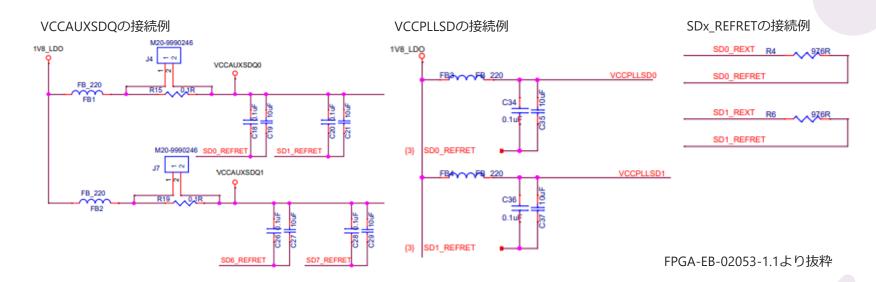

| Vccsd           | 0.95 | 1.00 | 1.05 | V    | SerDesブロック, I/O供給電源    |              |                        |

| <b>V</b> CCSDCK | 0.95 | 1.00 | 1.05 | V    | SerDesクロックバッファ供給電源     |              |                        |

| Vccpllsd        | 1.71 | 1.80 | 1.89 | V    | SerDesブロックPLL供給電源      |              |                        |

| Vccauxsdq       | 1.71 | 1.80 | 1.89 | V    | SerDesブロック補助電源         |              |                        |

- 1. 正しく動作させるためには、すべての電源が有効な動作電圧範囲に保持されていなければならない。

- 2. 同じ電圧の電源はすべて同じ電圧源から供給。適切な絶縁フィルターが必要。

- 3. SerDes を除き、共通電源レールは一緒に接続。

- 4. MSPI (Bank 0) と JTAG、SSPI、I2C、I3C (Bank 1) ポートは VCCIO =  $1.8 \text{ V} \sim 3.3 \text{ V}$  でサポート。

- 5. 10G SerDes を使用する場合、VCC 電圧は0.97V~1.05V の範囲内でなければならない。

Data Sheet DC and Switching Characteristics for Commercial and Industrial より抜粋

### 1.2 電源ランプレート

#### ■電源ランプレート

各電源ピンへの電圧供給は以下のランプレートを守らなければならない。

• 0.1V/ms~50V/ms

Power Supply Ramp Rates より抜粋

Certus-NX

Certus-NX Family Data Sheet FPGA-DS-02078-1.9 January 2024

CertusPro-NX

CertusPro-NX Family Data Sheet FPGA-DS-02086-1.8 February 2024

CrossLink-NX

CrossLink-NX Family Data Sheet FPGA-DS-02049-2.0 October 2023

MachXO5-NX

MachXO5-NX Family Data Sheet FPGA-DS-02102-1.5 October 2023

## 1.2 電源ランプレート

■電源ランプレート

仕様を基に立ち上げ時間の参考値を算出すると以下のようになる。

計算式 Max Vcc/0.1(V/ms): 例 1.0(V) / 0.1(V/ms) = 10ms

Min Vcc/50(V/ms):例 1.0(V) / 50(V/ms) = 0.02ms

| 電源種類               | 電圧(Typ) | Certus-NX,CertusPro-NX/CrossLink-NX/<br>MachXO5-NX,MachXO5T-NX<br>(ms) |     |  |

|--------------------|---------|------------------------------------------------------------------------|-----|--|

|                    |         | Min                                                                    | Max |  |

| Vcc                | 1.0V    | 0.02                                                                   | 10  |  |

| V <sub>CCAUX</sub> | 1.8V    | 0.036                                                                  | 18  |  |

| V <sub>CCIO</sub>  | 1.0V    | 0.02                                                                   | 10  |  |

|                    | 1.2V    | 0.024                                                                  | 12  |  |

|                    | 1.8V    | 0.036                                                                  | 18  |  |

|                    | 2.5V    | 0.05                                                                   | 25  |  |

|                    | 3.3V    | 0.066                                                                  | 33  |  |

### 1.3 電源シーケンス

#### ■電源シーケンス

本デバイスに電源に関するシーケンスの規定は基本的にはありません。

ただし POR 後デバイスが起動すると、IO の出力電圧はそのバンクの  $V_{CCIO}$  に依存するため、不定電圧の出力を防止するために POR解除前に  $V_{CCIO}$  を立ち上げることを推奨。または、リセットICなどを使用して、十分な時間PORが掛かるようにする事を推奨。

Power up Sequence より抜粋

Certus-NX

Certus-NX Family Data Sheet FPGA-DS-02078-1.9 January 2024

CertusPro-NX

CertusPro-NX Family Data Sheet FPGA-DS-02086-1.8 February 2024

CrossLink-NX

CrossLink-NX Family Data Sheet FPGA-DS-02049-2.0 October 2023

MachXO5-NX

MachXO5-NX Family Data Sheet FPGA-DS-02102-1.5 October 2023

**MACNICA**

### 1.4 電源Power-On-Reset

■本項は、Lattice 社の以下の資料より抜粋した情報です。 なお、Lattice 社の英文資料の情報を正とします。

Power-On Reset より抜粋

Certus-NX

Certus-NX Family Data Sheet FPGA-DS-02078-1.9 January 2024

CertusPro-NX

CertusPro-NX Family Data Sheet FPGA-DS-02086-1.8 February 2024

CrossLink-NX

CrossLink-NX Family Data Sheet FPGA-DS-02049-2.0 October 2023

MachXO5-NX

MachXO5-NX Family Data Sheet FPGA-DS-02102-1.5 October 2023

### 1.4 電源Power-On-Reset

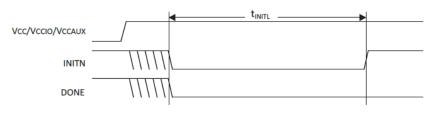

#### ■ 電源立ち上がり時のPOR トリップポイント。

- Vcc  $0.73V \sim 0.83V$

- $V_{CCAUX}$  1.34V  $\sim$  1.71V (Certus-NX, CrossLink-NX)

- $\cdot$  V<sub>CCAUX</sub> 1.34V  $\sim$  1.62V (CertusPro-NX, Mach XO5-NX, Mach XO5T-NX )

- $\cdot$  V<sub>CCIO0/1</sub> 0.89V  $\sim$  1.05V

POR がかかるとリセット状態になる。

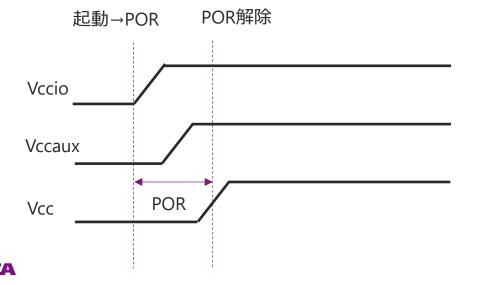

例として上げると下図のようになる。

例

#### 注意)

Vccioの電源立ち上げシーケンスを最後にした場合、0.89V ~ 1.05V でパワーオンリセットが解除され、不定出力となる。 外部のリセットICでコントロールするか、シーケンス設計を綿密に確認することを推奨。

### 1.4 電源Power-On-Reset

- 電源立ち下がり時のPOR トリップポイント。

- $\cdot$  Vcc 0.51V  $\sim 0.81$ V

- ・VCCAUX 1.38V  $\sim 1.54$ V,または 1.59V

# 2. sysI/Oピン関連

## 2.1 sysl/Oピンの概要 1/8

■本項は、Lattice 社の以下の資料より抜粋した情報です。 なお、Lattice 社の英文資料の情報を正とします。

Pinout Information より抜粋

| Certus-N> | ( |

|-----------|---|

|-----------|---|

Certus-NX Family Data Sheet FPGA-DS-02078-1.9 January 2024

CertusPro-NX

CertusPro-NX Family Data Sheet FPGA-DS-02086-1.8 February 2024

CrossLink-NX

CrossLink-NX Family Data Sheet FPGA-DS-02049-2.0 October 2023

MachXO5-NX

MachXO5-NX Family Data Sheet FPGA-DS-02102-1.5 October 2023

# 2.1 sysl/Oピンの概要 2/8

以下は専用ピンです。外部処理は設計ツール(Lattice Radiant)に従って処理が必要。

| ピン名                  | 入出力 | 説明                                                                                        | 外部処理                                                                           |

|----------------------|-----|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Dedicated ピン         |     |                                                                                           |                                                                                |

| JTAG_EN              | ı   | JTAG ピンをコントロールするピン。<br>JTAG ピンは Low の場合は GPIO に、Highの場合は JTAG 専用ピン。                       | 4.7kΩ pull-down to GND(Disable時) 1.0kΩ pull-up to $V_{\text{CCIO1}}$ (Enable時) |

| ADC_REFA, ADC_REFB   | I   | ADC の基準電圧を入力。                                                                             | 未使用時は Open                                                                     |

| ADC_DP/NA, ADC_DP/NB | I   | ADC への入力専用ピン。                                                                             | 未使用時は Open                                                                     |

| SDx_RXDP/N           | I   | SerDes 用の入力ピン。                                                                            | 未使用時は Open                                                                     |

| SDx_TXDP/N           | 0   | SerDes 用の出力ピン。                                                                            | 未使用時は Open                                                                     |

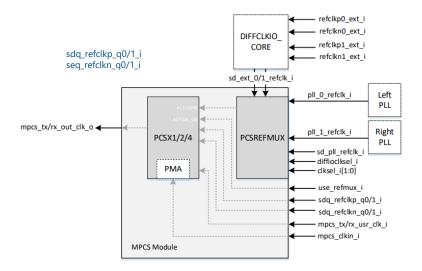

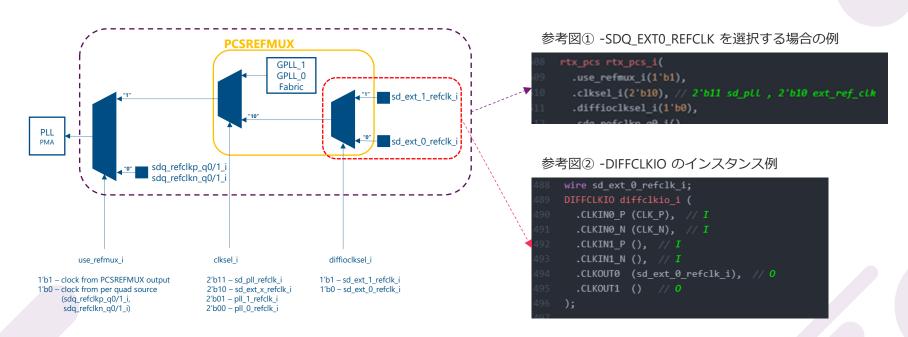

| SDQy_REFCLKP/N       | I   | Quad yの SerDes リファレンスクロック入力ピン。                                                            | 未使用時は Open                                                                     |

| SD_EXTy_REFCLKP/N    | I   | SerDes 用の外部リファレンスクロック入力ピン。                                                                | 未使用時は Open                                                                     |

| SDx_REXT             | I   | SerDes 用リファレンス抵抗入力ピン。このピンと SDx_REFRET の間に抵抗を接続。<br>外部抵抗値に基づいて、オンチップ差動終端インピーダンスを調整するために使用。 | 未使用時は Open                                                                     |

| SDx_REFRET           | I   | SerDes 用リファレンスリターン入力ピン。このピンと SDx_REXT の間に抵抗を接続。<br>V <sub>CCPLLSDx</sub> に AC 結合。         | 未使用時は Open                                                                     |

| D-PHY[0-1]_CKP/N     | I/O | MIPI D-PHY クロック入出カペア (2つのD-PHYブロック毎)。                                                     | 未使用時は Open                                                                     |

| D-PHY[0-1]_DP/N[0-3] | I/O | ハードMIPI D-PHY データ入出力ペア。<br>2つのハードMIPI D-PHY ブロックの4つの高速レーン毎。                               | 未使用時は Open                                                                     |

# 2.1 sysl/Oピンの概要 3/8

| ピン名                             | ピン名 入出力 説明 |                                                                                                                                                            | 外部処理 |

|---------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| その他のピン                          |            |                                                                                                                                                            |      |

| NC                              |            | 未接続ピン。何も接続しない。                                                                                                                                             |      |

| RESERVED                        |            | 予約ピン。RESERVED には何も接続しない。                                                                                                                                   |      |

| 汎用ピン                            | •          |                                                                                                                                                            |      |

| P[T/B/L/R][Number] _ [A/B]<br>例 | I/O        | USER IO ピン。T は Top、B は Bottom、L は Left、R は Right の Bank を示す。<br>A/B は差動のペアを示し、Number は A/B ペアを識別。<br>Bottom Bank(Bank3, 4, 5) の A/B ペアは True LVDS の入出力に対応。 |      |

| PRxxx, PTxxx, PBxxx, PLxxx など   |            | True LVDS 使用の場合、100Ωの差動終端抵抗が選択可能。<br>それ以外の Bank では Emulated LVDS は A/B ペアで出力のみサポート可能。                                                                      |      |

Datasheet Signal Descriptions より抜粋

2025/7/3

# 2.1 sysl/Oピンの概要 4/8

| ピン名                     | 入出力 | 説明                                                                                                       | 外部処理                                                                               |

|-------------------------|-----|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Shared Configuration ピン |     |                                                                                                          |                                                                                    |

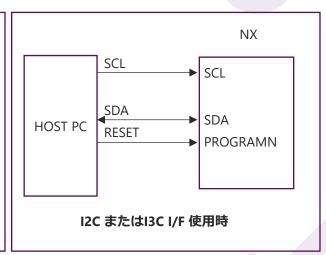

| PRxxx/SDA/USER_SDA      | I/O | PRxxx:GPIO として使用。<br>SDA:コンフィギュレーションを  2C/ 3C 経由で行う場合の SDA として使用。<br>USER_SDA: 2C/ 3C  F 使用時の SDA として使用。 | SDA:1.0kΩ to 4.7kΩ pull-up to V <sub>CCIO1</sub><br>※Slave I3C コンフィギュ時はプルアップ抵抗不要   |

| PRxxx/SCL/USER_SCL      | I/O | PRxxx:GPIOとして使用。<br>SDA:コンフィギュレーションを  2C/ 3C 経由で行う場合の SCL として使用。<br>USER_SDA: 2C/ 3C  F 使用時の SCL として使用。  | SCL:1.0kΩ to 4.7kΩ pull-up to V <sub>CClO1</sub><br>※Slave I3C コンフィギュ時はプルアップ抵抗不要   |

| PRxxx/TDO/SSO           | I/O | PRxxx:GPIO として使用。<br>TDO:JTAG_EN=1 の時、JTAG ピンとして使用。<br>SSO:Slave SPI モード時の出力ピンとして使用。                     | TDO: 4.7kΩ pull-up to V <sub>CCIO1</sub>                                           |

| PRxxx/TDI/SSI           | I/O | PRxxx:GPIO として使用。<br>TDI:JTAG_EN=1 の時、JTAG ピンとして使用。<br>SSI:Slave SPI モード時の入力ピンとして使用。                     | TDI:4.7kΩ pull-up to V <sub>CClO1</sub><br>pull-up は出力IC端にて行う                      |

| PRxxx/TMS/SCSN          | I/O | PRxxx:GPIO として使用。<br>TMS:JTAG_EN=1 の時、JTAG ピンとして使用。<br>SCSN:Slave SPIモード時のチップセレクトピンとして使用。                | TMS: $4.7k\Omega$ pull-up to $V_{CCIO1}$ SCSN: $4.7k\Omega$ pull-up to $V_{CCIO1}$ |

| PRxxx/TCK/SCLK          | I/O | PRxxx:GPIO として使用。<br>TCK:JTAG_EN=1 の時、JTAG ピンとして使用。<br>SCLK:Slave SPI モード時のクロック入力ピンとして使用。                | TCK: $2.2k\Omega$ pull-down to GND SCLK: $2.2k\Omega$ pull-down to GND             |

Datasheet Signal Descriptions より抜粋

© Macnica, Inc.

# 2.1 sysl/Oピンの概要 5/8

| ピン名                     | 入出力 | 説明                                                                                         | 外部処理                                          |

|-------------------------|-----|--------------------------------------------------------------------------------------------|-----------------------------------------------|

| Shared Configuration ピン | •   |                                                                                            |                                               |

| PTxxx/MCSNO             | I/O | PTxxx:GPIO として使用。<br>MCSNO:Master SPI モード時のチップセレクトとして使用。Daisy Chain構成時に使用。                 |                                               |

| PTxxx/MD3               | I/O | PTxxx: GPIO として使用。<br>MD3: Master SPI モードの Quad を使用する際に使用。                                 |                                               |

| PTxxx/MD2               | I/O | PTxxx :GPIO として使用。<br>MD2:Master SPI モードの Quad を使用する際に使用。                                  |                                               |

| PTxxx/MSI/MD1           | I/O | PTxxx:GPIO として使用。<br>MSI:Master SPI モード時の入力として使用。<br>MD1:Master SPI モードの Quad を使用する際に使用。   |                                               |

| PTxxx/MSO/MD0           | I/O | PTxxx:GPIO として使用。<br>MSO: Master SPI モード時の出力として使用。<br>MDO: Master SPI モードの Quad を使用する際に使用。 |                                               |

| PTxxx/MCSN/PCLKT0_1     | I/O | PTxxx:GPIO として使用。<br>MCSN: Master SPI モード時のチップセレクトとして使用。<br>PCLKTO_1:クロック入カピンとして使用。        | MCSN: 4.7kΩ pull-up to V <sub>CCIO0</sub>     |

| PTxxx/MCLK/PCLKT0_0     | I/O | PTxxx: GPIO として使用。<br>MCLK: Master SPI モード時のクロックピンとして使用。<br>PCLKTO_0: クロック入カピンとして使用。       | MCLK: 1.0kΩ pull-down to GND                  |

| PTxxx/PROGRAMN          | I/O | PTxxx:GPIOとして使用。<br>PROGRAMN:入力ピン。任意のタイミングでコンフィギュレーションを開始させるピン。<br>※1                      | PROGRAMN: 4.7kΩ pull-up to V <sub>CCIO0</sub> |

| PTxxx/INITN             | I/O | PTxxx:GPIOとして使用。<br>INITN:双方向オープンドレインピン。コンフィギュレーション可能な状態を示す。※1                             | INITN: $4.7k\Omega$ pull-up to $V_{CCIO0}$    |

| PTxxx/DONE              | I/O | PTxxx:GPIOとして使用。<br>DONE:双方向オープンドレインピン。コンフィギュレーションの完了を示す。※1                                | DONE: 4.7kΩ pull-up to V <sub>CCIO0</sub>     |

<sup>※1</sup> 詳細は「2.1.4. 電源起動時の I/O の挙動に関して」を参照。

**MACNICA**

コンフィギュ関連ピンは専用ピンとして使用することを強く推奨。MCLKを汎用ピンとして使用する場合、ワイヤードOR接続を推奨。

# 2.1 sysl/Oピンの概要 6/8

| ピン名                          | 入出力 | 説明                                                                                                                                       | 外部処理 |

|------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------|------|

| Shared CLOCK Pins            | '   |                                                                                                                                          |      |

| PBxxx/PCLK[T,C][3,4,5]_[0-3] | I/O | PBxxx: GPIO として使用。<br>PCLK: Primary Clock パスにつながる入力ピン。<br>T(True)、C(Complement)は差動の P/N で、シングルエンド入力で使用する<br>場合には T 側を使用。                 |      |

| PTxxx/PCLKT0_[0-1]           | I/O | PTxxx: GPIO として使用。<br>PCLK: シングルエンドのみ使用可能な Primary Clock パスに繋がる入力ピン。                                                                     |      |

| PRxxx/PCLKT[1,2]_[0-2]       | I/O | PRxxx: GPIO として使用。<br>PCLK: シングルエンドのみ使用可能な Primary Clock パスに繋がる入力ピン。                                                                     |      |

| PLxxx/PCLKT[6,7]_[0,2]       | I/O | PLxxx: GPIO として使用。<br>PCLK: シングルエンドのみ使用可能な Primary Clock パスに繋がる入力ピン。                                                                     |      |

| PBxxx/LRC_GPLL[T,C]_IN       | I/O | PBxxx: GPIO として使用。<br>LRC_GPLL: Lower Right Bank の PLL への CLK 入力ピン。<br>T(True)、C(Complement)は差動の P/N で、シングルエンド入力で<br>使用する場合には T 側を使用します。 |      |

| PBxxx/LLC_GPLL[T,C]_IN       | I/O | PLxxx: GPIO として使用。<br>ULC_GPLL: Lower Left Bank の PLL への CLK 入力ピン。<br>T(True)、C(Complement)は差動の P/N で、シングルエンド入力で<br>使用する場合には T 側を使用。     |      |

| PLxxx/ULC_GPLLT_IN           | I/O | PLxxx: GPIO として使用。<br>ULC_GPLL: Upper Left Bank の PLL へのシングルエンド CLK 入力ピン。                                                                |      |

| PRxxx/URC_GPLLT_IN           | I/O | PRxxx: GPIO として使用。<br>URC_GPLLT: Upper Right BankのPLLへのシングルエンド入力ピン。                                                                      |      |

# 2.1 sysl/Oピンの概要 7/8

| ピン名                           | 入出力 | 説明                                                                                                                  | 外部処理                                                        |

|-------------------------------|-----|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Shared JTAG Pins              |     |                                                                                                                     |                                                             |

| PRxxx/TDO/ yyyy               | I/O | PRxxx: GPIO<br>TDO: JTAG_EN = 1 の時、JTAG yyyy の TDO 信号として使用。                                                         | TDO: 4.7kΩ pull-up to V <sub>CCIO0</sub>                    |

| PRxxx/TDI/yyyy                | I/O | PRxxx: GPIO<br>TDI: JTAG EN = 1の時、JTAG yyyyのTDI 信号として使用。                                                            | TDI: 4.7kΩ pull-up to V <sub>CCIOO</sub> pull-up は出力IC端にて行う |

| PRxxx/TMS/ yyyy               | I/O | PRxxx: GPIO<br>TMS: JTAG_EN = 1の時、JTAG yyyyのTMS 信号として使用。                                                            | TMS: $4.7k\Omega$ pull-up to $V_{CCIO0}$                    |

| PRxxx/TCK/ yyyy               | I/O | PRxxx: GPIO<br>TCK: JTAG_EN = 1の時、JTAG yyyyのTCK 信号として使用。                                                            | TCK: 2.2kΩ pull-down to VCCIO0                              |

| Shared VREF Pins              | •   |                                                                                                                     |                                                             |

| PBxxx/VREF[3,4,5]_[1-2]/yyyy  | I/O | PBxxx: GPIO<br>VREF: DDR メモリ機能の基準電圧。<br>[3,4,5] = Bank [1-2] 各Bank の VREF まで。<br>yyyy:その他の選択可能な特定機能ピン。              |                                                             |

| Shared Comparator Pins        | ·   |                                                                                                                     |                                                             |

| PBxxx/COMP[1-3][P,N]/yyyy     | I/O | PBxxx: GPIO<br>COMP: 差動コンパレータ入力。[P,N] = 正または負入力。<br>[1-3] = コンパレータ1~3への入力。<br>yyyy:その他の選択可能な特定機能ピン。                 |                                                             |

| Shared SGMII Pins             |     |                                                                                                                     |                                                             |

| PBxxx/SGMII_RX[P,N][0-1]/yyyy | I/O | PBxxx: GPIO<br>SGMII_RX:差動 SGMII RX 入力。[P,N] = 正または負入力。<br>[0-1] = SGMII RX0 または RX1 への入力。<br>yyyy:その他の選択可能な特定機能ピン。 |                                                             |

# 2.1 sysl/Oピンの概要 8/8

| ピン名                      | 入出力 | 説明                                                   | 外部処理 |

|--------------------------|-----|------------------------------------------------------|------|

| Shared User GPIO Pins    | ·   |                                                      |      |

| PBxxx/VREF[3,4,5]_[1_2]  | I/O | PBxxx: GPIO として使用。<br>VREF: DDR メモリ機能の基準電圧ピン。        |      |

| PBxxx/ADC_C[P,N]nn       | I/O | PBxxx: GPIO として使用。<br>ADC_C: ユーザー I/O と ADC 入力の兼用ピン。 |      |

| PBxxx/COMP[1-3][P,N]     | I/O | PBxxx: GPIO として使用。<br>COMP: 差動コンパレータ入力ピン。            |      |

| PBxxx/SGMII_RX[P,N][0-1] | I/O | PBxxx: GPIO として使用。<br>SGMII_RX: SGMII 入力ピン。          |      |

## 2.2 PCLK/GPLLピン

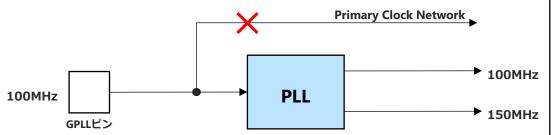

・クロック信号は必ずクロック入力ピン(PCLK) から入力。 GPIO からも入力が可能ですが、内部専用のクロックライン(Primary Clock) に載せるまでに遅延が発生(クロックピンから内部専用クロックラインまでのパスは最小遅延になる)。

・PLL への入力は GPLL ピンを使用することで PLL のクロック入力遅延を最小にできる。 ただし、以下のような PLL 入力を分岐して他の Primary Clock Network を使用し、FF に供給できない(設計 ツール上でエラーとなる)。

入力クロックの分岐ができないため、同じ周波数の クロックを使用する場合は同じ周波数のクロック出 力を用意する。

将来の拡張を考え、複数のGPLL(PCLK)ピンにクロックを配線しておく事を推奨。

・基板設計時、PLLを使用するかどうか判断に迷った場合、PLL専用ピン、クロックピン両方にクロック信号を供給しておくことを推奨(使わない方のピンはパターンが繋がっていても特に問題なし)。

引用: sysCLOCK PLL Design and Usage Guide for Nexus Platform 14.5. PLL Inputs and Outputs FPGA-TN-02095-2.3 September 2023

# 2.3 内部 Pull up/down の抵抗値 (1/7)

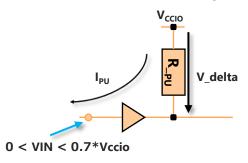

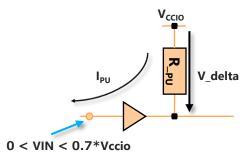

- ・外部 Pull up/down を設置する際、内部 Pull 設定と反対のレベルとなる場合は、Package Pin 上で中間電位となるのを防ぐために以下の内容に注意。

- ・内部 Pull up/down の抵抗値はそれぞれに流れるリーク電流と Vccio の推奨電圧範囲から算出可能。

| I <sub>PU</sub> | I/O Weak Pull-up Resistor<br>Current   | $0 \le V_{IN} \le 0.7 \times V_{CCIO}$     | -30 | 1 | -150 | μΑ |

|-----------------|----------------------------------------|--------------------------------------------|-----|---|------|----|

| I <sub>PD</sub> | I/O Weak Pull-down Resistor<br>Current | $V_{IL}$ (max) $\leq V_{IN} \leq V_{CCIO}$ | 30  | ı | 150  | μΑ |

引用: FPGA-DS-02086-1.7 3.8. DC Electrical Characteristics

# 2.3 内部 Pull up/down の抵抗値 (2/7)

- ・外部 Pull up/down を設置する際、内部 Pull 設定と反対のレベルとなる場合は、Package Pin 上で中間電 位となるのを防ぐために以下の内容に注意。

- ・内部 Pull up/down の抵抗値はそれぞれに流れるリーク電流と Vccio の推奨電圧範囲から算出可能。

#### 入力電圧レンジ

#### 3.11. sysI/O Single-Ended DC Electrical Characteristics

Table 3.14. sysI/O DC Electrical Characteristics – Wide Range I/O

| Input/Output          |         | V <sub>IL</sub> | VIII    | 1                  | V <sub>OL</sub> Max | V <sub>OH</sub> Min     | Ι /m Δ\                                    | I /m ()                                         |

|-----------------------|---------|-----------------|---------|--------------------|---------------------|-------------------------|--------------------------------------------|-------------------------------------------------|

| Standard <sup>2</sup> | Min (V) | Max (V)         | Min (V) | Max (V)            | (V)                 | (V) 101(III)            | I <sub>OL</sub> (mA)                       | I <sub>OH</sub> (mA)                            |

| LVTTL33<br>LVCMOS33   | _       | 0.8             | 2.0     | 3.465 <sup>4</sup> | 0.4                 | V <sub>CCIO</sub> – 0.4 | 2, 4, 8,<br>12, 16,<br>"50RS" <sup>3</sup> | -2, -4, -8,<br>-12, -16,<br>"50RS" <sup>3</sup> |

引用: FPGA-DS-02086-1.2 3.2. Recommended Operating Conditions

3.11. sysI/O Single-Ended DC Electrical Characteristics

## 2.3 内部 Pull up/down の抵抗値 (3/7)

・実際の計算例 LVCOMS33 の場合(Certus-NX, CertusPro-NX, CrossLink-NX)

内部 Pull-Up 抵抗 R\_PU は流れる電流 IPU と電圧降下V\_deltaを考慮して計算。

| Ipuが最大になるのはV_deltaが最大の時、即ちVIN=0Vのとき |                    |         |         |                   |  |  |  |  |

|-------------------------------------|--------------------|---------|---------|-------------------|--|--|--|--|

|                                     | VIN                | V_delta | Ipu(uA) | $R_{pu}(K\Omega)$ |  |  |  |  |

| LVCMOS33_max                        | 0                  | 3.465   | 150     | 23.1              |  |  |  |  |

| LVCMOS33_min                        | 0                  | 3.135   | 150     | 20.9              |  |  |  |  |

| lpuが最少になるのは                         | $VIN=0.7xV_{CCIC}$ | )       |         |                   |  |  |  |  |

|                                     | VIN                | V_delta | lpu(uA) | $R_{pu}(K\Omega)$ |  |  |  |  |

| LVCMOS33_max                        | 2.425              | 1.039   | 30      | 34.65             |  |  |  |  |

| LVCMOS33_min                        | 2.194              | 0.940   | 30      | 31.35             |  |  |  |  |

従って、LVCMOS33では内部Pull-Upが有効になっているとき、外部処理で論理レベルを反対のレベルにする場合、 R\_pu = 20.9K $\Omega$ とVIL(MAX) = 0.8Vを考慮すると 外部Pull Down=7.16K $\Omega$ 以下とする。

#### Recommended Operating Conditionより抜粋

| V <sub>CCIO</sub> = 3.3 V, Bank 0, Bank 1,<br>Bank 2, Bank 6, Bank 7 | 3.135 | 3.30 | 3.465 | V |  |

|----------------------------------------------------------------------|-------|------|-------|---|--|

|                                                                      |       |      |       |   |  |

#### sysI/O Single-Ended DC Electrical Characteristicsより抜粋

Table 3.14. sysI/O DC Electrical Characteristics – Wide Range I/O

| Input/Output          |         | V <sub>IL</sub> | VII     | 1       | V <sub>OL</sub> Max | V <sub>OH</sub> Min     | 1 ( 0)                                     | 1 /m 0)                                         |

|-----------------------|---------|-----------------|---------|---------|---------------------|-------------------------|--------------------------------------------|-------------------------------------------------|

| Standard <sup>2</sup> | Min (V) | Max (V)         | Min (V) | Max (V) | (V)                 | (V)                     | I <sub>OL</sub> (mA)                       | I <sub>OH</sub> (mA)                            |

| LVTTL33<br>LVCMOS33   | _       | 0.8             | 2.0     | 3.4654  | 0.4                 | V <sub>CCIO</sub> – 0.4 | 2, 4, 8,<br>12, 16,<br>"50RS" <sup>3</sup> | -2, -4, -8,<br>-12, -16,<br>"50RS" <sup>3</sup> |

| I <sub>PU</sub> | I/O Weak Pull-up Resistor<br>Current   | $0 \le V_{IN} \le 0.7 \times V_{CCIO}$ | -30 | _ | -150 | μА |

|-----------------|----------------------------------------|----------------------------------------|-----|---|------|----|

| I <sub>PD</sub> | I/O Weak Pull-down Resistor<br>Current | $V_{IL}(max) \le V_{IN} \le V_{CCIO}$  | 30  | _ | 150  | μА |

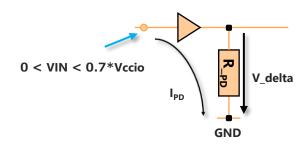

## 2.3 内部 Pull up/down の抵抗値 (4/7)

・実際の計算例 LVCOMS33 の場合(Certus-NX, CertusPro-NX, CrossLink-NX)

内部 Pull-Up 抵抗 R\_PD は流れる電流 IPD と電圧降下V\_deltaを考慮して計算。

| Ipdが最大になるのはV_deltaが最大の時、即ちVIN=V <sub>ccio</sub> のとき |            |         |         |                   |  |  |  |  |

|-----------------------------------------------------|------------|---------|---------|-------------------|--|--|--|--|

|                                                     | VIN        | V_delta | lpd(uA) | $R_{pd}(K\Omega)$ |  |  |  |  |

| LVCMOS33_max                                        | 3.465      | 3.465   | 150     | 23.1              |  |  |  |  |

| LVCMOS33_min                                        | 3.135      | 3.135   | 150     | 20.9              |  |  |  |  |

| Ipdが最少になるのはVIN=                                     | VIL(Max)の例 | 祭       |         |                   |  |  |  |  |

|                                                     | VIN        | V_delta | lpd(uA) | $R_{pd}(K\Omega)$ |  |  |  |  |

| LVCMOS33_max                                        | 0.8        | 2.665   | 30      | 26.666            |  |  |  |  |

| LVCMOS33_min                                        | 0.8        | 2.335   | 30      | 26.666            |  |  |  |  |

従って、LVCMOS33では内部Pull-Downが有効になっているとき、外部処理で論理レベルを反対のレベルにする場合、 R\_pd = 20.9K $\Omega$ と、VIH(MIN) = 2.0Vを考慮すると 外部Pull Up=11.86K $\Omega$ 以下とする。

#### Recommended Operating Conditionより抜粋

| V <sub>CCIO</sub> = 3.3 V, Bank 0, Bank 1,<br>Bank 2, Bank 6, Bank 7 | 3.135 | 3.30 | 3.465 | V |

|----------------------------------------------------------------------|-------|------|-------|---|

|                                                                      |       |      |       |   |

#### sysI/O Single-Ended DC Electrical Characteristicsより抜粋

Table 3.14. sysI/O DC Electrical Characteristics – Wide Range I/O

| Input/Output          |         | V <sub>IL</sub> | VIII    | ı                  | V <sub>OL</sub> Max | V <sub>OH</sub> Min     | 1 /m 1                                     | 1 (m 1)                                         |

|-----------------------|---------|-----------------|---------|--------------------|---------------------|-------------------------|--------------------------------------------|-------------------------------------------------|

| Standard <sup>2</sup> | Min (V) | Max (V)         | Min (V) | Max (V)            | (V)                 | (V)                     | I <sub>OL</sub> (mA)                       | I <sub>OH</sub> (mA)                            |

| LVTTL33<br>LVCMOS33   | _       | 0.8             | 2.0     | 3.465 <sup>4</sup> | 0.4                 | V <sub>CCIO</sub> – 0.4 | 2, 4, 8,<br>12, 16,<br>"50RS" <sup>3</sup> | -2, -4, -8,<br>-12, -16,<br>"50RS" <sup>3</sup> |

| I <sub>PU</sub> | I/O Weak Pull-up Resistor<br>Current   | $0 \le V_{IN} \le 0.7 \times V_{CCIO}$                      | -30 | _ | -150 | μА |

|-----------------|----------------------------------------|-------------------------------------------------------------|-----|---|------|----|

| I <sub>PD</sub> | I/O Weak Pull-down Resistor<br>Current | V <sub>IL</sub> (max) ≤ V <sub>IN</sub> ≤ V <sub>CCIO</sub> | 30  | _ | 150  | μА |

# 2.3 内部 Pull up/down の抵抗値 (5/7)

・実際の計算例 LVCOMS33 の場合(MachXO5-NX)

内部 Pull-Up 抵抗 R\_PU は流れる電流 IPU と電圧降下V\_deltaを考慮して計算。

| Ipuが最大になるのはV_deltaが最大の時、即ちVIN=0Vのとき |                    |         |         |                   |  |  |  |  |

|-------------------------------------|--------------------|---------|---------|-------------------|--|--|--|--|

|                                     | VIN                | V_delta | Ipu(uA) | $R_{pu}(K\Omega)$ |  |  |  |  |

| LVCMOS33_max                        | 0                  | 3.465   | 150     | 23.1              |  |  |  |  |

| LVCMOS33_min                        | 0                  | 3.135   | 150     | 20.9              |  |  |  |  |

| lpuが最少になるのは                         | $VIN=0.7xV_{CCIC}$ | )       |         |                   |  |  |  |  |

|                                     | VIN                | V_delta | lpu(uA) | $R_{pu}(K\Omega)$ |  |  |  |  |

| LVCMOS33_max                        | 2.425              | 1.039   | 30      | 34.65             |  |  |  |  |

| LVCMOS33_min                        | 2.194              | 0.940   | 30      | 31.35             |  |  |  |  |

従って、LVCMOS33では内部Pull-Upが有効になっているとき、外部処理で論理レベルを反対のレベルにする場合、 R\_pu = 20.9K $\Omega$ とVIL(MAX) = 0.8Vを考慮すると外部Pull Down=7.16K $\Omega$ 以下とする。

#### Recommended Operating Conditionより抜粋

| · •                                                                                             |       |      |       | _ |

|-------------------------------------------------------------------------------------------------|-------|------|-------|---|

| V <sub>CCIO</sub> = 3.3 V, Bank 0, Bank 1,<br>Bank 2, Bank 3, Bank 4, Bank<br>7, Bank 8, Bank 9 | 3.135 | 3.30 | 3.465 | V |

|                                                                                                 |       |      |       |   |

#### sysI/O Single-Ended DC Electrical Characteristicsより抜粋

#### 3.12. sysI/O Single-Ended DC Electrical Characteristics<sup>3</sup>

Table 3.15. sysI/O DC Electrical Characteristics – Wide Range I/O (Over Recommended Operating Conditions)

| Input/Output Standard | V <sub>IL</sub> <sup>1</sup> |         | V <sub>IH</sub> <sup>1</sup> |                    | V <sub>OL</sub> Max (V)   | V <sub>OH</sub> Min <sup>2</sup> (V) | I <sub>OL</sub> (mA)             | I <sub>OH</sub> (mA)                   |  |

|-----------------------|------------------------------|---------|------------------------------|--------------------|---------------------------|--------------------------------------|----------------------------------|----------------------------------------|--|

| input/Output Standard | Min (V)                      | Max (V) | Min (V)                      | Max (V)            | V <sub>OL</sub> IVIAX (V) | VOH WITH (V)                         | I <sub>OL</sub> (MA)             | IOH(INA)                               |  |

| LVTTL33               | _                            | 0.8     | 2.0                          | 3.465⁵             | 0.4                       | V <sub>CCIO</sub> - 0.4              | 4, 8, 12,<br>"50RS" <sup>3</sup> | -4, -8,<br>-12,<br>"50RS" <sup>3</sup> |  |

| LVCMOS33              | _                            | 0.8     | 2.0                          | 3.4655             | 0.4                       | 2.4                                  | 2                                | -2                                     |  |

|                       | _                            | 0.8     | 2.0                          | 3.465 <sup>5</sup> | 0.49                      | V <sub>CCIO</sub> - 0.58             | 16                               | -16                                    |  |

|                 | · ·                                    | t and the second |     |   |      |    |

|-----------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---|------|----|

| I <sub>PU</sub> | I/O Weak Pull-up Resistor<br>Current   | $0 \le V_{IN} \le 0.7 \times V_{CCIO}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -30 | _ | -150 | μА |

| I <sub>PD</sub> | I/O Weak Pull-down Resistor<br>Current | $V_{IL}$ (max) $\leq V_{IN} \leq V_{CCIO}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 30  | _ | 150  | μА |

## 2.3 内部 Pull up/down の抵抗値 (6/7)

・実際の計算例 LVCOMS33 の場合(MachXO5-NX)

内部 Pull-Up 抵抗 R\_PD は流れる電流 IPD と電圧降下V\_deltaを考慮して計算。

| Ipdが最大になるのはV_deltaが最大の時、即ちVIN=V <sub>CCIO</sub> のとき |       |         |         |                   |  |

|-----------------------------------------------------|-------|---------|---------|-------------------|--|

|                                                     | VIN   | V_delta | lpd(uA) | $R_{pd}(K\Omega)$ |  |

| LVCMOS33_max                                        | 3.465 | 3.465   | 150     | 23.1              |  |

| LVCMOS33_min                                        | 3.135 | 3.135   | 150     | 20.9              |  |

| Ipdが最少になるのはVIN=VIL(Max)の際                           |       |         |         |                   |  |

|                                                     | VIN   | V_delta | lpd(uA) | $R_{pd}(K\Omega)$ |  |

| LVCMOS33_max                                        | 0.8   | 2.665   | 30      | 26.666            |  |

| LVCMOS33_min                                        | 0.8   | 2.335   | 30      | 26.666            |  |

従って、LVCMOS33では内部Pull-Downが有効になっているとき、外部処理で論理レベルを反対のレベルにする場合、 R\_pd = 20.9K $\Omega$ と、VIH(MIN) = 2.0Vを考慮すると 外部Pull Up=11.86K $\Omega$ 以下とする。

#### Recommended Operating Conditionより抜粋

| 1 | •                                                                                               |       |      |       |   |

|---|-------------------------------------------------------------------------------------------------|-------|------|-------|---|

|   | V <sub>CCIO</sub> = 3.3 V, Bank 0, Bank 1,<br>Bank 2, Bank 3, Bank 4, Bank<br>7, Bank 8, Bank 9 | 3.135 | 3.30 | 3.465 | V |

|   |                                                                                                 |       |      |       |   |

#### sysI/O Single-Ended DC Electrical Characteristicsより抜粋 3.12. sysI/O Single-Ended DC Electrical Characteristics³

#### Table 3.15. sysI/O DC Electrical Characteristics – Wide Range I/O (Over Recommended Operating Conditions)

| Innut/Outnut Standard | V <sub>IL</sub> 1 |         | V <sub>IH</sub> <sup>1</sup> |                    | V <sub>OL</sub> Max (V)   | V <sub>OH</sub> Min² (V)   | I <sub>OI</sub> (mA)             | 1 ( 0)                                 |

|-----------------------|-------------------|---------|------------------------------|--------------------|---------------------------|----------------------------|----------------------------------|----------------------------------------|

| Input/Output Standard | Min (V)           | Max (V) | Min (V)                      | Max (V)            | V <sub>OL</sub> IVIAX (V) | V <sub>OH</sub> IVIII- (V) | I <sub>OL</sub> (mA)             | I <sub>OH</sub> (mA)                   |

| LVTTL33               | _                 | 0.8     | 2.0                          | 3.465⁵             | 0.4                       | V <sub>CCIO</sub> - 0.4    | 4, 8, 12,<br>"50RS" <sup>3</sup> | -4, -8,<br>-12,<br>"50RS" <sup>3</sup> |

| LVCMOS33              | _                 | 0.8     | 2.0                          | 3.465 <sup>5</sup> | 0.4                       | 2.4                        | 2                                | -2                                     |

|                       | _                 | 0.8     | 2.0                          | 3.4655             | 0.49                      | V <sub>CCIO</sub> – 0.58   | 16                               | -16                                    |

| I <sub>PU</sub> | I/O Weak Pull-up Resistor<br>Current   | $0 \le V_{IN} \le 0.7 \times V_{CCIO}$                      | -30 | - | -150 | μА |

|-----------------|----------------------------------------|-------------------------------------------------------------|-----|---|------|----|

| I <sub>PD</sub> | I/O Weak Pull-down Resistor<br>Current | V <sub>IL</sub> (max) ≤ V <sub>IN</sub> ≤ V <sub>CCIO</sub> | 30  | _ | 150  | μА |

## 2.3 内部 Pull up/down の抵抗値 (7/7)

下表は前ページの計算式に従い、それぞれの電圧で計算した結果。

|                                   | 内部プルアップ |         | 内部プルダウン |          |  |

|-----------------------------------|---------|---------|---------|----------|--|

|                                   | MIN     | MAX     | MIN     | MAX      |  |

| LVCMOS33(V <sub>CCIO</sub> =3.3V) | 20.9ΚΩ  | 34.65ΚΩ | 20.9ΚΩ  | 26.666ΚΩ |  |

| LVCMOS25(V <sub>CCIO</sub> =2.5V) | 15.83ΚΩ | 26.25ΚΩ | 15.83ΚΩ | 23.333ΚΩ |  |

| LVCMOS18(V <sub>CCIO</sub> =1.8V) | 11.4ΚΩ  | 18.9ΚΩ  | 11.4ΚΩ  | 19.95ΚΩ  |  |

従って、内部端子処理の論理レベルと反対のレベルにする必要がある場合は、以下の値を推奨 (LVCMOS, LVTTL など)。

|                                   | 外部プルアップ推奨値 | 外部プルダウン推奨値 |

|-----------------------------------|------------|------------|

| LVCMOS33(V <sub>CCIO</sub> =3.3V) | 11.86ΚΩ以下  | 7.16ΚΩ以下   |

| LVCMOS25(V <sub>CCIO</sub> =2.5V) | 6.28KΩ以下   | 6.61ΚΩ以下   |

| LVCMOS18(V <sub>CCIO</sub> =1.8V) | 3.13ΚΩ以下   | 3.13ΚΩ以下   |

内部処理が無い専用ピンにつける外部処理の抵抗値としては3.13kΩ以下を推奨。 或いはフェイルセーフ的な観点や設計要件によって、内部端子処理と同じレベルで外部端子処理を行う場合も同様。

## 2.4 電源起動時のI/Oの挙動に関して

■本項は、Lattice 社の以下の資料より抜粋した情報です。 なお、Lattice 社の英文資料の情報を正とします。

sysCONFIG Port Timing Specifications より抜粋

| Certus-NX<br>Certus-NX Family Data Sheet       | FPGA-DS-02078-1.9 | January 2024  |

|------------------------------------------------|-------------------|---------------|

| CertusPro-NX<br>CertusPro-NX Family Data Sheet | FPGA-DS-02086-1.8 | February 2024 |

| CrossLink-NX<br>CrossLink-NX Family Data Sheet | FPGA-DS-02049-2.0 | October 2023  |

| MachXO5-NX<br>MachXO5-NX Family Data Sheet     | FPGA-DS-02102-1.5 | October 2023  |

© Macnica, Inc.

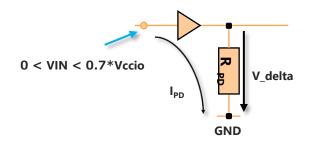

## 2.4 電源起動時のI/Oの挙動に関して (1/6)

専用ピンの状態変化を記しています。

専用ピンは、専用ピンとしてのみ使用する事を強く推奨。

TCK,TMS,TDI,TDO,JTAG\_N,PROGRAMN,INITN,DONEは外に配線を出しておく事を推奨。

デバッグを考慮した基板設計を推奨。

Power ON

コンフィギュ関連ピンは専用ピンとしてご使用頂く事を強く推奨。MCLKを汎用ピンとして使用する場合は、ワイヤードOR接続を推奨。

Power on Reset解除(各雷圧の詳細は14ページ参昭)

| 00,1        |                             |                                      |                                      |

|-------------|-----------------------------|--------------------------------------|--------------------------------------|

| ux          |                             |                                      |                                      |

| Pin Name    | Power up (Default State)    | Initialization & Configuration       | Wake up & User Mode                  |

| 汎用IO        | Hi-z and internal pull down | Hi-z and internal pull down          | 開発ツールで設定している状態                       |

| JTAG_ENABLE | Hi-z and internal pull down | Hi-z and internal pull down          | Hi-z and internal pull down          |

| PROGRAMN    | Hi-z and internal pull up   | Hi-z and internal pull up 36ページ参照    | Hi-z and internal pull up 36ページ参照    |

| INITN       | Hi-z and internal pull up   | Hi-z and internal pull up 37~38ページ参照 | Hi-z and internal pull up 37~38ページ参照 |

| DONE        | Hi-z and internal pull up   | Hi-z and internal pull up 39ページ参照    | Hi-z and internal pull up 39ページ参照    |

| MCLK        | Hi-z and internal pull Down | Hi-z and internal pull Down          | Hi-z and internal pull Down          |

| MCSN        | Hi-z and internal pull up   | Hi-z and internal pull up            | Hi-z and internal pull up            |

| MOSI/MD0    | Hi-z and internal pull up   | Hi-z and internal pull up            | Hi-z and internal pull up            |

| MISO/MD1    | Hi-z and internal pull up   | Hi-z and internal pull up            | Hi-z and internal pull up            |

| MD2         | Hi-z and internal pull up   | Hi-z and internal pull up            | Hi-z and internal pull up            |

| MD3         | Hi-z and internal pull up   | Hi-z and internal pull up            | Hi-z and internal pull up            |

| CSNO/SDO    | Hi-z and internal pull up   | Hi-z and internal pull up            | Hi-z and internal pull up            |

Configuration完了

## 2.4 電源起動時のI/Oの挙動に関して (2/6)

Data Sheet sysCONFIG Port Timing Specifications より抜粋

sysCONFIG User Guide for Nexus Platform FPGA-TN-02099-2.9 February 2024

## 2.4 電源起動時のI/Oの挙動に関して (3/6)

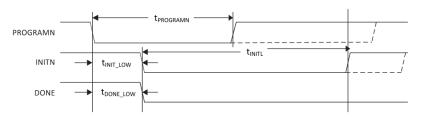

#### **PROGRAMN**

PROGRAMNは、FPGA のコンフィギュレーションに使用される入力端子。 アサートにより、デバイスのプログラミングフローを制御。 Low アクティブで、内部にWeak プルアップがある。 Low アサートされると、FPGA はユーザーモードを終了してデバイスのプログラムを開始。 前述の初期化段階でデバイスのコンフィギュレーションシーケンスを開始。

ピンをLow に保持すると、Nexus デバイスが初期化段階から抜けないようになります。PROGRAMN には最小パルス幅によって認識され る最短パルス幅アサート期間(tPROGRAMN)がある。この最小時間は『sysCONFIG User Guide for Nexus Platform 』(FPGA-TN-02099-2.9)、『 Nexusファミリ・データシート』)の「sysCONFIG Port Timing Specification 」に記載。

Certus-NX ファミリ・データシート、CertusPro-NX ファミリ・データシート、CrossLink-NX-33 およびMachXO5-NX データシートを参照。

#### PROGRAMNピンがアクティブの場合、以下の特殊なケースに注意:

- デバイスがJTAG 経由でプログラムされている場合、PROGRAMN ピンはJTAG モードのプログラミング・シーケンスが完了するまで無 視される。

- デバイスのコンフィギュレーション中にPROGRAMN ピンをトグルすると、プロセスが中断され、コンフィギュレーション・サイクル が再スタート。

- デバイスが初期化状態にある間は、PROGRAMNが立ち下がりエッジに遷移してはいけない。 コンフィギュレーションを中断、再開、失敗させないために、PROGRAMN は最低tPROGRAMN 期間アサートしなければならない。 この要件を満たさないと、デバイスが動作不能になる可能性があり、電源の再投入が必要になる。

## 2.4 電源起動時のI/Oの挙動に関して (4/6)

#### INITN

INITN ピンは双方向オープンドレイン制御ピンで、以下の機能を保有:

- 電源投入後およびPROGRAMN アサート後、またはREFRESH コマンド後にLow となり、SRAM コンフィギュレーション・メ モリが消去されることを示す。

- Low アサート時間はtINIT LOW パラメータで指定。

- tINITL 時間経過後、INITN ピンはディアサート(アクティブHi )され、Nexus デバイスがコンフィギュレーション・ビット を使用できる状態になったことを示す。

- Nexus デバイスは外部SPI フラッシュからのコンフィギュレーションデータのロードを開始。

- INITN がコンフィギュレーションビットを読み出さないようにするには、tINITL 時間が経過する前に外部エージェントが INITN をLow にアサート。

- INITN がコンフィギュレーションビットを読み出すことを防止できる。これは、複数のプログラマブルデバイスが連結され ている場合に有用。

- 時間が最長のプログラマブルデバイスは、チェーン内の他のすべてのデバイスがデータを取得するのを、そのデバイス自身 が準備完了するまで抑えることが可能。

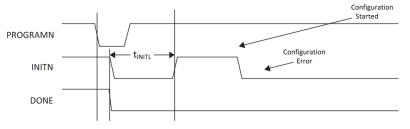

- INITN が提供する最後の機能は、コンフィギュレーション・データが読み出されている間のエラー通知。tINITL が経過しピ ンがHigh になると、それ以降INITN がアサートされると、Nexus デバイスがコンフィギュレーション中にエラーを検出した ことを诵知。

## 2.4 電源起動時のI/Oの挙動に関して (5/6)

#### INITN

以下の条件では、INITN がアクティブになり、初期化状態がアクティブであることを示す:

- 電源が投入された。

- PROGRAMN の立ち下がりエッジが発生。

- IEEE1532 REFRESHコマンドがスレーブ・コンフィギュレーション・ポート(JTAG またはSSPI )を使用して送信された。 INITNピンがアサートされる。

ピンがエラー状態でアサートされた場合、コンフィギュレーションのビットストリームを修正してFPGA を強制的に初期化状 態にすることでエラーをクリア可能。

初期化状態に強制的に移行させることで、エラーをクリア可能。

ビットストリームの読み出し時にエラーが検出された場合、INITN はLow になり、内部DONE ビットは設定されず、DONE ピ ンはLow のままで、デバイスはウェイクアップしない。

#### 次の場合は、デバイスのコンフィギュレーションに失敗:

- ビットストリームのCRCエラーを検出。

- 無効なコマンドエラーを検出。

- ◆ 外部フラッシュメモリからのロード時にタイムアウトエラーが発生。これは、デバイスがコンフィギュレーションモードで SPI フラッシュデバイスがプログラムされていない場合に発生する可能性あり。

- オンチップSRAM コンフィギュレーションまたは外部フラッシュメモリの終端に到達してもプログラム完了コマンドが受信 されない。

# 2.4 電源起動時のI/Oの挙動に関して (6/6)

#### DONE

DONE ピンは、FPGA がユーザーモードであることを示す双方向オープンドレインで、Weak プルアップがある。

DONE は、内部DONE ビットがアサートされた後にのみユーザーモードに移行可能。

内部DONE ビットは、FPGAのウェイクアップ状態の開始を定義。

内部DONE ビットがアサートされた後、GPIO がウェイクアップし、10us 後にDONE ピンがHigh になる。これは、DONEL

内部DONE ビットがアサートされた後、GPIO がウェイクアップし、10μs 後にDONE ピンがHigh になる。これは、DONEピ ンがHighになる前にGPIOピンの設定が適用されることを意味する。

外部エージェントがDONE ピンをLow にアサートし続けることで、FPGA のユーザーモードへの移行を無期限に停止可能。 DONE ピンをLow 駆動し続ける一般的な理由は、複数のFPGA を同時にコンフィギュレーション完了させることです。各FPGA がDONE 状態に達すると、論理動作を開始する準備が整う。最後にコンフィギュレーションされるFPGA がすべてのFPGA を一斉に起動させる。

FPGA が初期化モードに入ると、DONE ピンはINITN ピンと連動しLow に駆動される。 前述のように、この状態は、DONE ピンがアサートされるか、またはアクティブなコンフィギュレーションポートを介して IEEE 1532 REFRESH コマンドを受信した場合に発生。

DONE ピンをサンプリングすることで、FPGA がコンフィギュレーションを完了したかどうか外部デバイスが判断可能。

# 3. sysI/O BANK関連

### 3.1 sysI/O BANK関連(Certus-NX,CertusPro-NX/CrossLink-NX/MachXO5-NX,MachXO5T-NX)

■本項は、 Lattice 社の以下の資料より抜粋した情報です。 なお、Lattice 社の英文資料の情報を正とします。

sysI/O Banking Scheme より抜粋

Certus-NX

Certus-NX Family Data Sheet FPGA-DS-02078-1.9 January 2024

CertusPro-NX

February 2024 CertusPro-NX Family Data Sheet FPGA-DS-02086-1.8

CrossLink-NX

CrossLink-NX Family Data Sheet FPGA-DS-02049-2.0 October 2023

MachXO5-NX

MachXO5-NX Family Data Sheet FPGA-DS-02102-1.5 October 2023

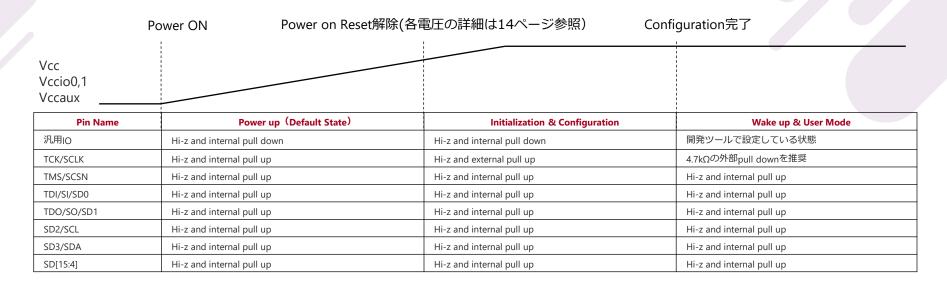

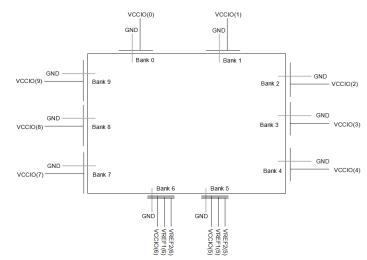

#### 3.1.1 Certus-NX BANK構成

#### BANK 構成の概要

- Certus-NXはBANK0~7のsysI/O BANK で構成

- BANKO, 1, 2, 6, 7は1.2V~3.3VのSingle-Ended IOをサポート

- BANK3, 4, 5は, 1.0V~1.8VのStaticとDynamicのTerminationがあり、Differential IOやDDR Memory IFをサポート

- BANKO, 1, 2, 6, 7はHot Socket に対応

- BANK3, 4, 5はHot Socket に非対応

VCCIO(7)

Bank 7

Bank 1

GND

WCCIO(1)

Bank 2

GND

Bank 3

Bank 3

GND

WCCIO(2)

Bank 5

Bank 4

Bank 3

WCCIO(2)

Bank 5

GND

WCCIO(2)

Bank 5

GND

WCCIO(2)

Bank 6

Bank 7

WCCIO(2)

Bank 7

WCCIO(2)

Bank 8

Bank 9

WCCIO(2)

Bank 9

WCC

VCCIO(0)

sysI/O Banking Scheme より抜粋

Certus-NX Family Data Sheet FPGA-DS-02078-1.9 January 2024

#### 3.1.2 CertusPro-NX BANK構成

#### BANK 構成の概要

- CertusPro-NXはBANK0~7のsysI/O BANK で構成

- BANKO, 1, 2, 6, 7は1.2V~3.3VのSingle-Ended IOをサポート

- BANK3, 4, 5は1.0V~1.8VのStaticとDynamicのTerminationがあり、Differential IOやDDR Memory IFをサポート

- BANKO, 1, 2, 6, 7ではHot Socketに対応

- BANK3, 4, 5ではHot Socketに非対応

sysI/O Banking Scheme より抜粋

CertusPro-NX Family Data Sheet FPGA-DS-02086-1.8 February 2024

Figure 2.27. sysI/O Banking

#### 3.1.3 CrossLink-NX BANK構成

#### BANK 構成の概要

- CrossLink-NXはBANK0~7のsysI/O BANK で構成

- BANKO, 1, 2, 6, 7は1.2V~3.3VのSingle-Ended IOをサポート

- BANK3, 4, 5は, 1.0V~1.8VのStaticとDynamicのTerminationがあり、Differential IOやDDR Memory IFをサポート

- BANKO, 1, 2, 6, 7はHot Socketに対応

- BANK3, 4, 5はHot Socket非対応

VCCIO(7)

| Bank 7\* | Bank 1 | GND | VCCIO(1)

| VCCIO(6) | Bank 6\* | Bank 2\* | GND | VCCIO(2)

| Bank 5 | Bank 4 | Bank 3 | GND | G

VCCIO(0)

Bank 0

sysI/O Banking Scheme より抜粋

CrossLink-NX Family Data Sheet FPGA-DS-02049-2.0 October 2023

Figure 2.27. sysI/O Banking

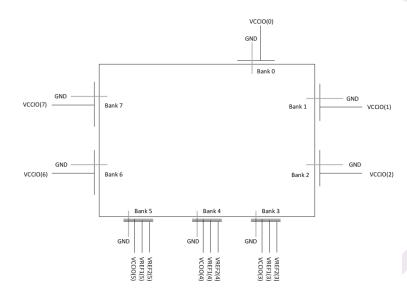

#### 3.1.4 Mach XO5-NX BANK構成

#### BANK 構成の概要

- Mach XO5-NXはBANK0~7のsysI/O BANK で構成

- BANKO, 2, 3, 4, 7, 8, 9は1.0V~3.3VのSingle-Ended IOをサポート

- BANK1は3.3VのSingle-Ended IOのみサポート

- BANK5, 6は 1.0V~1.8V StaticとDynamicのTerminationがあり、Differential IOやDDR Memory IFをサポート

- BANKO, 2, 3, 4, 7, 8, 9はHot Socket に対応

- BANK5, 6はHot Socket非対応

sysI/O Banking Scheme より抜粋

MachXO5-NX Family Data Sheet FPGA-DS-02102-1.5 October 2023

Figure 2.31. sysl/O Banking of MachXO5-NX-25 Devices

■各I/O Standard と対応BANK まとめ(Certus-NX, CertusPro-NX, CrossLink-NX)

| Standard                           | Support Banks | V <sub>CCIO</sub> (Input)              | V <sub>CCIO</sub> (Output) |  |

|------------------------------------|---------------|----------------------------------------|----------------------------|--|

| Standard                           | Support banks | Тур.                                   | Тур.                       |  |

| Single-Ended                       |               |                                        |                            |  |

| LVCMOS33                           | 0, 1, 2, 6, 7 | 3.3                                    | 3.3                        |  |

| LVTTL33                            | 0, 1, 2, 6, 7 | 3.3                                    | 3.3                        |  |

| LVCMOS25 <sup>1, 2</sup>           | 0, 1, 2, 6, 7 | 2.5, 3.3                               | 2.5                        |  |

| LVCMOS18 <sup>1, 2</sup>           | 0, 1, 2, 6, 7 | 1.2, 1.5, 1.8, 2.5, 3.3                | 1.8                        |  |

| LVCMOS18H                          | 3, 4, 5       | 1.8                                    | 1.8                        |  |

| LVCMOS15 <sup>1, 2</sup>           | 0, 1, 2, 6, 7 | 1.2, 1.5, 1.8, 2.5, 3.3                | 1.5                        |  |

| LVCMOS15H <sup>1</sup>             | 3, 4, 5       | 1.5, 1.8                               | 1.5                        |  |

| LVCMOS12 <sup>1, 2</sup>           | 0, 1, 2, 6, 7 | 1.2, 1.5, 1.8, 2.5, 3.3                | 1.2                        |  |

| LVCMOS12H <sup>1</sup>             | 3, 4, 5       | 1.2, 1.35 <sup>6</sup> , 1.5, 1.8      | 1.2                        |  |

| LVCMOS10 <sup>1</sup>              | 0, 1, 2, 6, 7 | 1.2, 1.5, 1.8, 2.5, 3.3                | _                          |  |

| LVCMOS10H <sup>1</sup>             | 3, 4, 5       | 1.0, 1.2, 1.35 <sup>6</sup> , 1.5, 1.8 | 1.0                        |  |

| LVCMOS10R <sup>1</sup>             | 3, 4, 5       | 1.0, 1.2, 1.35 <sup>6</sup> , 1.5, 1.8 | <del></del>                |  |

| SSTL135_I, SSTL135_II <sup>3</sup> | 3, 4, 5       | 1.356                                  | 1.35                       |  |

| SSTL15_I, SSTL15_II <sup>3</sup>   | 3, 4, 5       | 1.57                                   | 1.5 <sup>7</sup>           |  |

| HSTL15_I <sup>3</sup>              | 3, 4, 5       | 1.5 <sup>7</sup>                       | 1.5 <sup>7</sup>           |  |

| HSUL12 <sup>3</sup>                | 3, 4, 5       | 1.2                                    | 1.2                        |  |

Data Sheet Supported sysI/O Standards より抜粋

■各I/O Standard と対応BANK まとめ(Certus-NX, CertusPro-NX, CrossLink-NX)

| Standard                             | Support Banks | V <sub>CCIO</sub> (Input)<br>Typ.                   | V <sub>CCIO</sub> (Output)                     |

|--------------------------------------|---------------|-----------------------------------------------------|------------------------------------------------|

| Differential                         |               | Τуρ.                                                | Тур.                                           |

| LVDS                                 | 3, 4, 5       | 1.2, 1.35, 1.5, 1.8                                 | 1.8                                            |

| LVDSE <sup>5</sup>                   | 0, 1, 2, 6, 7 | _                                                   | 2.5                                            |

| subLVDS                              | 3, 4, 5       | 1.2, 1.35, 1.5, 1.8                                 | _                                              |

| subLVDSE <sup>5</sup>                | 0, 1, 2, 6, 7 | _                                                   | 1.8                                            |

| subLVDSEH <sup>5</sup>               | 3, 4, 5       | _                                                   | 1.8                                            |

| SLVS                                 | 3, 4, 5       | 1.0, 1.2, 1.35 <sup>6</sup> , 1.5, 1.8 <sup>4</sup> | 1.2, 1.35 <sup>6</sup> , 1.5, 1.8 <sup>4</sup> |

| LVCMOS33D <sup>5</sup>               | 0, 1, 2, 6, 7 | _                                                   | 3.3                                            |

| LVTTL33D⁵                            | 0, 1, 2, 6, 7 | _                                                   | 3.3                                            |

| LVCMOS25D <sup>5</sup>               | 0, 1, 2, 6, 7 | _                                                   | 2.5                                            |

| SSTL135D_I, SSTL135D_II <sup>5</sup> | 3, 4, 5       | _                                                   | 1.35 <sup>6</sup>                              |

| SSTL15D_I, SSTL15D_II <sup>5</sup>   | 3, 4, 5       | _                                                   | 1.5                                            |

| HSTL15D_I <sup>5</sup>               | 3, 4, 5       | _                                                   | 1.5                                            |

| HSUL12D⁵                             | 3, 4, 5       |                                                     | 1.2                                            |

Data Sheet Supported sysl/O Standards より抜粋

■各I/O Standard と対応BANK まとめ(Certus-NX, CertusPro-NX, CrossLink-NX)

#### 備考

- 1.シングルエンド入力は、標準と異なるVCCIO を持つI/O Bankに混在する可能性がある。 これは、これらの入力規格の一部が入力バッファの電源として内部電源電圧源(VCC、VCCAUX)を使用し、VCCIO 電圧に依存しないため。詳細は、Certus-NX High-Speed I/O Interface (FPGA-TN-02216)参照。 以下に簡単なガイドラインを示す:

- a. I/O のWeak プルアップはオフに設定。

- b. Bank3, 4およびBank5のI/O はこのBank のクランプダイオードにより、VCCIO がI/O Standard より高いBank にのみ混在可能。Bank0, 1, 2、Bank6, 7にこの制限はない。

- c. LVCMOS25 はBankO, 1, 2、Bank6, 7の入力バッファにVCCIO 電源を使用。

VCCIO =VIH とVIL の要件を満たすためにVCCIO = 3.3V でサポートできるが、VCCIO に流れる電流が増加。

電源電圧3.3V を使用する場合、ヒステリシスを無効にする必要あり。

- d. LVCMOS15 はBank3, 4, 5 の入力バッファにVCCIO 電源を使用。

VIH とVIL の要件を満たすためにVCCIO = 1.8V でサポートできるが、VCCIO に流れる電流が増加。

- 2.シングルエンドLVCMOS 入力は、Weak プルアップが使用されない限り、異なるVCCIO のI/O Bankに混在可能。 Bank VCCIO の混在I/O に関する詳細は、Certus-NX High-Speed I/O Interface (FPGA-TN-02216) 参照。

- 3.これらの入力は、 Bank3, 4, 5 で差動入力コンパレータを使用。差動入力コンパレータはVCCAUXH 電源を使用。これらの入力には、Bank 内の基準電圧を供給するVREF ピンが必要。 詳細はCertus-NX High-Speed I/O Interface (FPGA-TN-02216) 参照。

- 4. すべての差動入力は、Bank3, 4 およびBank5で差動入力コンパレータを使用。 差動入力コンパレータは、VCCAUXH 電源を使用。 Bank0, 1, 2、Bank6, 7では、差動入力信号は未サポート。

■各I/O Standard と対応BANK まとめ(Certus-NX, CertusPro-NX, CrossLink-NX)

#### 備考

- 5.これらの出力は、シングルエンド出力ドライバで差動出力ペアをエミュレートしており、真の出力と補数の出力は、対応する真の出力と補数の出力ペアピンのそれぞれを駆動する。 コモンモード電圧VCM は½ \* VCCIO である。 詳細は『Certus-NX High-Speed I/O Interface』(FPGA-TN-02216) 参照。

- 6.VCCIO =1.35V は、Bank 内のDDR3L インターフェイスで使用するため、Bank3, 4, 5でのみサポート。 これらの入出力規格は、VCCIO = 1.35V で同一Bank に収めることが可能。

- 7.LVCMOS15 入力はVCCIO の電源電圧を使用。

VCCIO が1.8V の場合、LVCMOS15のDC レベルは満たされるが、入力バッファ電流が増加する可能性がある。

■各I/O Standard と対応BANK まとめ(MachXO5-NX)

| Standard                           | Support Panks          | V <sub>CCIO</sub> (Input)              | V <sub>CCIO</sub> (Output) |  |

|------------------------------------|------------------------|----------------------------------------|----------------------------|--|

| Standard                           | Support Banks          | Тур.                                   | Тур.                       |  |

| Single-Ended                       |                        |                                        |                            |  |

| LVCMOS33                           | 0, 1, 2, 3, 4, 7, 8, 9 | 3.3                                    | 3.3                        |  |

| LVTTL33                            | 0, 1, 2, 3, 4, 7, 8, 9 | 3.3                                    | 3.3                        |  |

| LVCMOS25 <sup>1, 2</sup>           | 0, 2, 3, 4, 7, 8, 9    | 2.5, 3.3                               | 2.5                        |  |

| LVCMOS18 <sup>1, 2</sup>           | 0, 2, 3, 4, 7, 8, 9    | 1.2, 1.5, 1.8, 2.5, 3.3                | 1.8                        |  |

| LVCMOS18H                          | 5, 6                   | 1.8                                    | 1.8                        |  |

| LVCMOS15 <sup>1, 2</sup>           | 0, 2, 3, 4, 7, 8, 9    | 1.2, 1.5, 1.8, 2.5, 3.3                | 1.5                        |  |

| LVCMOS15H <sup>1</sup>             | 5, 6                   | 1.5, 1.8                               | 1.5                        |  |

| LVCMOS12 <sup>1, 2</sup>           | 0, 2, 3, 4, 7, 8, 9    | 1.2, 1.5, 1.8, 2.5, 3.3                | 1.2                        |  |

| LVCMOS12H <sup>1</sup>             | 5, 6                   | 1.2, 1.35 <sup>7</sup> , 1.5, 1.8      | 1.2                        |  |

| LVCMOS10 <sup>1</sup>              | 0, 2, 3, 4, 7, 8, 9    | 1.2, 1.5, 1.8, 2.5, 3.3                | <del>_</del>               |  |

| LVCMOS10H <sup>1</sup>             | 5, 6                   | 1.0, 1.2, 1.35 <sup>7</sup> , 1.5, 1.8 | 1.0                        |  |

| LVCMOS10R <sup>1</sup>             | 5, 6                   | 1.0, 1.2, 1.35 <sup>7</sup> , 1.5, 1.8 | _                          |  |

| SSTL135_I, SSTL135_II <sup>3</sup> | 5, 6                   | 1.35 <sup>7</sup>                      | 1.35                       |  |

| SSTL15_I, SSTL15_II <sup>3</sup>   | 5, 6                   | 1.5 <sup>8</sup>                       | 1.5 <sup>8</sup>           |  |

| HSTL15_I <sup>3</sup>              | 5, 6                   | 1.5 <sup>8</sup>                       | 1.58                       |  |

| HSUL12 <sup>3</sup>                | 5, 6                   | 1.2                                    | 1.2                        |  |

| MIPI D-PHY LP Input <sup>6</sup>   | 5, 6                   | 1.2                                    | 1.2                        |  |

Supported sysl/O Standards より抜粋 Data Sheet

■各I/O Standard と対応BANK まとめ(MachXO5-NX)

| Standard                             | Support Banks          | V <sub>CCIO</sub> (Input)<br>Typ.                   | V <sub>CCIO</sub> (Output)<br>Typ.             |  |  |

|--------------------------------------|------------------------|-----------------------------------------------------|------------------------------------------------|--|--|

| Differential                         |                        | 1 yp.                                               | Typ.                                           |  |  |

| LVDS                                 | 5, 6                   | 1.2, 1.35, 1.5, 1.8                                 | 1.8                                            |  |  |

| LVDSE <sup>5</sup>                   | 0, 2, 3, 4, 7, 8, 9    | _                                                   | 2.5                                            |  |  |

| SubLVDS                              | 5, 6                   | 1.2, 1.35, 1.5, 1.8                                 | _                                              |  |  |

| SubLVDSE <sup>5</sup>                | 0, 2, 3, 4, 7, 8, 9    | _                                                   | 1.8                                            |  |  |

| SubLVDSEH <sup>5</sup>               | 5, 6                   | _                                                   | 1.8                                            |  |  |

| SLVS <sup>6</sup>                    | 5, 6                   | 1.0, 1.2, 1.35 <sup>7</sup> , 1.5, 1.8 <sup>4</sup> | 1.2, 1.35 <sup>7</sup> , 1.5, 1.8 <sup>4</sup> |  |  |

| MIPI D-PHY <sup>6</sup>              | 5, 6                   | 1.2                                                 | 1.2                                            |  |  |

| LVCMOS33D <sup>5</sup>               | 0, 1, 2, 3, 4, 7, 8, 9 | _                                                   | 3.3                                            |  |  |

| LVTTL33D <sup>5</sup>                | 0, 1, 2, 3, 4, 7, 8, 9 | _                                                   | 3.3                                            |  |  |

| LVCMOS25D <sup>5</sup>               | 0, 2, 3, 4, 7, 8, 9    | _                                                   | 2.5                                            |  |  |

| SSTL135D_I, SSTL135D_II <sup>5</sup> | 5, 6                   | _                                                   | 1.35 <sup>7</sup>                              |  |  |

| SSTL15D_I, SSTL15D_II <sup>5</sup>   | 5, 6                   | _                                                   | 1.5                                            |  |  |

| HSTL15D_I <sup>5</sup>               | 5, 6                   | _                                                   | 1.5                                            |  |  |

Data Sheet Supported sysl/O Standards より抜粋

■各I/O Standard と対応BANK まとめ(MachXO5-NX)

#### 備考

- 1.シングルエンド入力は、標準と異なるVCCIO を持つI/O Bank に混在する可能性がある。 これは、これらの入力規格の一部が、入力バッファの電源として内部電源電圧源(VCC、VCCAUX)を使用し、VCCIO 電圧に依存しな いため。詳細は、sysl/O User Guide for Nexus Platform(FPGA-TN-02067)参照。 以下に簡単なガイドラインを示す:

- a. I/O のWeak プルアップはOFF に設定。

- b. Bank5, 6のI/Oは、これらのBank のクランプダイオードにより、VCCIO がI/O Standard より高いBank にのみ混在可能。 Bank0, 1, 2、3, 4、Bank7, 8, 9にこの制限はない。

- c. LVCMOS25 はBank0, 1, 2, 3, 4、Bank7, 8, 9 の入力バッファにVCCIO 電源を使用。 VIH  $\angle VIL$  の要件を満たすためにVCCIO = 3.3 V でサポートできるが、VCCIO に流れる電流が増加。 電源電圧3.3V を使用する場合は、ヒステリシスを無効にする必要あり。

- d. LVCMOS15 はBank5, 6 の入力バッファにVCCIO 電源を使用。 VIH とVIL の要件を満たすために VCCIO = 1.8V でサポートできるが、VCCIO に流れる電流が増加。

- 2.シングルエンドLVCMOS 入力は、Weak プルアップが使用されない限り、異なるVCCIO のI/O Bank に混在可能。 Bank VCCIO の混在I/O に関する詳細は、sysI/O User Guide for Nexus Platform (FPGA-TN-02067) 参照。

- 3.これらの入力は、Bank5,6で差動入力コンパレータを使用。差動入力コンパレータはVCCAUXH電源を使用。 これらの入力には、Bank 内の基準電圧を供給するVREF ピンが必要。 詳細は、sysl/O User Guide for Nexus Platform (FPGA-TN-02067)参照。

- 4.すべての差動入力はBank5,6で差動入力コンパレータを使用。差動入力コンパレータはVCCAUXH電源を使用。 Bank0, 1, 2, 3, 4、Bank7, 8, 9 では差動入力信号は未サポート。

■各I/O Standard と対応BANK まとめ(MachXO5-NX)

#### 備考

- 5.これらの出力は、シングルエンド出力ドライバで差動出力ペアをエミュレートしており、真の出力と補数の出力は、対応する真の出力と 補数の出力ペアピンのそれぞれを駆動。 コモンモード電圧VCM は、1/2 × VCCIO である。

- 詳細は、sysl/O User Guide for Nexus Platform (FPGA-TN-02067)参照。

- 6.sysl/O を使用するソフトMIPI D-PHY HS は、SLVS で示されるVCCIO 電圧のBank に配置可能なSLVS 入出力でサポート。 HS およびLP モードをサポートするD-PHY は、VCCIO電圧=1.2V のBank に配置する必要がある。 sysI/O を使用するソフトMIPI D-PHY LP 入出力は、LVCMOS12でサポート。

- 7.VCCIO = 1.35V は、Bank 内のDDR3L インターフェイスで使用するため、Bank5, 6でのみサポート。 これらの入出力規格は、VCCIO = 1.35Vで同じBank に収めることが可能。

- 8.LVCMOS15 入力はVCCIO の電源電圧を使用。 VCCIOが1.8Vの場合、LVCMOS15のDCレベルは満たされるが、入力バッファ電流が増加する可能性がある。

- ■各VCCIO 電圧と入力可能なI/O Standard まとめ

- VCC, VCCAUX, VCCIOの3電源を用いることにより各Bank は以下の通りMixed Voltageに対応。

| Wide Range                     | Input Buffers |           |           |             |          |             |

|--------------------------------|---------------|-----------|-----------|-------------|----------|-------------|

|                                |               |           |           |             |          |             |

| VCCIO                          | LVCMOS10      | LVCMOS12  | LVCMOS15  | LVCMOS18    | LVCMOS25 | LVCMOS33    |

| 1.2                            | ✓             | ✓         | ✓         |             |          |             |

| 1.5                            | ✓             | ✓         | <b>\</b>  | <b>&gt;</b> |          |             |

| 1.8                            | ✓             | ✓         | /         | <b>&gt;</b> |          |             |

| 2.5                            | ✓             | <b>✓</b>  | <         | <b>\</b>    | <b>✓</b> |             |

| 3.3                            | ✓             | <b>✓</b>  | /         | >           | ✓        | <b>&gt;</b> |

| High Performance Input Buffers |               |           |           |             |          |             |

| VCCIO                          | LVCMOS10H     | LVCMOS12H | LVCMOS15H | LVCMOS18H   |          |             |

| 1.0                            | ✓             |           |           |             |          |             |

| 1.2                            | ✓             | ✓         |           |             |          |             |

| 1.5                            | /             | /         | /         |             |          |             |

| 1.8                            | ✓             | ✓         | /         | <b>✓</b>    |          |             |

- ■各VCCIO 電圧と入力可能なI/O Standard まとめ

- 外部の2.5V~1.2V IO の信号を受信する場合は、外部にてレベル変換ICを通して3.3Vレベルに変換した後に受信す る事を強く推奨。

- 例として挙げると、外部の1.8V IO の信号をNX にて3.3V IO Bank にて受信するには、外部にてレベル変換ICで、 1.8V→3.3V に信号レベルを変換した後に受信。

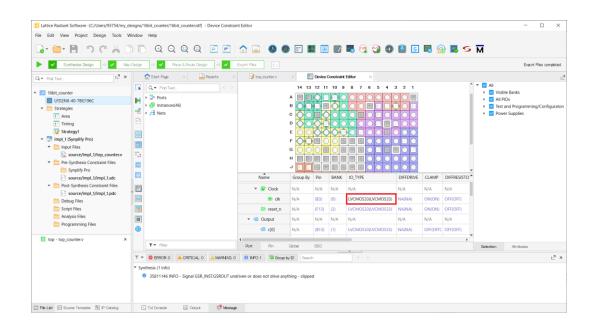

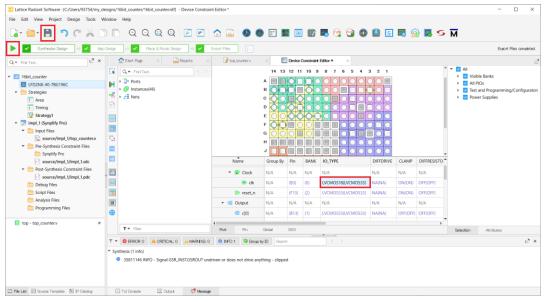

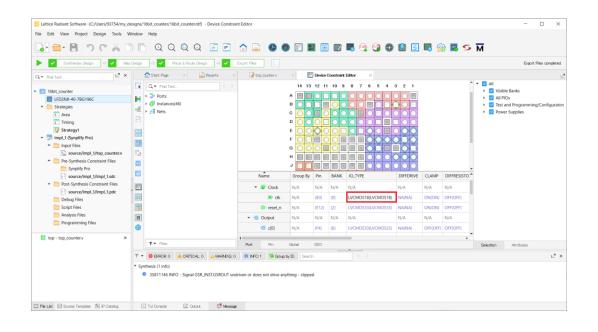

- 設計ツールLattice Radiant ソフトウェアにて入力設定を行わない限り、正常にMixed Voltage Modeの入力を受信で きない。

- ■Lattice Radiant ソフトウェアにて入力設定を行う方法

- 変更前

- ■Lattice Radiant ソフトウェアにて入力設定を行う方法

- 変更方法: Device Constraint Editor => IO TYPE を選択、受信したい信号の電圧に設定。

- 下図ではLVCMOS18 → Save → RUN ALL

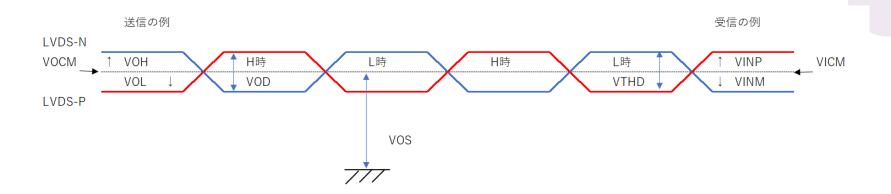

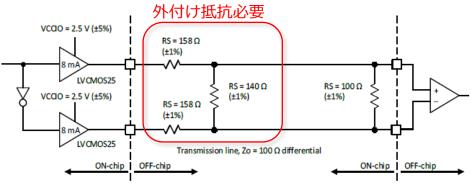

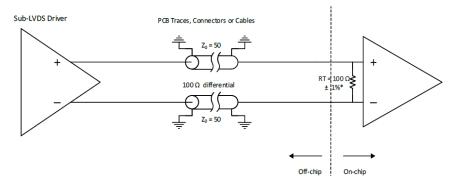

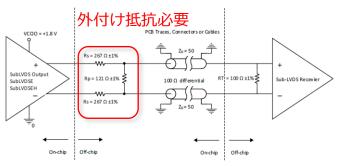

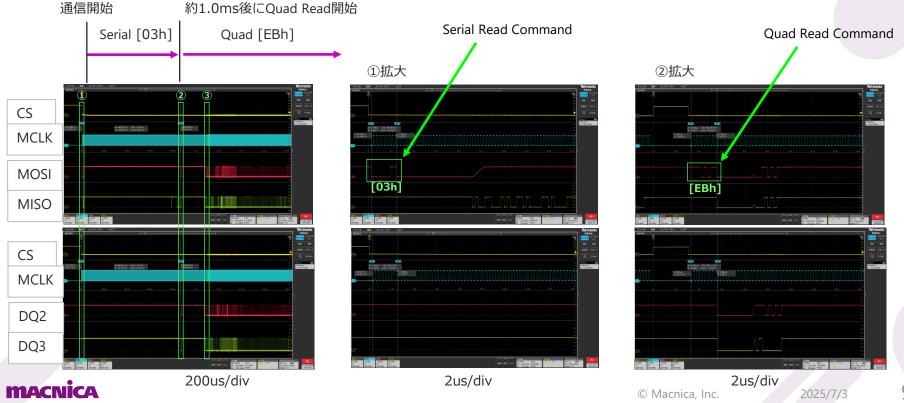

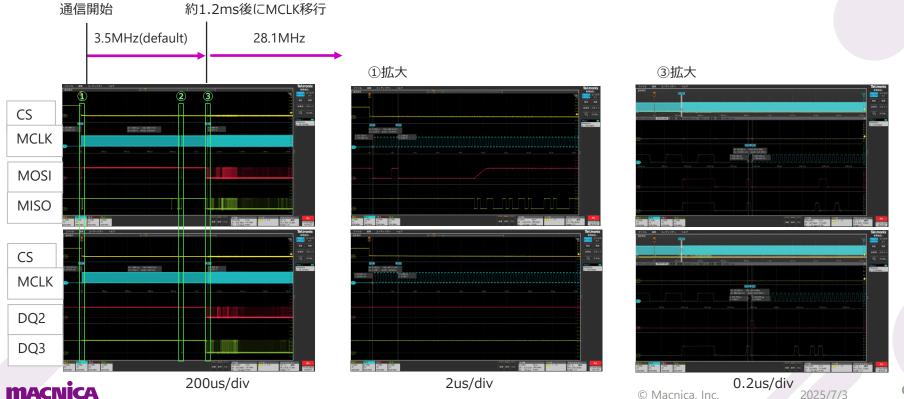

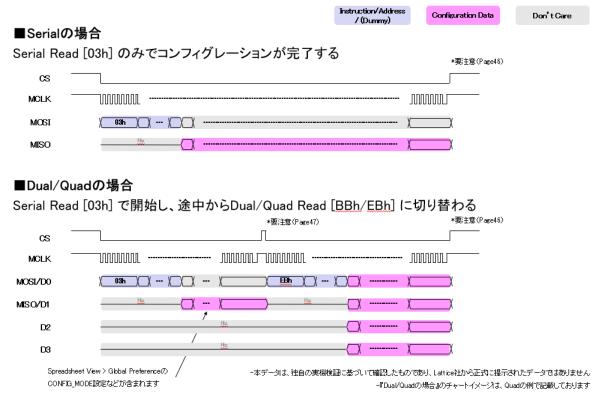

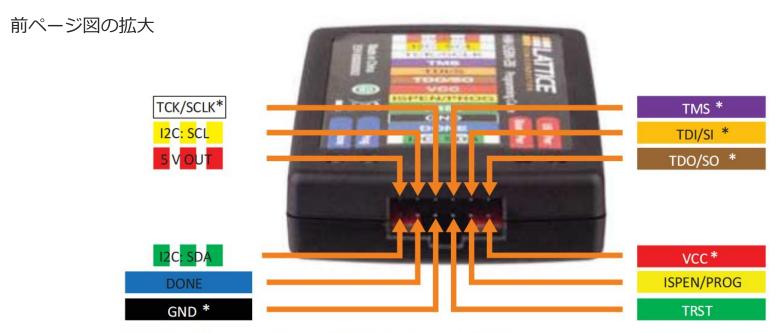

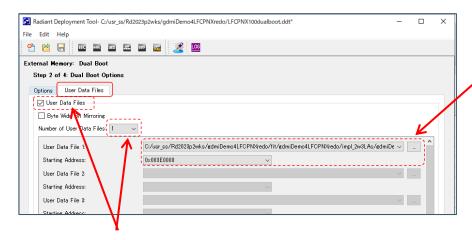

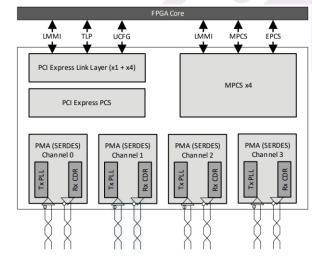

- ■Lattice Radiant ソフトウェアにて入力設定を行う方法