# Quartus II

# Chip Planner クイック・ガイド

ver.9.0 2009 年 8 月

## 1. はじめに

この資料は、Quartus®II の Chip Planner の使用方法を紹介しています。

Chip Planner は、従来の フロアプラン と Chip Editor が統合された機能です。この機能により、Quartus II 上でアルテラ・デバイスの内部構造の表示、内部タイミングの調査、デバイス内のリソースに対する機能とプロパティ設定の編集を行うことができ、本資料では、Chip Planner におけるデザインの 解析 と 変更 について説明します。

※ Chip Planner を使用して配置やプロパティを変更する場合は、デバイスのアーキテクチャに関する知識を要します。

# 2. Chip Planner の概要

Chip Planner は、デザインで使用するターゲット・デバイス内のロジック・エレメント(LE)、アダプティブ・ロジック・モジュール (ALM)、PLL ブロック、DSP ブロック、メモリ・ブロック、I/O エレメントなどの使用状況、それらの配置や接続状況を視覚的に確認および解析ができる機能です。同様に、LogicLock™ 領域の接続、クリティカル・パスの表示、また、ロジック・セル間のルーティング、レジスタ間のファンインおよびファンアウトなども表示ができ、それらのパスにおけるディレイ情報を表示することができます。さらにフロアプランを使用して、ロジック・セルや I/O ブロックのレイアウトの移動や削除などの配置制約やリソース・アサインの変更も可能です。

※ LogicLock については、アルティマ資料「Quartus II - LogicLock クイック・ガイド」をご参照ください。

ECO の変更の際、Chip Planner での作業は、デザイン・ネットリストに直接反映されるため、デザインをコンパイルすることなく、数分で変更内容をデバイスへ実装できます。デザインの他の部分でのタイミング・クロージャを維持するために、変更は特定のデバイス・リソースに限定されます。ユーザが不正な編集をしないように、すべての変更にはデザイン・ルール・チェックが適用されます。その作業をスムーズに行うため、Chip Planner はフロアプラン、リソース・プロパティ・エディタ、チェンジ・マネージャなどのプラットフォームを提供しています。

Chip Planner でサポートされているデバイスは、Arria <sup>®</sup> GX, Arria II GX, Cyclone <sup>®</sup>, Cyclone II, Cyclone III, HardCopy <sup>®</sup> II, MAX <sup>®</sup> II, Stratix <sup>®</sup>, Stratix GX, Stratix II GX, Stratix III, Stratix IV です。なお、Chip Planner がサポートされていないデバイスの場合には、Timing Closure Floorplan を使用してください。

関連資料: Quartus II Handbook volume2 Analyzing and Optimizing the Design Floorplan

http://www.altera.com/literature/hb/qts/qts\_qii52006.pdf

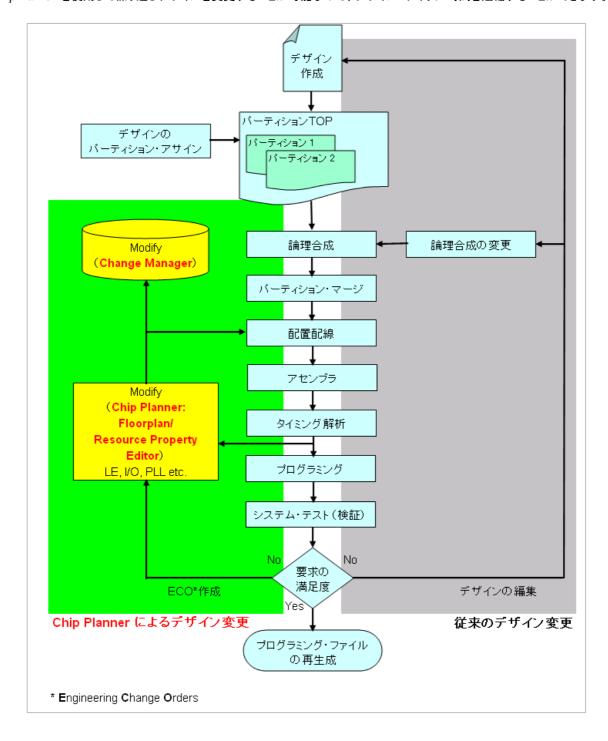

# 3. Chip Planner のデザイン・フロー

以下の図は、設計フローにおける Chip Planner のデザイン・フローを示しています。

RTL コードにバグが見つかったり、開発途中でデザインの仕様が変更されたりした場合、従来は、デザイン・ソースに戻り変更を行い、論理合成、配置配線、検証といった全体のフローをやり直す必要がありました。

Chip Planner を使用すると、以下のようにフル・コンパイルを実行する必要がなく、配置配線後のネットリストに直接変更を加え、新しいプログラミング・ファイルを生成し、タイミング・シミュレーションやタイミング解析を行えます。問題が改善されるまで Chip Planner を使用して繰り返しデザインを変更することが可能なので、デザイン・サイクル時間を短縮することができます。

# 4. デザイン解析

Chip Planner を使用するためには、コンパイルが終了していることが条件になります。コンパイルを実行していない場合は、以下のフローでコンパイルを行ってください。

- Processing メニュー ⇒ Start Compilation または ► ボタンをクリック

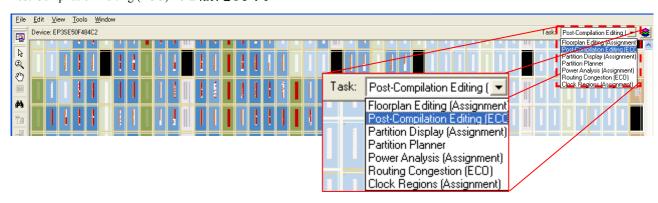

# 4-1. Chip Planner フロアプラン・ビュー

Chip Planner フロアプラン・ビューは、コンパイル後のデバイス内部の配置配線を視覚的に確認できるため、デザインの解析を行う上で役立ちます。また、 Chip Planner では、Chip Planner 上の Task メニューより、以下のモードが選択でき、本項では、Post-Compilation Editing (ECO) のご紹介をします。

※ Task の項目内容はデバイスにより異なります。

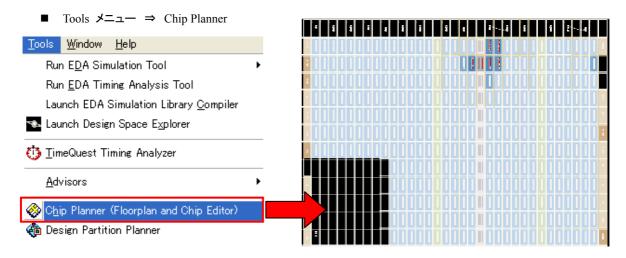

## 4-1-1. 起動方法

スタンダードな Chip Planner の起動方法は以下の手順です。

ターゲット・デバイスの抽象化レベルを示す階層ズーム・ビューワにおいて、ズーム・ツール (Chip Planner ツール・バー内)などを用いてズーム・レベルを上げると、抽象化レベルが下がりデバイス内部がより詳細に表示されます。

ver.9.0 2009 年 8 月 Page 3 of 23 Altima Corporation

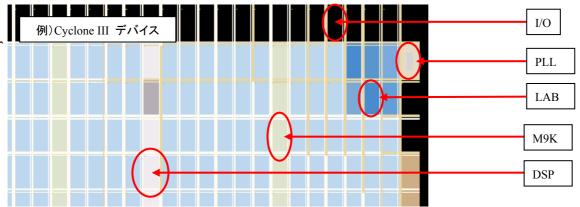

### ▶ ズーム・レベル 1

レベル1は、デバイス内部全体を表示します。各リソースは色別で表示され、リソースの使用率が高くなるほど色が濃くなります。(例: LAB で LE の使用が増えると、LAB の色が濃くなります。)

マウスのポインタをリソース上に置くと、高いレベルでのリソースの使用情報がツール・チップにより表示されます。

また、マウスのポインタをリソース上に置くと、高いレベルでのリソースの使用情報がツール・チップにより表示されます。

#### ▶ ズーム・レベル 2

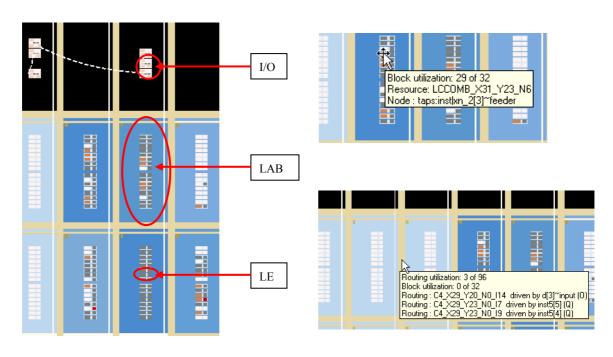

レベル1をズーム・アップすると、さらに詳細な内部情報が表示され、LABとI/O バンクの内容、およびリソース間の配線チャネルが確認できます。

マウスのポインタをリソース上に置くと、LE 名、LE の位置およびその LAB におけるリソースの使用情報がツール・チップにより表示されます。また、インターコネクト上にポインタを置くと、使用されているインターコネクトの配線チャネルを示します。

## ▶ ズーム・レベル3

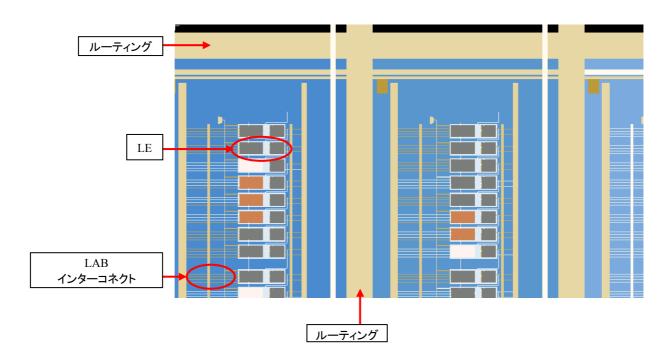

レベル2をズーム・アップすると、さらに詳細な内部情報が表示され、FPGA の LAB で使用される各配線リソースが確認できます。

### 4-1-2. クロス・プロービングによる起動方法

Chip Planner は、Quartus II の様々なクロス・プロービングにより、リンク起動させることができます。

以下に主な起動方法を例として示します。

- プロジェクト・ナビゲータからのリンク起動

- TimeQuest からのリンク起動

- コンパイラ・レポート(Timing Analyzer レポート)からのリンク起動

- ノード・ファインダからのリンク起動

- RTL ビューワからのリンク起動

- Pin Planner からのリンク起動

これらの中でクロス・プロービングによる Chip Planner の起動方法の代表的な例を2つご紹介します。

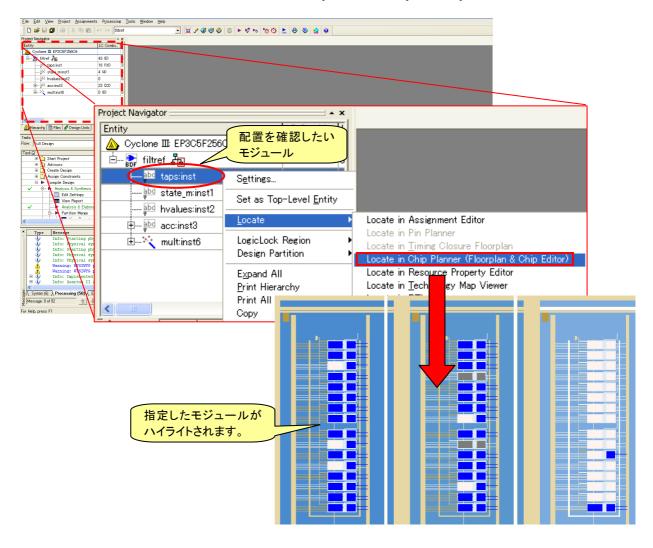

■ プロジェクト・ナビゲータからのリンク起動

特定のモジュールごとに配置状況を確認したい場合などに便利な機能です。

- 1. プロジェクト・ナビゲータ内のあるモジュールを右クリックで選択します、

- 2. プルダウン・リストより Locate ⇒ Locate in Chip Planner (Floorplan & Chip Editor) を指定します。

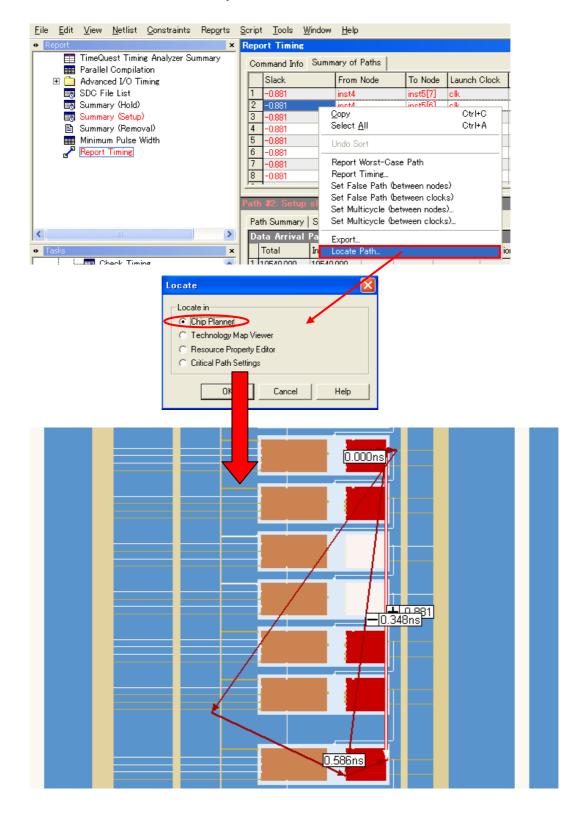

■ TimeQuest からのリンク起動

タイミング検証において、特定のパスの配置情報(遅延情報)を視覚的に確認したい場合などに便利な機能です。

- 1. 確認したい情報を右クリックで選択します。

- 2. プルダウン・リストより Locate Path... を選択します。

- 3. Locate ダイアログ・ボックスより Chip Planner を選択し OK ボタンをクリックします。

### 4-2. クリティカル・パス設定

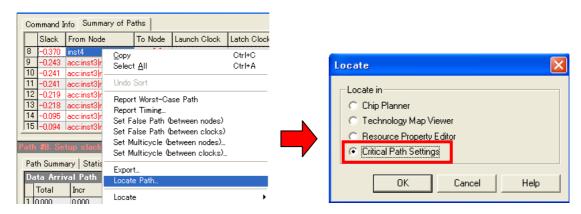

Chip Planner 上でクリティカル・パスを表示させるとき、先述のようにタイミング・レポート(TimeQuest レポート、または Classic Timing Analyzer レポート)からクロス・プロービングにより視覚的に確認する方法の他に、Chip Planner 上でクリティカル・パスに条件を設定して表示させる方法があります。

なおこの機能を使用する場合には、事前に TimeQuest または Classic Timing Analyzer にてクロックや各タイミングに対する要求値を設定していること、またコンパイルを実行している必要があります。TimeQuest でタイミング解析している場合には、さらにコンパイル後に TimeQuest でタイミング解析(レポート生成)を実行しておかねばなりません。その際 TimeQuest は起動したままにしてください。

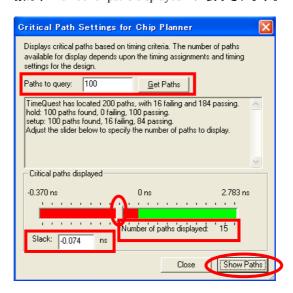

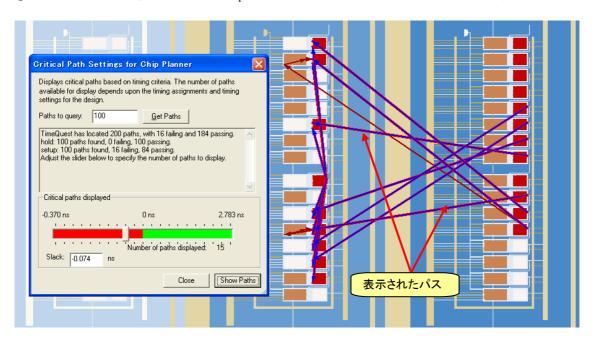

#### 4-2-1. TimeQuest Timing Analyzer の場合

※ TimeQuest でタイミングを解析した後に行ってください。

- ① Chip Planner を起動します。

- ② View メニュー ⇒ Critical Path Settings またはツール・バー内の 🗗 ボタンをクリックします。

もしくは TimeQuest のレポート上から情報を選び、右クリック ⇒ Locate Path ⇒ Critical Path Settings を選択後 OK ボタンをクリックしても同様です。

- ③ Critical Path Settings for Chip Planner ダイアログ・ボックスが起動します。Paths to query 欄に照合するパス数を入力し、Get Paths ボタンをクリックします。

- ④ Critical Path displayed 欄にて、バーを左または右へ移動させるか Slack 欄にスラック値を指定し、表示させるパスを設定します。表示されるパス数は、"Number of paths displayed" に表示されます。

⑤ Show Paths ボタンをクリックすると、Chip Planner フロアプラン・ビューにクリティカル・パスが表示されます。

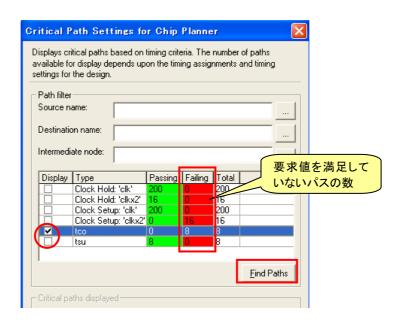

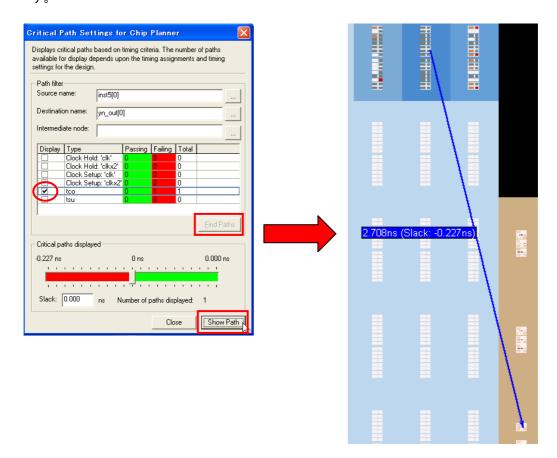

### 4-2-2. Classic Timing Analyzer の場合

### 4-2-2-1 全体指定

- ① Chip Planner を起動します。

- ② View メニュー ⇒ Critical Path Settings またはツール・バー内の 🗗 ボタンをクリックします。

- ③ Critical Path Settings for Chip Planner ダイアログ・ボックスにクリティカル・パスの一覧が検出されます。

- ④ 表示させたい項目にチェックを入れ、Find Paths ボタンをクリックします。

ver.9.0 2009 年 8 月 Page 9 of 23 Altima Corporation

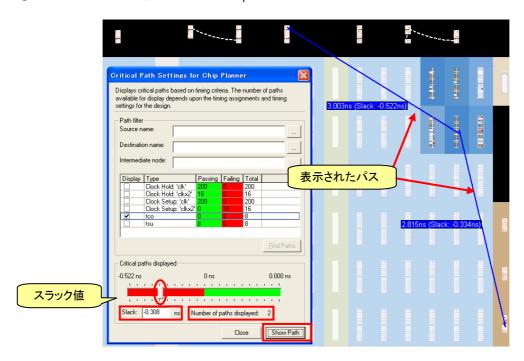

- ⑤ Critical Path displayed 欄にて、バーを左または右へ移動させるか Slack 欄にスラック値を指定し、表示させるパスを設定します。表示されるパス数は、"Number of paths displayed"に表示されます。

- ⑥ Show Paths ボタンをクリックすると、Chip Planner フロアプラン・ビューにクリティカル・パスが表示されます。

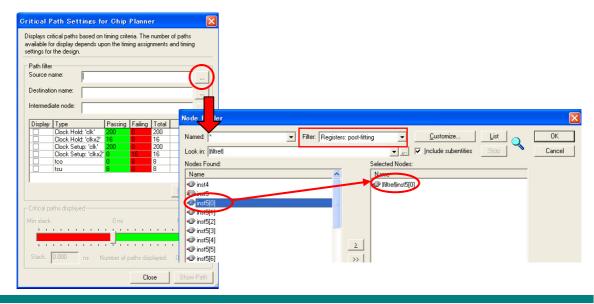

## 4-2-2-2 個別指定

- ① Chi Planner を起動します。

- ② View メニュー ⇒ Critical Path Settings またはツール・バー内の pt ボタンをクリック。

- ③ Critical Path Settings for Chip Planner ダイアログ・ボックスにクリティカル・パスが検出されます。

- ④ Path Filter 欄の Source name に、Node Finder を使用してノード名を入力します。

- 1) Filter リストより、ノードを選出しやすい項目を選択します。

- 2) List ボタンをクリックします。

- 3) Nodes Found (左枠)よりノードをダブル・クリックで指定し、Selected Nodes (右枠)へ移行させます。

ver.9.0 2009 年 8 月 Page 10 of 23 Altima Corporation

- 4) OK ボタンをクリックします。

- ⑤ 同様に、Destination name に Node Finder を使用してノード名を入力します。(必要に応じて Intermediate node も 指定します。)

- ⑥ Find Paths ボタンをクリックし、情報を表示させます。

- ⑦ 見たいパスの "Display"欄に を入れ、再び Find Paths ボタンをクリックします。

- ⑧ Show Paths ボタンをクリックすると、Chip Planner フロアプラン・ビューに指定したクリティカル・パスが表示されます。

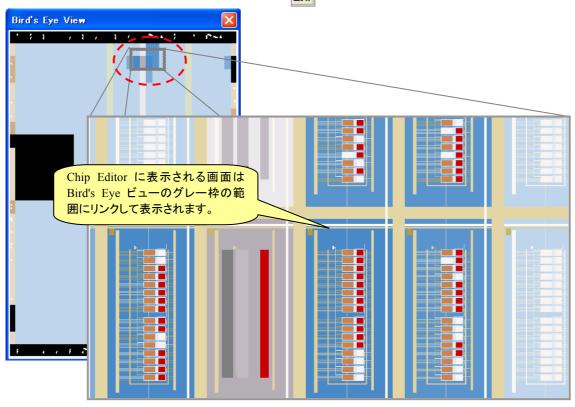

## 4-3. Bird's Eye ビュー

Bird's Eye ビューは、デバイス全体のリソース使用の状況を画像で表示し、Chip Planner 内を効率的にナビゲートするウィンドウです。Bird's Eye ビュー内のエリアを選択すると、Chip Planner フロアプランも自動的にリンクし、デバイス内の指定されたエリアを拡大表示します。 Chip Planner フロアプラン・ウィンドウをズーム・イン(ズーム・アウト)することで、Bird's Eye ビューの指定範囲枠を小さく(大きく)することができ、より詳細な情報が得られます。起動方法は以下のとおりです。

■ View メニュー ⇒ Bird's Eye View を選択、または 🍇 ボタンをクリック

また、Layers Settings (View メニュー または Chip Planner 画面の右上の **w** ボタン) により、Bird's Eye View で示される詳細をカスタマイズすることができます。

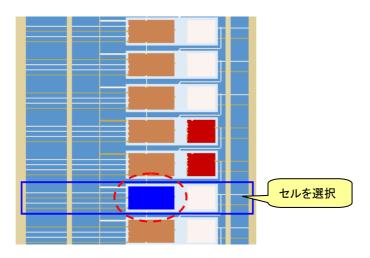

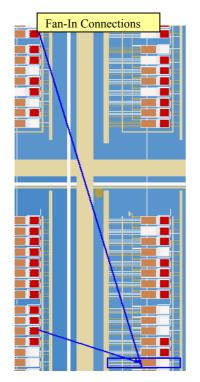

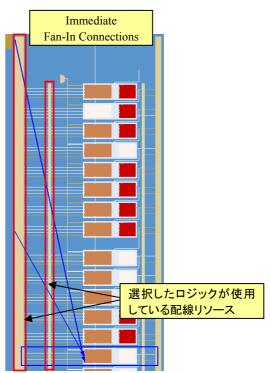

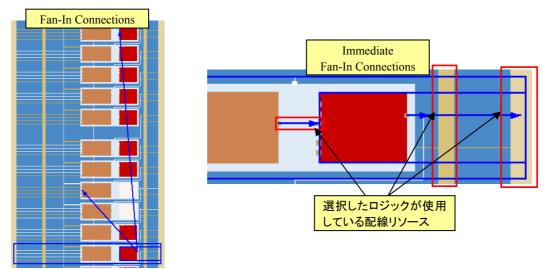

## 4-4. Fan-In/Fan-Out の表示

指定したロジックの Fan-In および Fan-Out を表示することができます。2 通りの表示方法があり、ひとつは、指定ロジック 下an-In するロジック(または指定ロジックから Fan-Out するロジック) を確認することができます。もうひとつは、選択したロジックの Fan-In および Fan-Out において、配線リソースを含めた状態で接続を表示できます(Immediate モード)。

■ Fan-In の表示

View メニュー ⇒ Generate Fan-In Connections またはツール・バー内の 📲 ボタンをクリックします。

■ Immediate Fan-In の表示

View メニュー ⇒ Generate Immediate Fan-In Connections をクリックします。

■ Fan-Out の表示

View メニュー ⇒ Generate Fan-Out Connections またはツール・バー内の **ド** ボタンをクリックします。

■ Immediate Fan-Out の表示 View メニュー ⇒ Generate Immediate Fan-Out Connections をクリックします。

イクエーション・ボタン x=b をクリックすると、選択したロジックとその接続先(Fan-In/Fan-Out)の情報が確認できます。 Fan-In、Fan-Out の表示を消したい場合は、View メニュー ⇒ Clear Unselected Connection/Paths またはツール・バー内の ネタンをクリックします。

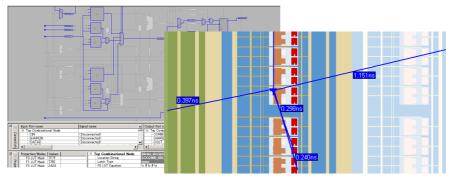

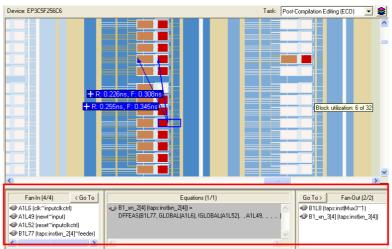

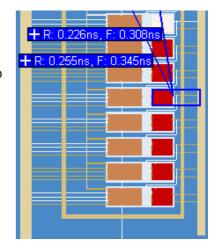

## 4-5. 遅延の表示

指定されたリソース間のタイミング遅延を表示できます。

セルを選択し、View メニュー ⇒ Show Delays またはツール・バー内の ボタンをクリックします。

# 5. <u>デザイン変更</u>

Chip Planner においてデザイン変更を行うためには、コンパイルが終了していることが条件になります。コンパイルを実行していない場合は、以下のフローでコンパイルを行ってください。

- Processing メニュー ⇒ Start Compilation または ▶ ボタンをクリック

※ Chip Planner を使用して配置やプロパティを変更する場合は、デバイスのアーキテクチャに関する知識を要します。

## 5-1. レイアウトの変更

Chip Planner フロアプランは、既存のロジック・エレメントや I/O のレイアウト(物理的配置)を変更することが可能です。

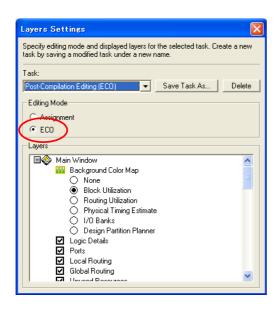

- ① View メニュー ⇒ Layers Settings または Chip Planner ウィンドウの右上の **参** ボタンにて、Layers Settings ダイア ログ・ボックスを起動します。

- ② Editing Mode において ECO を選択します。

③ レイアウトを移動させたいロジックを選択し、新しい配置先へドラッグ&ドロップで移動させます。

## ALTIMA

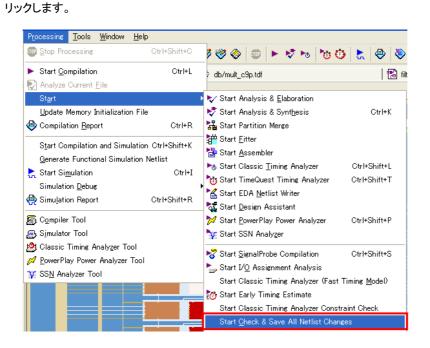

④ 変更内容に問題がないかどうかを確認するため、デザイン・ルールのチェックを行います。

Processing メニュー ⇒ Start Check & Save All Netlist Changes またはツール・バー内の ボタンをク

⑤ "ECO Fitting was successful" メッセージが表示されたら OK ボタンをクリックします。同時に、Chip Planner フロアプランで編集した後のプログラミング・ファイルが生成されます。

#### 5-2. リソースの変更

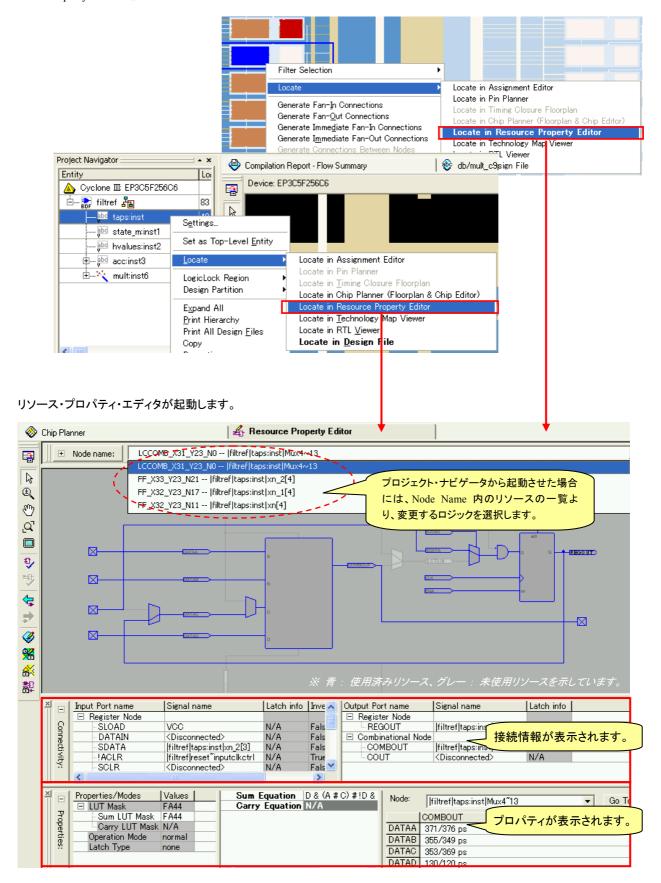

リソース・プロパティ・エディタを使用して、任意の LE 、ALM、I/O リソース、PLL を表示およびプロパティの変更をすることができます。特定のデバイス・ファミリのアーキテクチャについては、各デバイス・ファミリ・ハンドブックをご覧ください。

ここでは図例として、Cyclone III デバイスの LE を掲載しています。

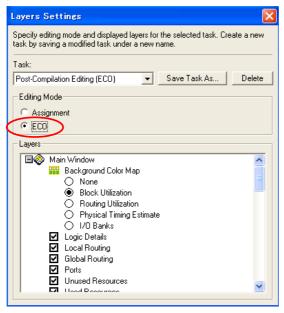

- ① View メニュー ⇒ Layers Settings または Chip Planner ウィンドウの右上の **参** ボタンにて、Layers Settings ダイア ログ・ボックスを起動します。

- ② Editing Mode において ECO を選択します。

③ プロパティを変更したいロジックを右クリックで選択し、Locate ⇒ Locate in Resource Property Editor またはダブル・クリックします。または、プロジェクト・ナビゲータからモジュールを右クリックで選択し、Locate ⇒ Locate in Resource Property Editor を指定すると、リソース・プロパティ・エディタが起動します。

- ④ 変更したい項目を、スケマティック・ビューまたはプロパティ・ウィンドウやコネクティビティ・ウィンドウから選択し、変更します。(下記 5-2-1.節 に変更例を掲載します。ご参考ください。)

- ⑤ Edit メニュー ⇒ Check Resource Properties またはツール・バー内の ジボタンをクリックし、変更内容の簡易チェックをします。

- ⑥ Edit メニュー ⇒ Check & Save All Netlist Changes またはツール・バー内の デザイン・ルールをチェックします。

- ⑦ フィッティングとアセンブラが実行され、"ECO Fitting was successful" メッセージが表示されたら OK ボタンをクリックします。同時に、リソース・プロパティ・エディタで編集した後のプログラミング・ファイルが生成されます。

(その後、Quartus II の TimeQuest タイミング・アナライザでタイミング解析を実行、およびタイミング・シミュレーションを行います。 ⇒ 本紙「第6章 ECO操作後の実行」をご覧ください。)

#### 5-2-1. リソースの変更例

以下に、リソースの変更例をいくつかご紹介します。変更後は、5-2.節⑤以降の操作を行ってください。

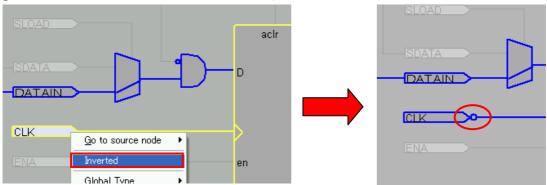

- クロック信号にインバータ(反転)を挿入する場合

- ① スケマティック・ビューにおいて、クロック・ポート(CLK)を選択します。

- ② 右クリック ⇒ プルダウン・メニュー ⇒ Inverted を指定します。

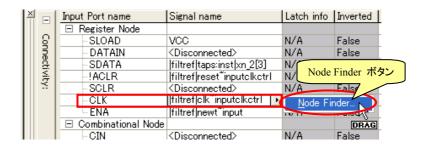

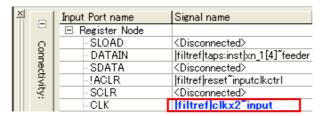

- クロック・ノードに別のノードを接続しなおす場合

- ① スケマティック・ビューにおいて、クロック・ポート(CLK)を選択します。

- ② 右クリック ⇒ プルダウン・メニュー ⇒ Edit Connection ⇒ Other を指定します。

- ③ Edit Connection ウィンドウの Signal name 欄において、Node Finder ボタンをクリックします。

または下記の図のように、コネクティビティ・ウィンドウにおいて、クロック・ポート(CLK)の Signal name をダブル・クリックし、Node Finder を起動させます。

- ④ Node Finder を使用して、接続したいノード名を選択します。

- 1) Filter リストより、ノードを選出しやすい項目を選択します。

- 2) List ボタンをクリックします。

- 3) Nodes Found (左枠)よりノードをダブル・クリックで指定し、Selected Nodes (右枠)へ移行させます。

- 4) OK ボタンをクリックします。

⑤ コネクティビティ・ウィンドウにおいて、変更後のノード名が確認できます。

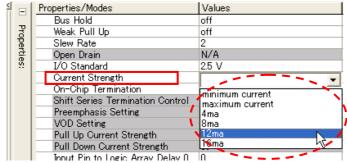

- 出力ピンの出力電流値(Current Strength)を変更する場合

- ① プロパティ・ウィンドウにおいて、Current Strength の Values 欄をダブル・クリックします。

- ② プルダウン・リストより、希望の電流値を選択します。

ver.9.0 2009 年 8 月 Page 19 of 23 Altima Corporation

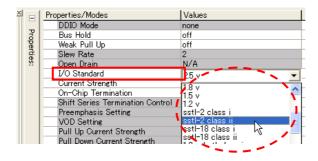

- I/O 規格を変更する場合

- ① プロパティ・ウィンドウにおいて、I/O Standard の Values 欄をダブル・クリックします。

- ② プルダウン・リストより、希望の I/O 規格を選択します。

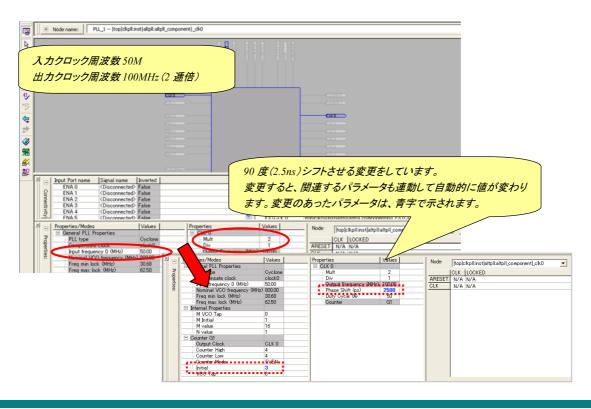

■ PLL の位相シフト調整をする場合

以下の等式を使用して、PLLの出力クロックの位相シフトを調整します。

位相シフト = (周期 VCO x 0.125 x Tap VCO) + (Initial VCO x 周期 VCO)

Normal モードの場合、以下の設定で位相シフトを計算します。

Tap VCO = カウンタ・ディレイ ー M Tap VCO

Initial VCO = カウンタ・イニシャル - M イニシャル

周期 VCO = イン・クロック周期 xN/M

詳細は、各デバイス・ファミリのハンドブックを参照してください。

- ① シフトさせる値を設定するため、各パラメータの値を等式より求めます。

- ② プロパティ・ウィンドウにおいて、変更する項目の Value 欄をダブル・クリックし、等式より求めた値を入力します。

※ 下図は、シフト値を 0 度 から 90 度 に変更した例を示しています。

## 5-3. デザイン変更の履歴

## 5-3-1. デザイン変更の履歴

Chip Planner フロアプランやリソース・プロパティ・エディタで変更した内容は、チェンジ・マネージャにより記録されます。チェンジ・マネージャの起動方法は以下のとおりです。

① View メニュー ⇒ Utility Windows ⇒ Change Manager を選択します。

| Index A | Node Name             | Change Type      | Old Value        | Target Value     | Current Value    | Disk Value       | Comment |

|---------|-----------------------|------------------|------------------|------------------|------------------|------------------|---------|

| 1       | yn out[0]             | Current Strength | 24mA             | 12mA             | 12mA             | 12mA             |         |

| 2       | acc:inst3 ynm[8]~103  | Location Index   | LCCOMB_X14_Y9_N2 | LCCOMB_X14_Y9_N4 | LCCOMB_X14_Y9_N4 | LCCOMB_X14_Y9_N4 |         |

| 3       | acc:inst3 result[8]_N | Location Index   | LCFF_X14_Y9_N3   | LCFF_X14_Y9_N5   | LOFF_X14_Y9_N5   | LOFF_X14_Y9_N5   |         |

## ② 変更履歴が表示されます。

各フィールドの説明は以下のとおりです。

| カラム名          | 説明                                                                    |  |  |

|---------------|-----------------------------------------------------------------------|--|--|

| Index         | Chip Planner または Resource Property Editor で行われる変更に対応する変               |  |  |

|               | 更記録を連続番号により識別します。変更記録が複雑な場合、インデックス・カ                                  |  |  |

|               | ラムは主な変更だけでなくコンポーネントの変更もすべて識別します。                                      |  |  |

| Node Name     | 変更が行われたリソースを個々に識別します。                                                 |  |  |

| Change Type   | Change Type リソースに行われた変更のタイプを識別します。                                    |  |  |

| Old Value     | Old Value 変更が行われる直前のリソースの値をリストします。                                    |  |  |

| Target Value  | Target Value Resource Property Editor、Chip Planner、または SignalProbe を使 |  |  |

|               | 用して、確立した希望のターゲット値(新しい値)をリストします。                                       |  |  |

| Current Value | メモリで現在アクティブなネットリストのリソースの値をリストします(ディスクに                                |  |  |

|               | 保存されたネットリストの値ではありません。変更を行ったが、まだ Check &                               |  |  |

|               | Save All Netlist Changes コマンドを使用していない場合、この値は異なること                     |  |  |

|               | があります)。                                                               |  |  |

| Disk Value    | ディスク上のリソースの現在の値をリストします。この値は、現在のフィッティン                                 |  |  |

|               | グ後のネットリストに取り込まれた変更を反映しています。                                           |  |  |

| Comment       | これで Change Manager で変更記録にコメントを追加できます。変更記録にコメ                          |  |  |

|               | ントを追加するには、注釈を付けたいレコードの Comment フィールドをダブル・                             |  |  |

|               | クリックして、希望のコメントを入力します。                                                 |  |  |

### 5-3-2. デザイン変更履歴のファイル生成

チェンジ・マネージャの情報を Tcl スクリプトや CSV ファイル、テキスト・ファイルにエクスポートすることができます。

- ① チェンジ・マネージャ上で右クリック ⇒ Export ⇒ Export All Changes As を選択します。

- ② 保存するフォルダ、ファイル名を入力し、ファイルの種類をプルダウン・リストより選択して、Export ボタンをクリックします。

# 6. ECO 操作後の実行

Chip Planner で変更を行った後は、以下の操作を行ってください。

### 6-1. タイミング検証

Chip Planner で変更を行った場合には、Quartus II の TimeQuest または Classic Timing Analyzer においてタイミング解析を行い、変更内容がデザインのタイミング性能に悪影響を与えていないことを確認してください。レイアウト変更以外の変更内容でも、タイミングに影響する場合があります。(例: I/O エレメントの遅延挿入など)

また同様に、Quartus II のシミュレータまたはEAD ベンダのシミュレータ・ツールでゲートレベルのタイミング・シミュレーションを実行し、動作確認を行ってください。

- ※ Classic Timing Analyzer については、アルティマ資料「Quartus II はじめてガイド タイミング制約の設定方法 (Classic Timing Analyzer)をご参照ください。

- ※ TimeQuest については、アルティマ資料「Quartus II TimeQuest クイック・ガイド」をご参照ください。

## 6-2. プログラミング・ファイルの生成

タイミング解析およびシミュレーションを実行し、変更内容がデザインの要件を満足していると判断できた場合には、先に行った Check & Save All Netlist Changes (Edit メニュー)にて生成されたプログラミング・ファイルを使用します。別途アセンブラを単独 で実行する場合は、以下のメニューより操作可能です。

- Processing メニュー ⇒ Start → Start Assembler

#### 6-3. 注意点

ECO での変更内容は、デザイン・ファイルやオプション設定には<u>一切反映されません</u>。そのため、Change Manager (本紙 5-3 節)での管理を徹底してください。 また、ECO 変更後に再コンパイルを実行してしまうと、ECO の変更内容は全て無視された状態でコンパイルが実行されます。ご注意ください。

ver.9.0 2009 年 8 月 Page 22 of 23 Altima Corporation

弊社より資料を入手されましたお客様におかれましては、下記の使用上の注意を一読いただいた上でご使用ください。

- 1. 本資料は非売品です。許可無く転売することや無断複製することを禁じます。

- 2. 本資料は予告なく変更することがあります。

- 3. 本資料の作成には万全を期していますが、万一ご不明な点や誤り、記載漏れなどお気づきの点がありましたら、弊社までご一報いただければ幸いです。

- 4. 本資料で取り扱っている回路、技術、プログラムに関して運用した結果の影響については、責任を負いかねますのであらかじめご了承ください。

- 5. 本資料は製品を利用する際の補助的な資料です。製品をご使用になる場合は、英語版の資料もあわせてご利用ください。

#### 横浜本社

〒222-8563 横浜市港区新横浜 1-5-5 マクニカ第二ビル TEL 045-476-2155 FAX 045-476-2156 大阪営業所

〒532-0003 大阪市淀川区宮原 3-4-30 ニッセイ新大阪ビル 17 階 TEL 06-6397-1053 FAX 06-6397-1054 名古屋営業所

〒460-0003 名古屋市中区錦 1-6-5 名古屋錦シティビル 7 階 TEL 052-202-1024 FAX 052-202-1025 宇都宮営業所

〒321-0953 宇都宮市東宿郷 4-2-24 センターズビル 7 階 TEL 028-637-4488 FAX 028-637-4489