## タイミング & インプリメンテーション デザイン・デバッグ ガイドライン

2018年12月 株式会社マクニカ アルティマカンパニー

Rev.1

## アジェンダ

- ・はじめに

- 本資料の目的

- チェックリスト

- チェックポイント

- チェックフロー

- タイミングで確認すべき項目

- 回路設計で気をつけるポイント

- クロック信号の確認

- ○電源電圧の確認

- 不具合事例

## はじめに

### 本資料の目的

インテル® FPGA では、設計ソフトウェア(インテル® Quartus® Prime)上でのコンパイル(論理合成、配置、配線)工程を経て、FPGA 内の物理リソースを設定・接続するデータを作成し、そのコンパイルデータを FPGA 内にダウンロードすることで所要の機能をハードウェアとして実現します。

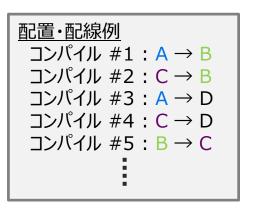

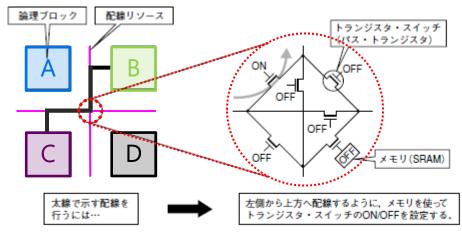

インテル® Quartus® Prime は、ユーザーの設定条件(動作周波数のようなタイミング制約等)を守るようにコンパイルを実行します。コンパイルでは、FPGA 内の固定された位置にある膨大な数のリソース(LUT、フリップフロップ(FF)、メモリー、DSP 等)を更に膨大な数の配線用の交差点トランジスター・スイッチ(パス・トランジスター)の On/Off によって接続します。

インテル® Quartus® Prime では、ユーザーデザイン(RTL や 回路図)が変更されない場合であっても、この配置や配線はコンパイル毎に変化します(場合によっては、論理合成結果も)。

また、半導体には、プロセス(P)、電源電圧(V)、温度(T) ばらつきがあり、この条件を加味したタイミングモデルを用いて、ユーザーが設定したタイミング制約に基づくタイミング解析が行われます。

正常な動作を保証するためには、適正な動作環境下で、適切に設定されたタイミング制約を守っている必要があります。

〔図2〕トランジスタ・スイッチを使った配線経路の設定

FET のゲート電極に与える制御信号でオン/オフを決める。制御信号はメモリ(SRAM)に蓄えてある。

引用: Design Wave Magazine, 1999年12月号

#### 本資料の目的 Cont.

- 一方で、実際に FPGA にコンパイルデータをダウンロードして動作させた場合、以下のような事象が発生する場合があります。

- ・ユーザーデザインを変更していない場合であっても、コンパイル毎に不具合動作・頻度・発生の有無が異なる

- ・調査のために Signal Tap を挿入すると、不具合現象が再現しなくなる

- ・FPGA の個体により不具合動作・頻度・発生の有無が異なる(P)

- ・電源電圧を変化させると不具合動作・頻度・発生の有無が異なる(V)

- ・温度が変化すると不具合動作・頻度・発生の有無が異なる(ある時間、動作させていると不具合動作が発生するようになる)(T)

- ・ある時点から(ある**製品ロット**から)不具合動作が発生するようになる(P)

- ・対向デバイスを交換すると事象が変化する

このような現象は、経験的に約 80% の割合で、下記のような原因の複合で発生することが確認されています。

・適切にタイミング制約が設定されていない

例:タイミング制約の漏れや上書き、False 設定による無効化

・信号間の到達時間差(どれかが早い、遅い、同時)に対して、その時間差を考慮した回路構成となっていない

例:非同期リセット、非同期信号の分配

・タイミング制約およびタイミングモデルで規定した条件外での使用

例:PVT条件や入力ジッター条件を満たしていない、もしくはギリギリ

本資料では、タイミング制約の生成方法や不具合が発生しにくい回路構成を示すとともに、不具合発生時のデバッグ手順を示します。 対象デバイスは インテル® Stratix® 10, Arria® 10, Cyclone® 10 をはじめとした、インテル® FPGA デバイスすべてを対象としています。

## チェックリスト

#### ◆タイミング

| タイミング検証を行いタイミングエラーがないことを確認し解析結果 (*.rpt) をエビデンスとして残しているか |                                     |

|---------------------------------------------------------|-------------------------------------|

| 仕様通りの制約で SDC ファイルを作成したか                                 |                                     |

| False Path の制約を正しい箇所にのみ設定しているか                          |                                     |

| 未制約のパス、無視されている制約はないか                                    |                                     |

| SDC ファイルが複数ある場合は、正しい順番で インテル® Quartus® Prime に登録を行ったか   |                                     |

| ◆回路                                                     |                                     |

| グリッチのケアを行っているか                                          |                                     |

| 非同期クロック間の信号の受け渡しに組み合わせ回路を使用していないか                       |                                     |

| 非同期となるレーシング回路の対策を行っているか                                 |                                     |

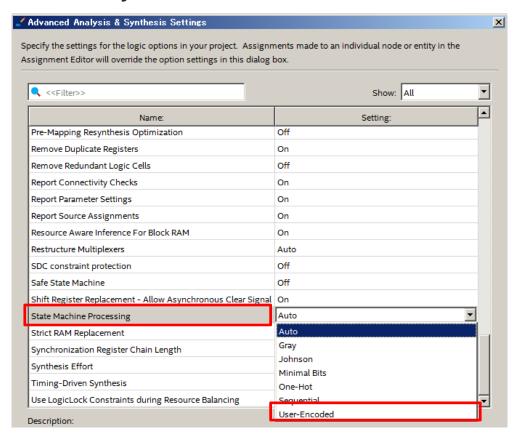

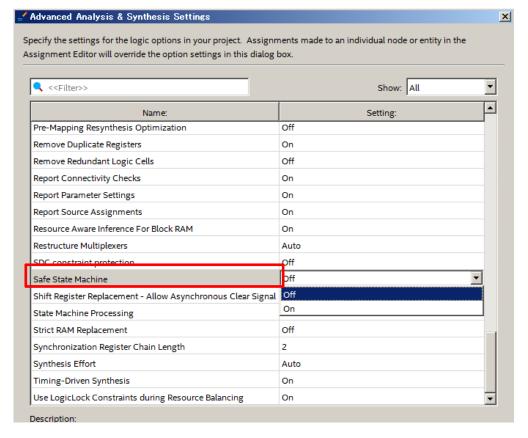

| インテル® Quartus® Prime でステートマシンの設定を "User Encoded" にしているか |                                     |

| リセット信号のリセット解除タイミングを考慮しているか                              |                                     |

| ◆クロック                                                   |                                     |

| 入力クロック信号の I/O 設定は正しいか                                   |                                     |

| FPGA コア・ファブリック側のクロック供給は外部から行っているか                       |                                     |

| ◆電源                                                     |                                     |

| 電源電圧はスペック内に収まっているか(過渡負荷時、同時スイッチング時)                     | A LTIMA  A Macrica Division Company |

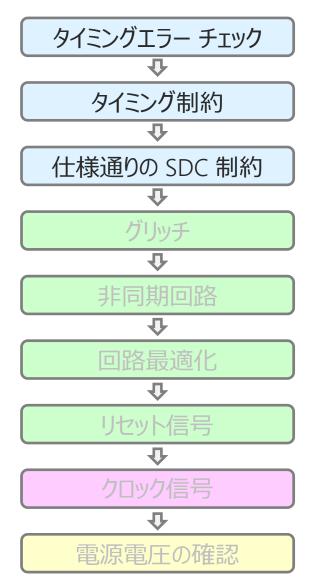

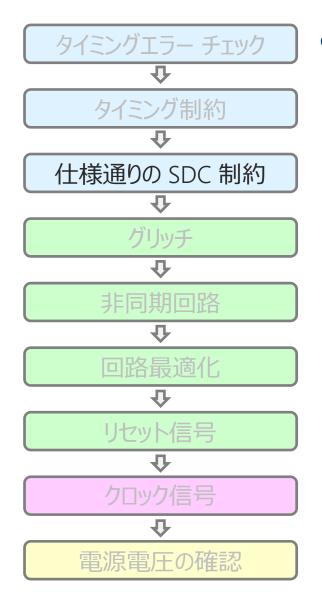

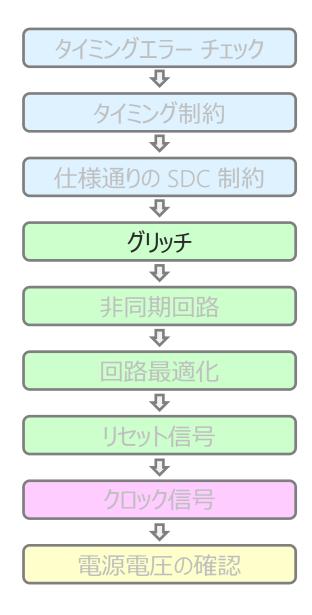

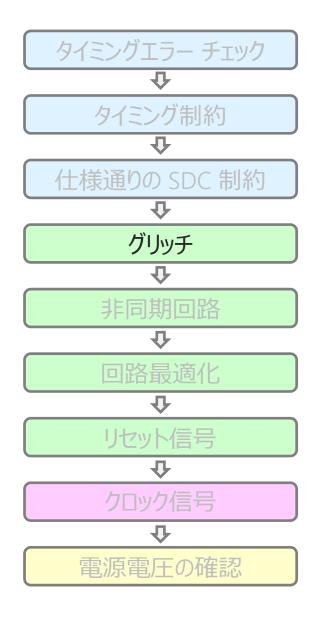

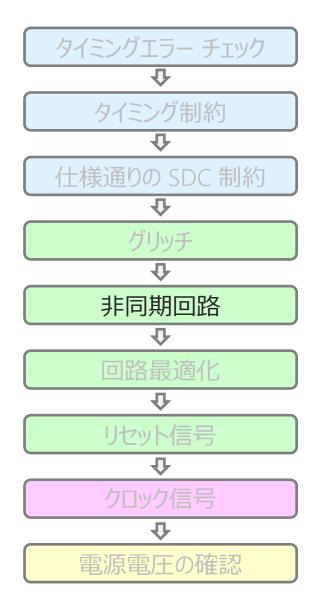

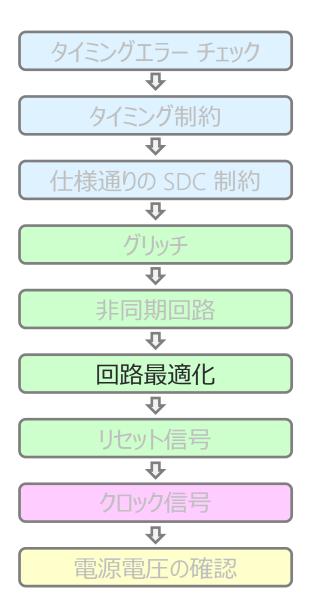

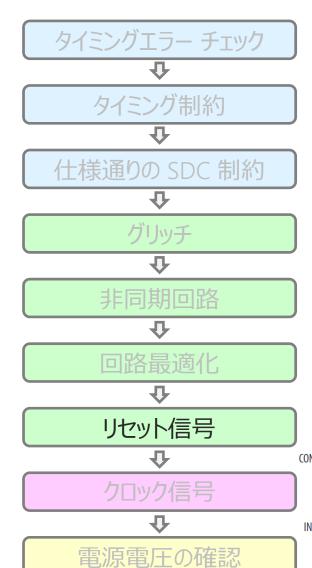

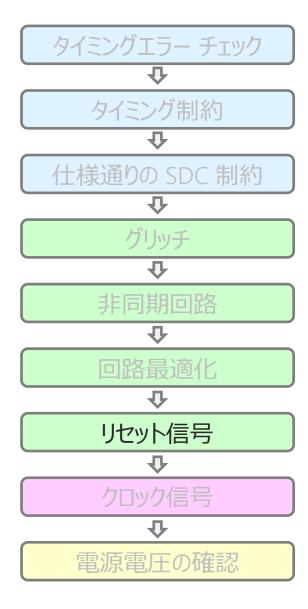

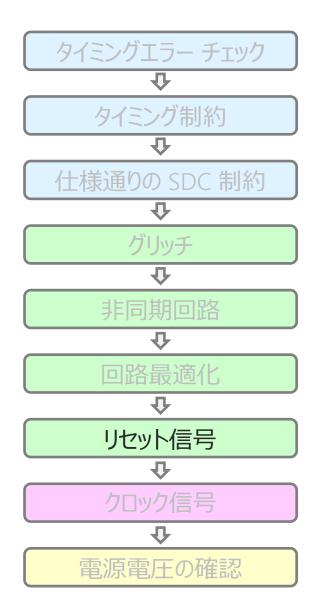

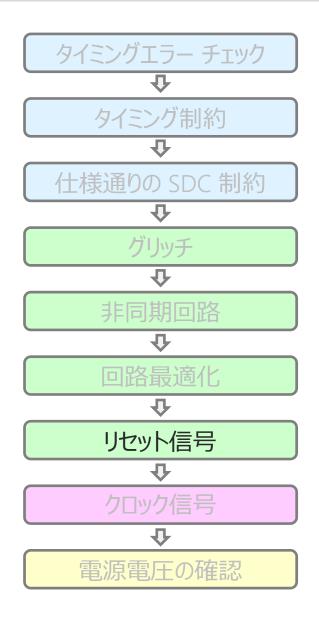

## チェックポイント

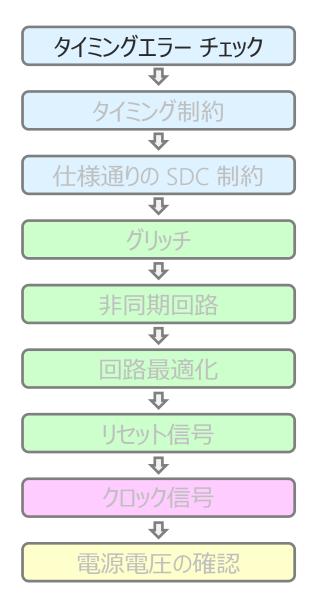

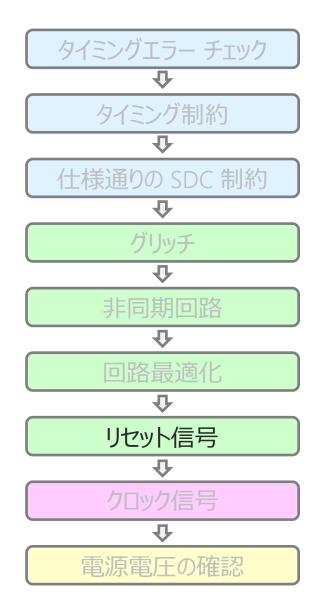

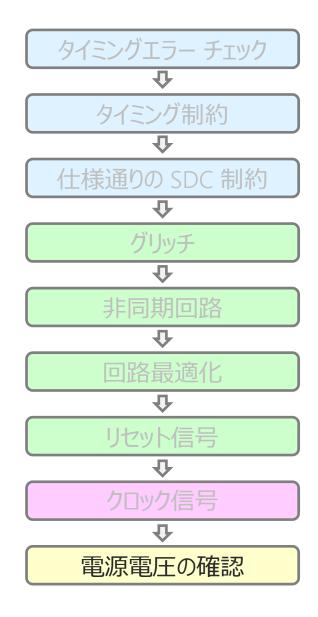

①タイミング関連の確認

②デザインの確認

③クロック信号の確認

タイミングエラー

タイミング制約

仕様通りの SDC 制約

グリッチ

非同期回路

回路最適化

リセット信号

クロック信号

4電源電圧の確認

電源電圧の確認

## タイミングで確認すべき項目

## インプリメンテーション・ガイドライン – タイミング –

#### • タイミングでケアすること

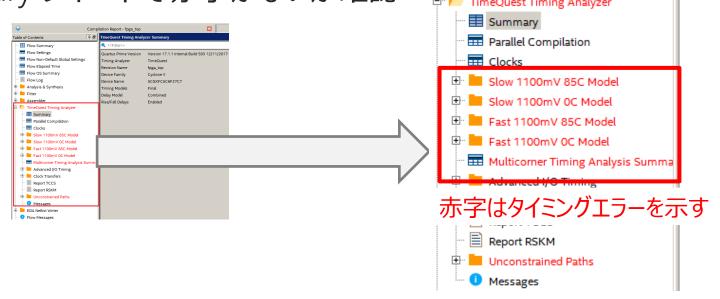

- O Timing Analyzer Summary のレポートで赤字がないか

- インテル® Quartus® Prime のコンパイルレポートから確認

- レポートを残しているか (Appendix 1-1. 参照)

- タイミング・アナライザーでのレポート確認

- 未制約のパス (Unconstrained Paths) はないか

- 作成した SDC が反映されているか

- 無視されている制約はないか

- 必要な箇所にのみ False path の制約をかけているか

- クロック系統図は作成しているか

- 外部 AC スペックの確認は行ったか

- 仕様通りの SDC ファイルとなっているか

- o SDC ファイルがインテル® Quartus® Prime のプロジェクトに登録されているか

## タイミングエラー チェック

タイミングエラー チェック タイミング制約 仕様通りの SDC 制約 グリッチ 非同期回路 回路最適化 リセット信号 クロック信号 電源電圧の確認

インテル® Quartus® Prime でのコンパイル後、Timing Analyzer Summary レポートで赤字がないか確認

- Timing Analyzer Summary レポートで赤字となっていた場合

タイミング収束を行い、赤字をなくす

- Timing Optimization Advisor を活用(Appendix 7. 参照)

- タイミングを収束させても状況が改善しない場合

- SDC の制約に誤りがないか、仕様通りの SDC を与えているか確認

## タイミング・アナライザーでのレポート確認

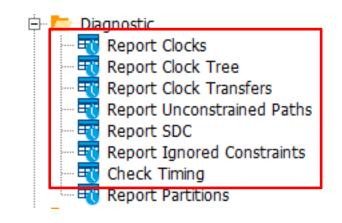

- 作成した SDC に問題がないかを確認

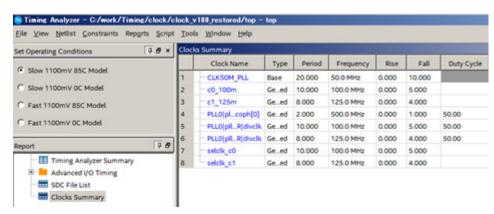

- Report Clocks

- 定義したクロック制約が正しく反映されているか

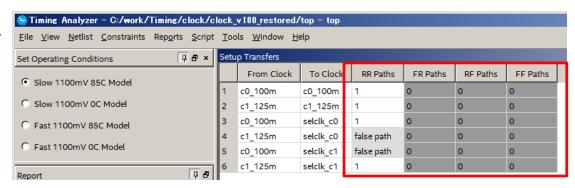

- Report Clock Transfers

- 解析対象外のクロック間パスがレポートされているか

- Report Unconstrained Paths

- 未制約のパスはないか

- Report SDC

- 作成した SDC は反映されているか

- Report Ignored Constraints

- 無視されている制約(コマンドはないか)

- Check Timing

- 制約の妥当性を確認

- 回路と制約の潜在的な問題を確認

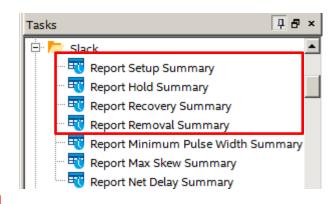

- タイミング要求を満たしているか確認

- Setup/Hold/Recovery/Removal

- 適切な箇所「のみ」に False Path 設定を行っているか (Appendix 2-4. 参照)

※赤字で示したレポートは与えた SDC が妥当か必ず確認する項目

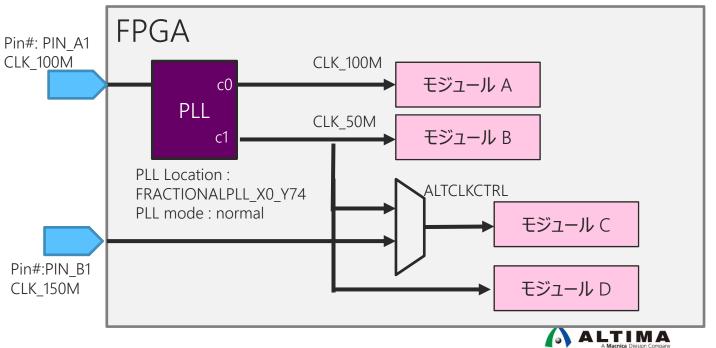

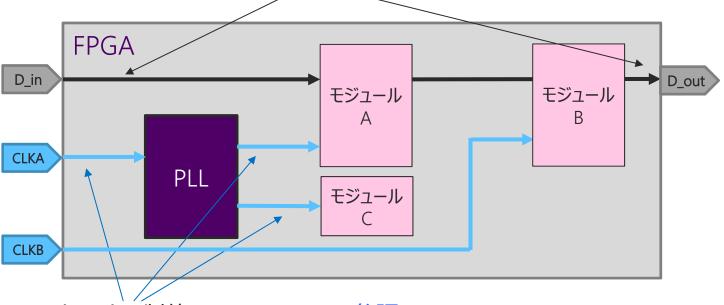

## クロック信号系統図の確認:ブロック図での確認

- 設計者が FPGA 内部で使用しているクロックの種類を認識するため クロック信号系統図を作成

- クロック系統図作成例はこちらを参照 ⇒ (ロック系統図)

- PLL Location, PLL mode 等は Fitter report で確認

- Appendix 5. 参照

#### クロック系統図 例)

## クロック信号系統図の確認:タイミング・アナライザー使用

タイミング・アナライザーの Report Clock Tree を使用することで FPGA 内部のクロックツリーを確認

タイミング・アナライザーのレポートと設計者が作成したクロックツリーに 相違がない事を確認

| Cloc | ock Summary Tree                                                      |           |        |           |       |        |            |           |     |

|------|-----------------------------------------------------------------------|-----------|--------|-----------|-------|--------|------------|-----------|-----|

|      | Clock Name                                                            | Туре      | Period | Frequency | Rise  | Fall   | Duty Cycle | Divide by | Mul |

| 1    | Ġ- CLK50M_PLL                                                         | Base      | 20.000 | 50.0 MHz  | 0.000 | 10.000 |            |           |     |

| 1    | - PLL0 pll0_inst altera_pll_i general[0].gpll~FRACTIONAL_PLL vcoph[0] | Generated | 2.000  | 500.0 MHz | 0.000 | 1.000  | 50.00      | 2         | 20  |

| 1    | PLL0 pll0_inst altera_pll_i general[0].gpll~PLL_OUTPUT_COUNTER divclk | Generated | 10.000 | 100.0 MHz | 0.000 | 5.000  | 50.00      | 5         | 1   |

| 1    | ⊟- c0_100m                                                            | Generated | 10.000 | 100.0 MHz | 0.000 | 5.000  |            | 1         | 1   |

| 1    | selclk_c0                                                             | Generated | 10.000 | 100.0 MHz | 0.000 | 5.000  |            | 1         | 1   |

| 2    | PLL0 pll0_inst altera_pll_i general[1].gpll~PLL_OUTPUT_COUNTER divclk | Generated | 8.000  | 125.0 MHz | 0.000 | 4.000  | 50.00      | 4         | 1   |

| 1    | ⊟ c1_125m                                                             | Generated | 8.000  | 125.0 MHz | 0.000 | 4.000  |            | 1         | 1   |

| 1    | selclk_c1                                                             | Generated | 8.000  | 125.0 MHz | 0.000 | 4.000  |            | 1         | 1   |

□ ₽ ×

Report DDR

Report Clock Tree

Report Metastability Summary

Report Unconstrained Paths

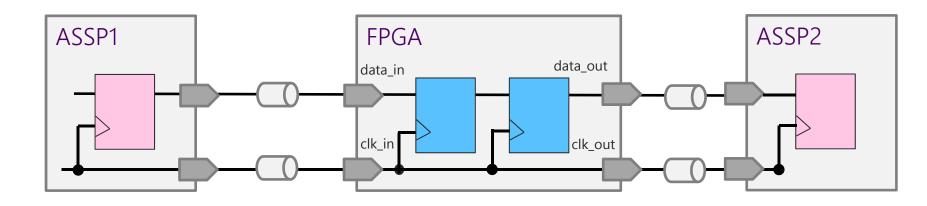

### 外部 AC スペックの確認

- FPGA 外部との AC スペックを定義するため、基板及び外部デバイスの情報が必要なため予め確認

- 外部デバイスの Setup / Hold の値

- 外部デバイスの Tco (min/max) の値

- 外部デバイス ⇔ FPGA の PCB 配線遅延値

- PCB クロックスキューの値

- 入力クロックのジッター

#### SDC 設定

各設定内容を確認

入力ピン、出力ピンの制約 (Appendix 2-5. 参照)/ ~ False path の制約 (<u>Appendix 2-3. 参照</u>) Multi-cycle path の制約 (<u>Appendix 2-6. 参照</u>)

クロックの制約 (Appendix 2-1. 参照)

クロックグループの制約 (Appendix 2-2. 参照)

FPGA 内部のクロックのバラつきの制約 (Appendix 2-1. 参照)

#### SDC を使ったタイミング制約

http://monoist.atmarkit.co.jp/mn/articles/0811/28/news136.html

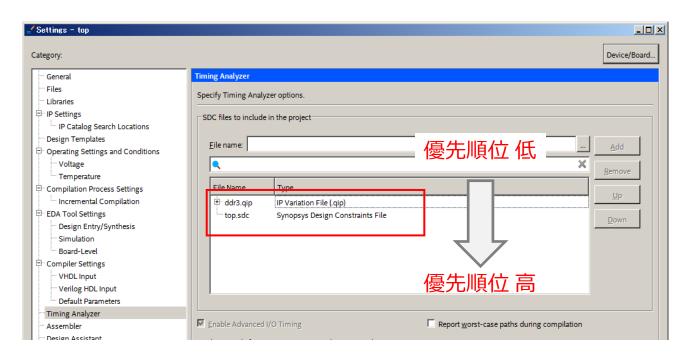

#### SDC の登録

- インテル® Quartus® Prime のプロジェクトに SDC を登録

- 作成した SDC が登録されているか確認

- Assignments -> Settings -> Timing Analyzer

- 複数の SDC を登録している場合、下に登録している SDC が優先順位が高い

- ユーザーで作成した SDC は一番下に登録すること

## 回路で気をつけるポイント

## 回路で気をつけるポイント

# タイミングエラー チェック タイミング制約 仕様通りの SDC 制約 グリッチ 非同期回路 回路最適化 リセット信号 クロック信号 電源電圧の確認

- グリッチ

- ゲートクロック

- クロックセレクト

- FPGA の入出力処理

- 非同期回路

- 非同期の受け渡しに組み合わせ回路を使用

- 非同期レーシングのケア

- 回路最適化

- 0 ステートマシン

- リセット信号

- ユーザーモード時のリセットケア

- O Clock Crossing Bridge / FIFO のリセット

- クロック (PLL 等) が安定するまで内部リセット

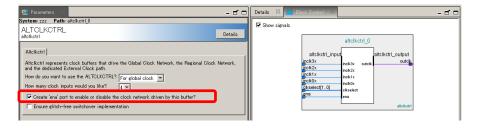

## グリッチ

- ゲートクロック

- 不具合事象

- ゲートクロック の制御信号 (Enable) にグリッチが発生する

ALTOLKOTRL

Altalkotri represents clock buffers that drive the Global Clock Network, the Regional Clock Network, and the dedicated External Clock path.

How do you want to use the ALTCLKCTRL? For global clock

How many clock inputs would you like? 4 ₩

- 対策

- ALTCLKCTRL を使用: ALTCLKCTRL の Create 'ena' port to enable or disable the clock network driven by this buffer を使用しグリッチを除去

- クロックセレクト

- 不具合事象

- クロックを排他的に使用する場合、クロックを切り替えた際にグリッチが発生する

- 0 対策

- ALTCLKCTRL で Ensure glitch-free switchover implementation を使用してグリッチを除去

Details

✓ Show signals

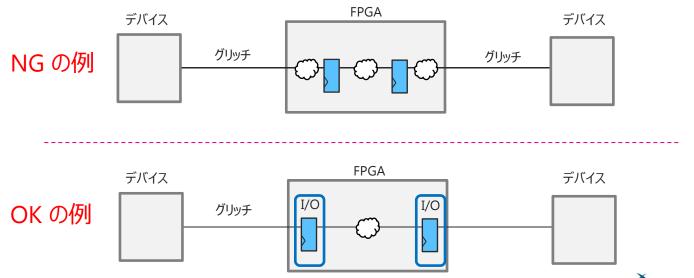

## グリッチ

- FPGA の入出力処理

- 不具合事象

- 外部デバイスからの信号を FPGA に取り込む・出力する際にグリッチが発生した信号を送受することがある

- 対策

- FPGA の入力、出力は I/O 内の FF で叩いた信号を使用

- I/O 内の FF に割り当てる方法は、Assignment Editor で Fast Input Register/Fast Output Register を割り当てて使用(<u>Appendix 8. 参照</u>)

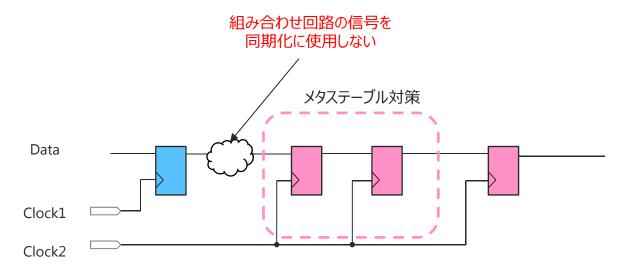

### 非同期回路

- 非同期の受け渡しに組み合わせ回路を使用

- 不具合事象

- 非同期の受け渡しに組み合わせ回路を使用するとグリッチが発生しデータ化けが 発生する可能性あり

- 対策

- 非同期の受け渡しは、組み合わせ回路は使用しない

- 組み合わせ回路の出力信号(LUT の出力)には「必ず」グリッジが発生するものとして取り扱うこと

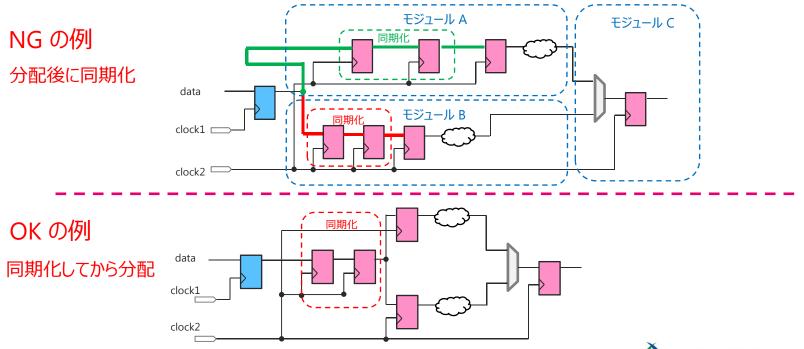

## 非同期回路

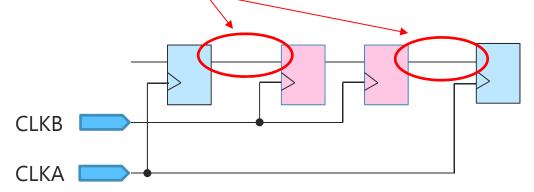

#### 非同期レーシングのケア

- 不具合事象

- 1本の非同期信号を複数個所で同期化することにより、レーシング発生

- バスの伝送を FF で 2 段受けする場合は、1 クロック分データ化けが発生

#### ○ 対策

- レーシングを防ぐため、同期化してから分岐

- モジュールを跨って設計する際には注意が必要

### 回路最適化

- ステートマシン

- 不具合事象

- コンパイルする際にイリーガルステートが最適化により実装されず、何らかの要因によりイリーガルステートに遷移した場合にデッドロックする場合がある

- イリーガルステート記述

- Verilog HDL : default

- VHDL : others

- 対策

- インテル® Quartus® Prime の設定 ⇒ "State Machine Processing" を "<mark>User Encoded</mark>" にして以下の設定を行う

- イリーガルステートを記述している場合

- = Safe State Machine = ON で設定 (イリーガルステートの最適化を防ぐため)

- イリーガルステートを記述してない場合

- = Safe State Machine = OFF で設定 (イリーガルステートが存在しないため)

設定方法については、Appendix 9-5. ステートマシンの設定方法参照

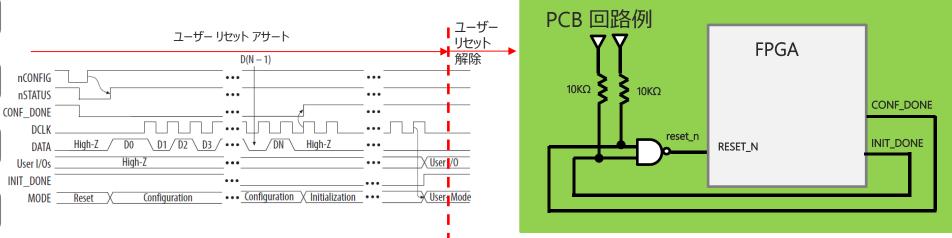

#### リセット信号

- ユーザーモード時のリセットケア

- 不具合事象

- コンフィグレーション開始からユーザーモードに至るまでリセットを入れておかないと FF の初期値が保証されない

- 対策

- ユーザーモードに入るまでリセットを供給

- https://www.intel.com/content/www/us/en/programmable/support/supportresources/knowledge-base/solutions/rd06112009 450.html

- CONF\_DONE と INIT\_DONE の AND したものをリセット信号として使用

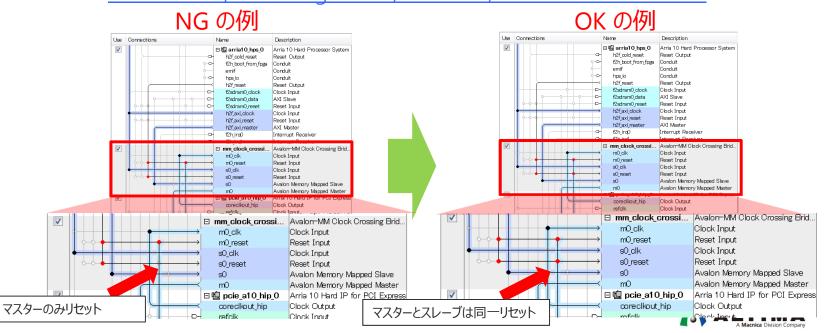

#### リセット信号

- Clock Crossing Bridge / FIFO のリセット (Platform Designer 使用時)

- 不具合事象

- マスターとスレーブのリセットが異なるために内部 FIFO のアドレスポインターのリセット タイミングが異なり誤動作

- 0 対策

- マスター側とスレーブ側のリセットは、同じ信号を使用してアサート

- <a href="https://www.intel.com/content/www/us/en/programmable/support/support-resources/knowledge-base/solutions/rd08042014">https://www.intel.com/content/www/us/en/programmable/support/support/support-resources/knowledge-base/solutions/rd08042014</a> 443.html

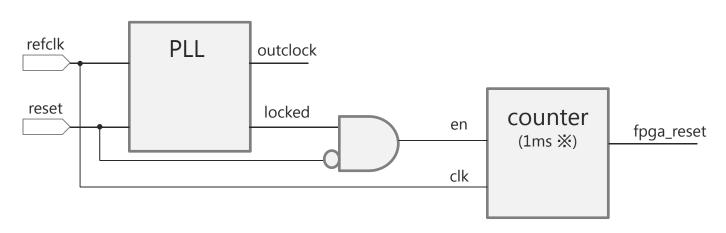

### リセット信号

- クロック (PLL 等) が安定するまで内部リセット

- 不具合事象

- クロックが不安定な状態で論理を動作させてしまうと、意図しない挙動で回路が動作

- 対策

- フリーランニングのリファレンス・クロックが要求されている場合は、フリーランニングが必須

- トランシーバー・クロックなど

- PLL 使用時、Lock 信号を見て、ユーザー回路のリセットを解除

- コンフィグレーション終了時にクロックが未供給の場合は、安定したクロックが供給されたあ とにリセットを解除する

※ counter 値は、Datasheet の tLOCKを参照

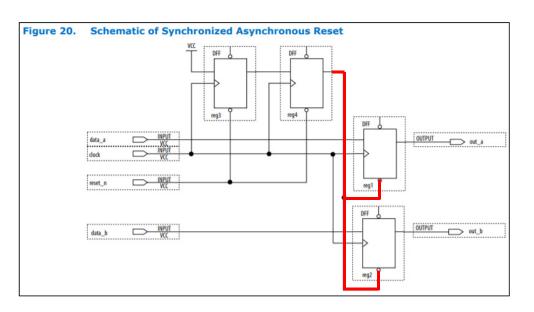

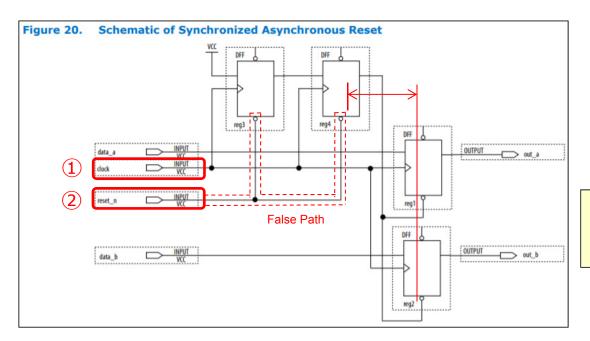

### リセット信号:推奨リセット構成

- 同期化された非同期リセット

- 非同期でアサートを行い、同期でディアサートする

- 0 メリット

- 非同期アサート: リセットを掛けると、非同期で全ての回路にリセットが入る

- 同期ディアサート:解除時はクロックに同期しているためメタステーブルの問題が無くなる

- 回路例:下図

- 赤線が Reg3/Reg4 により同期化された Reg1/Reg2 に対する非同期リセット

### リセット信号:推奨リセット構成 Cont.

- 同期化された非同期リセット:非同期パスに対する SDC 制約のかけ方

- 以下の2つの制約が必要

- 1. クロック(図の①)に対して create\_clock の制約をする

- 2. リセット (図の②) に対して set\_false\_path の制約をする

- set\_false\_path -from [get\_ports {reset\_n}] -to <all\_registers>

Reg1、Reg2 に対してcreate\_clockで制約したクロックが非同期リセットのRecovery/Removal を満たしているか、ツールが自動で解析

タイミング・アナライザーにて、該当クロック に対して Recovery/Removal の Slack 値 がマイナスになっていないか確認

- 入力クロック信号の I/O 設定は正しいか

- インテル® Quartus® Prime のレポートファイルで確認 (Appendix 1-3. 参照)

- Differential / Single-end

- AC-Coupling / DC-Coupling

- On-Chip Termination / External Termination

- シングル・エンド・クロックを使用する場合はクロック入力ピンの差動ペアのpチャネルにクロック信号をアサインをしているか

- 入力クロックのジッターは FPGA のスペックに収まっているか

- 入力クロックは SDC で設定したスペックに収まっているか

- コンパイル時にワーニングは発生していないか

#### Arria 10 Datasheet

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/arria-10/a10\_datasheet.pdf#page=37\_

#### Stratix 10 Datasheet

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/stratix-10/s10\_datasheet.pdf#page=43

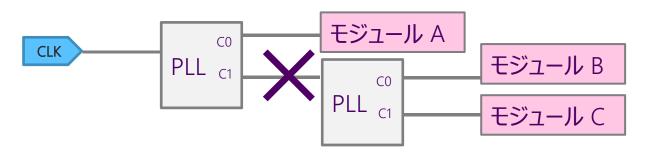

- PLL をカスケード接続していないか

- PLL カスケードは避ける

- PLL カスケードを使用する必要がある場合は、適切な設定で使用する (Appendix 10-1. 参照)

- カスケード専用配線を使用する

- PLL 設定 (Bandwidth) は下記の通りに設定

- ソース (upstream) PLL の Bandwidth 設定は Low に設定

- ディスティネーション (downstream) PLL の Bandwidth 設定は High に 設定

- ・スペックがない場合は、実測した計測値を SDC に入力する

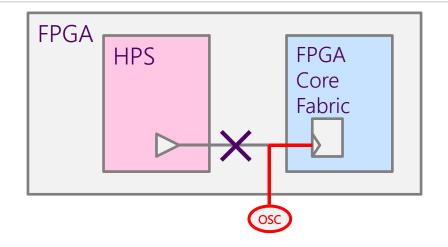

- HPS クロックを FPGA で使用しない

- HPS クロックのジッター定義が できない

- 対策:外部からクロックを入力

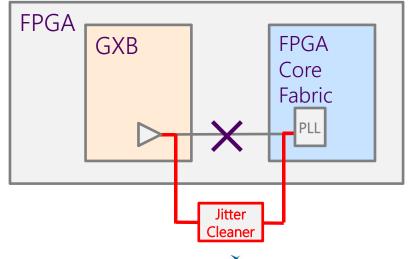

- トランシーバーからのリカバリークロックを PLL に接続して使用しない

- トランシーバー・クロックのジッター 定義ができない

- 対策:ジッター・クリーナー・デバイスを 使用して外部からクロックを入力

## 電源電圧の確認

#### 電源電圧の確認

- 電源電圧、温度環境によって現象は変化するか

- 電源電圧を高く・低くして不具合の発生頻度の変化を調べる

- デバイス温度を高く・低くして不具合の発生頻度の変化 を調べる

- 過渡負荷時、同時スイッチング時に現象が発生していないか

- 電源が安定的に供給されているか確認

- "Power & Thermal 関連 デザイン & デバッグガイドライン" を 参考にして、電源を見直す

- http://www.altima.jp/members/p1-literature/2device/1-altera/086\_power\_thermal\_dd\_guide.cfm

それでも解決しなかったら......

## それでも解決しなかったら…… (残りの20%)

- ボード起因

- リファレンス抵抗値の間違い

- Vcc または Ground への直接接続箇所への抵抗挿入

- ボードの製造不良

- はんだの接触不良(押すと改善する)やコンデンサー/抵抗の値の間違いや値抜け(試作や手付けの場合に多い)

- 対向デバイスの故障

- 外部メモリーに多い

- 実装デバイスが想定と異なる(ヒートシンクの下なので気づかず)

- ES デバイス (ES への Production デバイスのデータの書込み)

- スピードグレートが異なるデバイス (遅いデバイスへの速いデバイスのデータを書込み)

- 信号品質

- アイマスクのマージン不足・割れ

- ツール起因

- 古いバージョンのインテル® Quartus® Prime / IP を使用

- インテル®Quartus®PrimeバージョンとIPバージョンが違う場合は特に注意が必要(基本的に禁止)

- スピードグレードの選択ミス

### 不具合事例

### 不具合事例

- **事例①**: 再コンパイルを行うと、DDR4 のデータが稀に化ける時がある。温度を上げるとデータ化けが起きなくなる確率が高くなる

- ● 原因: DDR4 とユーザー回路間のパスでタイミングエラーが発生していたが、タイミング解析を行う必要がないパスだと誤認識し、ユーザーが False Path に設定してしまっていた

- 事例②: Ethernet 通信が1週間ほど経過するとスタックしてしまう

- 原因:非同期信号のレーシングが発生しており、ユーザー回路を同期化することで安定的に動作した。

- **事例③**:2年間動作実績がある装置が、新たに納入されたデバイスから数%の割合で誤動作する

- **原因**: タイミング解析を行っていなかったため、多くのパスでタイミングエラーが発生していた。制約を見直してタイミングエラーを解決することで安定動作した

- **事例④**: Nios® II が動作中にフリーズしていまう

- 原因: Platform Designer でクロック・クロッシング・ブリッジを挿入しておらず非同期パスに対して False Path 設定を行っていた。 Platform Designer の構成を見直すことで正常に動作した

#### 不具合事例 Cont.

- **事例**⑤: ロケーションによって PLL が Lock しない場合がある

- 原因: Cyclone® V で、PLL 用のリファレンス電圧 RREF ピンを 2k Ω でプルダウンしておらず、正しく処理する ことで定常的に PLL が Lock するようになった

- **事例**6: PCI Express (PCIe) が電源の ON/OFF でリンクしない場合がある

- **原因**:トランシーバーのリコンフィグ・コントローラーのクロックが外部クロックではなく、内部の PLL からのクロックが 使用されていた

- 事例②: PCle が電源の ON/OFF でリンクしない場合がある

- 原因: トランシーバーの電源が FPGA 端でドロップしていた。 qsf の設定値と実際の電圧もあっているか確認

- **事例**®: DDR3 にてキャリブレーションは成功したにもかかわらず稀にデータ化けが起きる

- **原因**:タイミング制約の見直し及び電源の精度を確保したことにより改善

### さいごに

FPGA の正常な動作を保証するためには、適正な動作環境下で、適切に設定されたタイミング制約を守っている必要があります。

- 一方で、実際に FPGA にコンパイルデータをダウンロードして動作させた場合、下記のような不具合事象が発生する場合があります。

- ・ユーザーデザインを変更していない場合であっても、**コンパイル毎に不具合動作・頻度・発生の有無が異なる**

- ・調査のために Signal Tap を挿入すると、不具合現象が再現しなくなる

- ・FPGA の個体により不具合動作・頻度・発生の有無が異なる(P)

- ・電源電圧を変化させると不具合動作・頻度・発生の有無が異なる(V)

- ・温度が変化すると不具合動作・頻度・発生の有無が異なる(ある時間、動作させていると不具合動作が発生するようになる)(T)

- ・ある時点から(ある製品ロットから)不具合動作が発生するようになる(P)

- ・対向デバイスを交換すると事象が変化する

これらの事象は、多くの場合、以下のような FPGA の特徴や半導体の特性に起因して発生することが経験的に確認されています。

- ・適切にタイミング制約が設定されていない

- ・信号間の到達時間差(どれかが早い、遅い、同時)に対して、その時間差を考慮した回路構成となっていない

- ・タイミング制約およびタイミングモデルで規定した条件外での使用

本資料では、タイミング制約の生成方法や不具合が発生しにくい回路構成を示すとともに、不具合発生時のデバッグ手順を示しました。

本資料が不具合発生を防ぎ、不具合発生時にはデバックの一助となることを期待します。

# Thank you!

# Appendix

### アジェンダ

- 1. レポートファイルの生成方法

- 1. サマリーレポート

- 2. 特定パスのレポート

- 3. 入力クロックピンの I/O 設定

- 2. タイミング制約

- 1. クロックの設定

- 2. クロックグループの設定

- 3. False Path の設定

- 4. コンパイル後の False path の指定

- 5. AC スペック の設定

- 6. マルチ・サイクル・パスの設定

- 3. コンパイル毎/Signal Tap 追加時に動作しない 場合の確認事項

- 4. Signal Tap 追加時の SDC 制約における注意 事項

- 5. PLL Location, PLL Mode 等の確認方法

- 6. タイミングスラックの改善を模索

- 7. Timing Optimization Advisor

- 8. I/O エレメントレジスター設定

- 9. その他回路記述での注意点

- 10. PLL カスケード関連情報

- 1. 各種デバイスハンドブック

- 2. ユーザーガイド

### 1-1. レポートファイルの生成方法 <サマリーレポート>

- Timing Analyzer Summary Report の生成/確認

- O Timing Analyzer Summary Report はフルコンパイル時に自動生成

- デフォルトでは下記に保存されている

- パス: < Project Folder >¥output\_files

- 名前: < Project Name >.sta.rpt

- タイミング解析詳細レポート

- 名前: < Project Name > .sta.summary

- タイミング解析サマリー

- 特定パスのレポートの生成方法は次項で説明

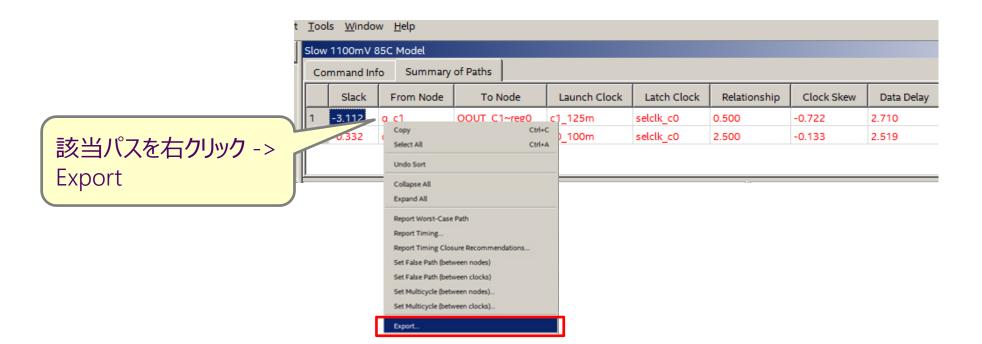

### 1-2. レポートファイルの生成方法 <特定パスのレポート>

- 特定のパスはタイミング・アナライザーで生成する必要がある

- 特定のパスのレポート生成方法

- Quartus -> Tools -> Timing Analyzer

- 所望のレポートをタイミング・アナライザー上で生成

- レポートを生成する特定のパスをハイライトし、右クリック -> Export

- テキスト方式もしくは HTML 形式を選択して保存

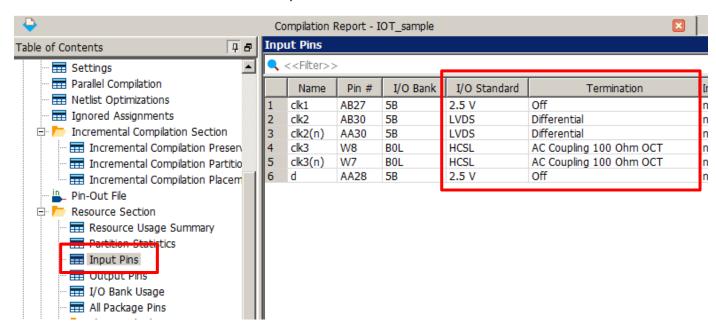

### 1-3. 入力クロックピンの I/O 設定

- Fitter 実行後に生成されるレポートを確認

- o GUI の場合は

- Compile Report -> Fitter -> Resource Section -> Input Pins

- テキストファイルの場合は

- パス: < Project Folder >¥output\_files

- 名前: < Project Name > .fit.rpt

### 2-1. タイミング制約 <クロックの設定>

- タイミング解析の対象となるクロックを定義

- FPGA に入力されるクロックの定義

- コマンド: create\_clock

- 例: create\_clock -name clkin\_a -period 10 [get\_ports CLKA]

- PLL の出力クロックを定義 (Stratix 10 を除く)

- コマンド: derive pll clocks

- FPGA内部で分周/逓倍されたクロックの定義

- コマンド: create\_generated\_clock

- 例: create\_generated\_clock -name divclk -source [get\_ports CLKA] -divide\_by 2 [get\_pins DIVFF|regout]

- FPGA 内部のクロックのバラツキ (ジッターやスキュー)を定義

- コマンド: derive\_clock\_uncertainty

- 全てのデザインに使用することを推奨

- 外部クロックのジッターやクロックに余裕を持たせる場合などに使用

- コマンド: set\_clock\_uncertainty

- 例:set\_clock\_uncertainty -from { CLKA } -to \* -setup 0.2

- 同一ポートに二重でクロックを定義した場合は下の行の制約が有効

- 上書きしないためには -add コマンドを使用

- 確認方法

- コンパイル後、Timing Analyzer -> Report Clocks

- 与えた制約が意図した通りに認識されているか確認

- クロック信号統図との相関を確認

### 2-2. タイミング制約 <クロックグループの設定>

- 同期クロックをグループで纏め、グループ間で非同期のクロックとして指定し、タイミング解析時に指定したクロック間(不要なパス)の解析を行わないようにする

- コマンド: set\_clock\_groups

- -group: クロックのグループを指定

- -asynchronous: クロック間の関係が非同期の時

- -exclusive: クロック間の関係が排他的の時

- CLKA CLKB

- 例:set\_clock\_groups -exclusive -group {CLKA} -group {CLKB}

- 確認方法

- Timing Analyzer -> Report Clock Transfers

- 解析不要なクロック間のパスは "false path" としてレポート

### 2-3. タイミング制約 < False Path の設定 >

- 特定のノードに対してタイミング制約を行わない場合に使用

- コマンド: set\_false\_path

- 例:

- set\_false\_path -from [get\_clocks CLKA] -to [get\_clocks CLKB]

- set\_false\_path -from [get\_clocks CLKB] -to [get\_clocks CLKA]

- False path を指定する場合の回路例

- 非同期であることを考慮して設計してる場合

- 注意事項

- ワイルドカード「\*」を使用して制約を与えた場合、本来解析しなければいけないパスを解析の対象から 外してしまう可能性があるため注意が必要

- 一度 set\_false\_path を記述してしまうと、そのあとの行でタイミング制約を与えても無効になる

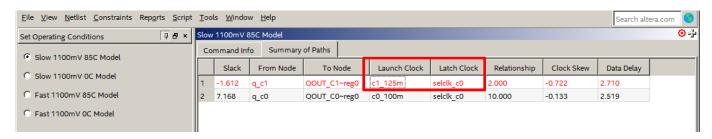

## 2-4. コンパイル後の false\_path 指定

- コンパイル後、タイミング・アナライザーで非同期パスを false\_path 指定する方法

- 該当のパスをタイミング・アナライザーで表示

○ 該当パスを右クリック -> set\_false\_path を選択

- Constraints -> Write SDC で SDC を生成

- 該当のパスが false\_path 指定されていることを確認し、ユーザーで作成した SDC に追記

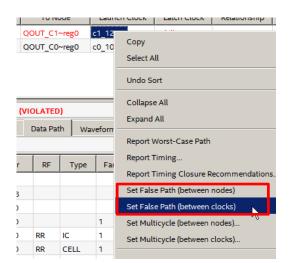

### 2-5. タイミング制約 <AC スペックの設定 >

- FPGA への入出力に対する制約には**仮想クロックを定義**して制約を与える

- 仮想クロックを使用して set\_input\_delay / set\_output\_delay を定義

- 同一クロックソースであっても仮想クロックの使用を推奨

- コマンド: create\_clock

- 例: create\_clock -name {CLK\_vir} -period 10

- FPGA に対応する port / pin は存在しないため周期のみの定義となる

- 外部デバイスと FPGA 間の入出力に対する制約

- コマンド: set\_input\_delay / set\_output\_delay

- 例:

- set\_input\_delay -clock {CLK\_vir} -max 0.5 [get\_ports {DATA\_A}]

- set\_input\_delay -clock {CLK\_vir} -min 0.2 [get\_ports {DATA\_A}]

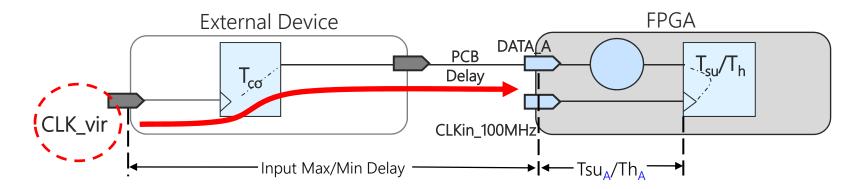

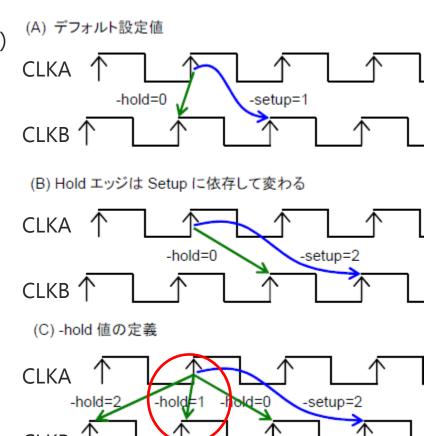

### 2-6. タイミング制約 <マルチ・サイクル・パスの設定>

- データの伝搬に1クロックサイクル以上必要なパスに与える制約

- コマンド: set\_multicycle\_path

- -setup: セットアップ解析時のサイクル数を増加させる(デフォルト値は 1)

- -hold:ホールド解析時のサイクル数を増加させる(デフォルト値は 0)

- -start : 送信クロックサイクルでサイクル数を指定をする場合に使用

- -end: 受信クロックサイクルでサイクル数を指定をする場合に使用

- 例:右図の赤丸の場合

- set\_multicycle\_path -end -setup -from CLKA -to CLKB 2

- set\_multicycle\_path -end -hold -from CLKA -to CLKB 1

- 設計者はマルチサイクルで与えた制約で、 正しく回路が動作するように設計する必要がある

- マルチ・サイクル・パスの使用例

- デザインが 1 クロックでデータ伝搬を要求していない場合

- 必要以上に厳しい制約条件を与えることを避ける

- レジスターが各クロックエッジごとにデータをサンプリングする必要がない場合

# 3. コンパイル毎/Signal Tap 追加時に動作しない場合の確認事項

- SDC は正しく与えているか

- AC スペック と クロック信号統図を基に SDC 制約内容を確認

- 前項の各種レポートの内容を確認

- Signal Tap 追加時は JTAG 制約と false\_path 制約を与える

- 注意事項は次項に記載

- 要求タイミングを満たしているか

- SDC が正しいが、タイミングを満たしていない場合の対処方法例を後述

## 4. Signal Tap 追加時の SDC 制約における注意事項

- JTAG 制約

- o インテル® Quartus® Prime Handbook に記載の Cook book を活用

- インテル® FPGA ダウンロード・ケーブル (USB-Blaster II) 使用時、TCK の周波数を 指定可能

- 実機で使用している TCK 周波数と SDC で与えている TCK 周波数を同一にする

- 10 ピンヘッダから FPGA までのトレース長を考慮した SDC 制約を与えることが可能

- Signal Tap に対して False path 制約を与える

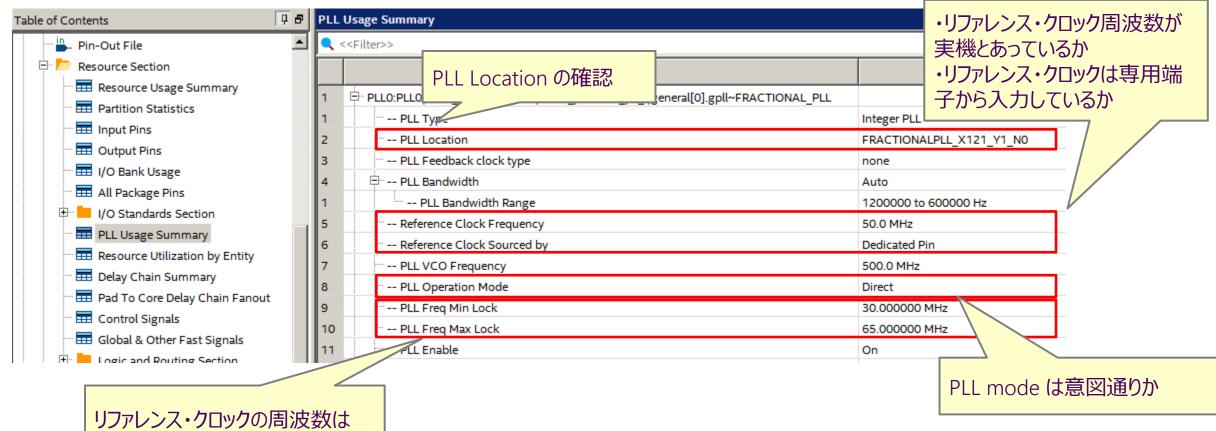

### 5. PLL Location / PLL Mode の確認方法

- インテル® Quartus® Prime の Fitter report で確認可能

- Compile Report -> Fitter -> Resource Section -> PLL Usage Summary

リファレンス・クロックの周波数はロックレンジに収まっているか

### 6. タイミングスラックの改善を模索

- インテル<sup>®</sup> Quartus<sup>®</sup> Prime の設定/制約を変更

- 配置配線結果が変わることで、タイミング解析結果が変わることを期待。

- Compiler Settings

- Timing Optimization Advisor

- 他の設定や制約

- デバイス変更

- スピードグレードを上げる

- デザインを変更

- レジスター間の組み合わせ回路の見直し

- レジスターの追加(パイプライン化) など…

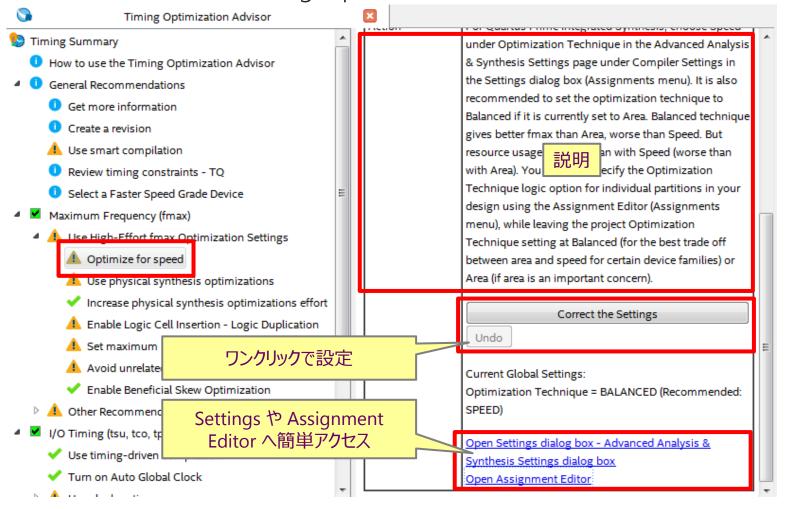

### 7. Timing Optimization Advisor

:設定済み

未設定(設定するかは設計者判断)

- パフォーマンスの最適化に関するアドバイザー機能

- O Tools メニュー -> Advisor -> Timing Optimization Advisor

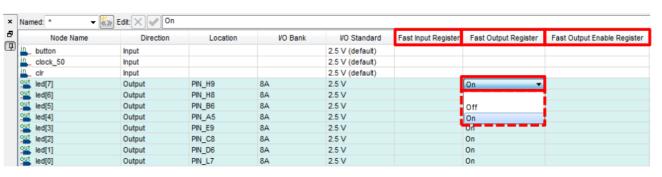

### 8. I/O エレメントレジスター設定

- I/O エレメント内のレジスターへマッピングさせるオプション

- タイミングを高速にするオプション

- セットアップ時間、クロック to アウトプット時間

#### 設定手順

- 1. Pin Planner を起動 (Assignments メニューより)

- 2. Pin Planner 内の All Pins リストにて確認 下図は、Fast Output Register を On に設定する例

#### 設定後の確認

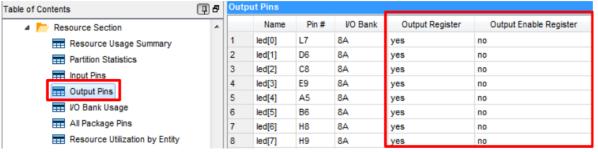

Compilation Report -> Fitter -> Resource Section 目的のピンを確認(下図の例: Output Pins) Output Register に "yes" と表示されていることを確認

#### 9. その他回路記述での注意点

- グリッチ

- パルス(リセット信号)生成回路

- 2. 非同期回路

- 異なるクロック間のケア

- 3. 非同期回路の確認方法

- タイミング・アナライザーを使用して MTBF を計測

- 4. リセット信号

- Stratix® 10 (Hyper-Register) を使用した場合のリセットのケア

- 5. 回路最適化

- ステートマシンの 設定方法

- 6. デザインチェック

- Design Assistant

- 7. HDL コーディング

- O Block RAM, DSP への割り当て

### 9-1. グリッチ

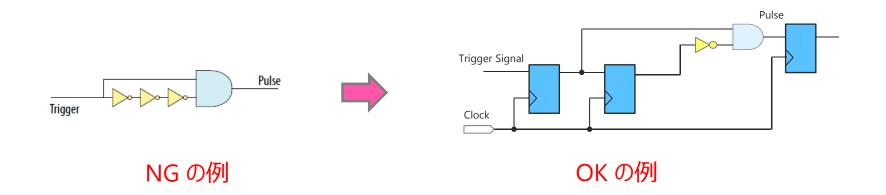

- パルス(リセット信号)生成回路

- 不具合事象

- パルス回路を組み合わせ回路で生成するとグリッチが発生する

- 0 対策

- パルス信号を同期化

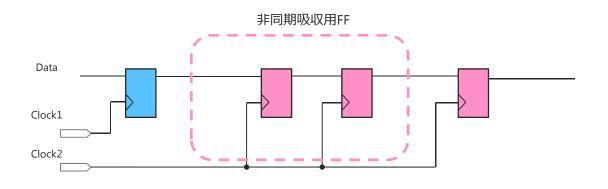

### 9-2. 非同期回路

- 異なるクロック間のケア

- 不具合事象

- 異なるクロックドメインで非同期渡しする際にメタステーブルが発生し、正しいデータが伝搬できない

- 0 対策

- 非同期吸収用の FF を 2段以上挿入

- FIFO よる非同期吸収 (Platform Designer の場合、Clock Crossing Bridge を使用)

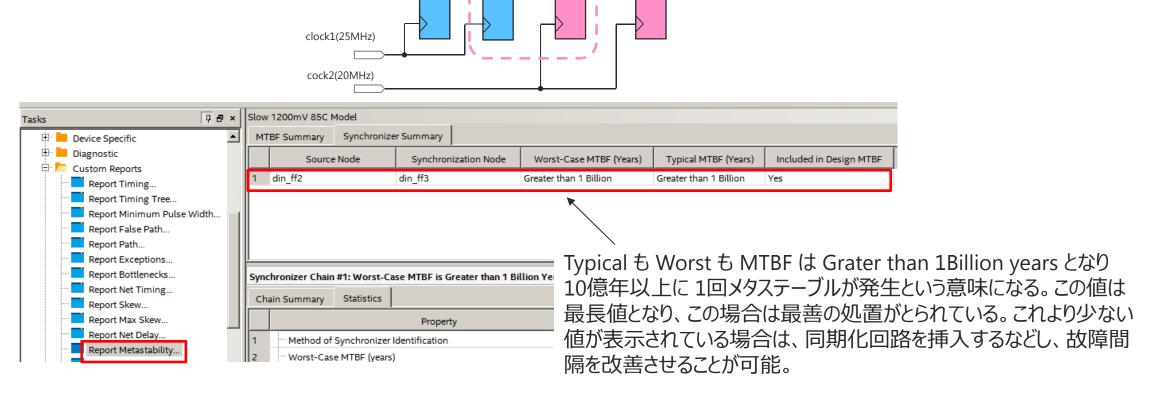

#### 9-3. 非同期回路の確認方法

タイミング・アナライザーを使用して MTBF を計測

data

○ 非同期に非同期吸収用の FF を入れた場合、挿入した FF の段数でどの程度信頼

din\_ff4

din\_ff3

din\_ff2

din\_ff1

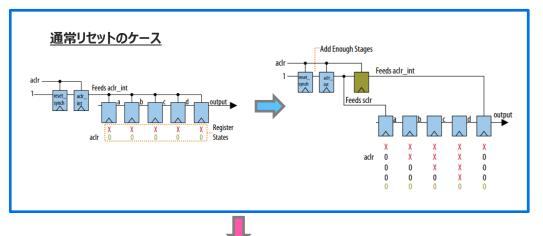

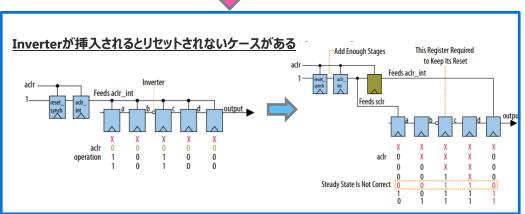

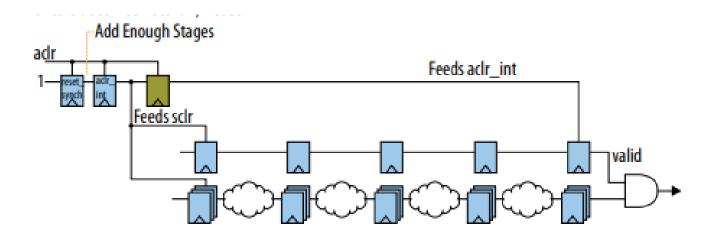

#### 9-4. リセット信号

- Stratix® 10 (Hyper-Register) を使用した場合のリセットのケア

- 不具合事象

- Hyper-Register は、リセットなしの FF になるため、誤ったリセット構成になり誤動作の原因となる

#### 推奨リセット構成

### 9-5. ステートマシンの設定方法

- State Machine Processing / Safe State Machine の設定方法

- O Assignments -> Settings -> Compiler Settings -> Advanced Settings (Synthesis...) より設定

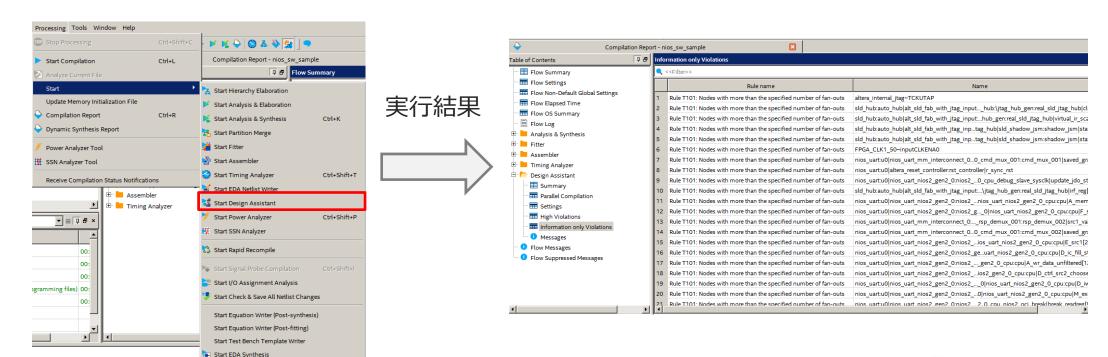

#### 9-6. デザインチェック

- Design Assistant

- インテル® Quartus® Prime には、コーディングをチェックするツール(HDLの lint チェック機能)

- O Stratix® 10, Arria® 10, Cyclone® 10 GX, MAX® 10 はサポート外

- 実行方法

- フルコンパイル完了後、Processing -> Start -> Start Design Assistant より実行

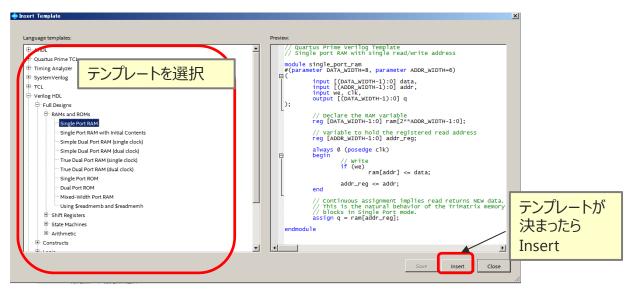

#### 9-7. HDL コーディング

- HDL のコーディング

- 不具合事象

- RTL の記述によっては、Block RAM や DSP に割当たらないケースあり

- 対策

- インテル® Quartus® Prime の RTL のテンプレートを使用して記述

- Verilog-HDL / VHDL のテキスト編集画面で 下記アイコンから Insert Template 用アイコンをクリックし、RAM や DSP のテンプレートを選択

```

Insert Template 用アイコン

Insert Template

Inse

```

## 10-1. PLL Cascading 関連情報:各種デバイスハンドブック

- Intel® Stratix® 10 Clocking and PLL User Guide

- o <a href="https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/stratix-10/ug-s10-clkpll.pdf">https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/stratix-10/ug-s10-clkpll.pdf</a>#page=23

- Intel® Arria® 10 Core Fabric and General Purpose I/Os Handbook

- o <a href="https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/arria-10/a10">https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/arria-10/a10</a> handbook.pdf#page=89

- Intel® Cyclone® 10 GX Core Fabric and General Purpose I/Os Handbook

- O <a href="https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/cyclone-10/c10gx-51003.pdf">https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/cyclone-10/c10gx-51003.pdf</a>#page=80

- Intel® MAX® 10 Clocking and PLL User Guide

- o <a href="https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/max-10/ug\_m10\_clkpll.pdf#page=39">https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/max-10/ug\_m10\_clkpll.pdf#page=39</a>

- Stratix V Device Handbook Volume 1: Device Interfaces and Integration

- o <a href="https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/stratix-v/stx5">https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/stratix-v/stx5</a> core.pdf#page=101

- Arria V Device Handbook Volume 1: Device Interfaces and Integration

- o <a href="https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/arria-v/av\_5v2.pdf#page=112">https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/arria-v/av\_5v2.pdf#page=112</a>

- Cyclone V Device Handbook Volume 1: Device Interfaces and Integration

- o <a href="https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/cyclone-v/cv-5v2.pdf">https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/cyclone-v/cv-5v2.pdf</a>#page=87

# 10-1. PLL Cascading 関連情報:各種デバイスハンドブック Cont. 🕕

- Stratix IV Device Handbook, Volume 1

- o <a href="https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/stratix-iv/stx4">https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/stratix-iv/stx4</a> 5v1.pdf#page=137

- Arria II Device Handbook

- o <a href="https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/arria-ii-gx/aiigx\_5v1.pdf#page=129">https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/arria-ii-gx/aiigx\_5v1.pdf#page=129</a>

- Cyclone IV Device Handbook, Volume 1

- o <a href="https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/cyclone-iv/cyiv-5v1.pdf#page=95">https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/cyclone-iv/cyiv-5v1.pdf#page=95</a>

### 10-2. PLL Cascading 関連情報:ユーザーガイド

- IOPLL Intel FPGA IP Core User Guide

- o <a href="https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug altera iopll.pdf">https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug altera iopll.pdf</a>

- O Arria 10, Cyclone 10 GX

- ALTPLL (Phase-Locked Loop) IP Core User Guide

- o <a href="https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug\_altpll.pdf">https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug\_altpll.pdf</a>

- O Cyclone 10 LP, Cyclone IV, Arria II, Stratix IV, or older

- Altera Phase-Locked Loop (Altera PLL) IP Core User Guide

- o <a href="https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/altera\_pll.pdf">https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/altera\_pll.pdf</a>

- Stratix V, Arria V, Cyclone V

# Thank you

#### 改版履歴

| Revision | 年月       | 概要   |

|----------|----------|------|

| 1        | 2018年12月 | 初版作成 |

弊社より資料を入手されたお客様におかれましては、下記の使用上の注意を一読いただいた上でご使用ください。

- 1. 本資料は非売品です。許可なく転売することや無断複製することを禁じます。

- 2. 本資料は予告なく変更することがあります。

- 3. 本資料の作成には万全を期していますが、万一ご不明な点や誤り、記載漏れなどお気づきの点がありましたら、弊社までご一報いただければ幸いです。

- 4. 本資料で取り扱っている回路、技術、プログラムに関して運用した結果の影響については、責任を負いかねますのであらかじめご了承ください。

- 5. 本資料は製品を利用する際の補助的な資料です。製品をご使用になる場合は、英語版の資料もあわせてご利用ください。