はじめに

物理法則に勝るものはありません。 抵抗器は、電気エネルギーを熱および電圧降下として放出します。コンデンサーは、電荷を保存するのに時間がかかり、電荷を解放するのに時間がかかります。 インダクターは、電磁界を生成して崩壊させるのに時間がかかります。それについて私たちにできることは何もないため、電子機器の設計者は、熱電子バルブの時代から、巧妙な回路トポロジーを開発することによってこれらの要因を回避することを学びました。物理学は物理学であり、バルブで機能したことは、今日の高性能半導体にも同様に適用できることがわかりました。

ミラーの静電容量が高周波増幅を制限する方法

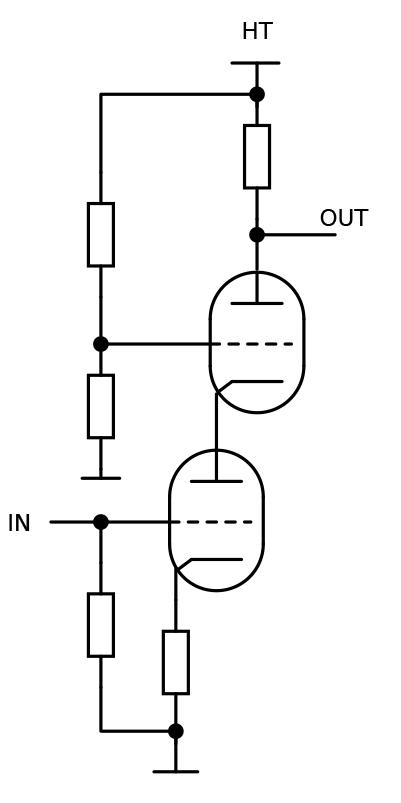

たとえば、ミラー効果を考えてみましょう。 1920年代、米国の電気技師John Milton Millerは、グリッドとアノードの間の内部容量が原因で、アンプとして使用した場合の単純な三極真空管の問題を特定しました。 この静電容量は、動作周波数の上昇に伴って静電容量のインピーダンスが低下するため、負帰還の量を増やすことにより、増幅器の帯域幅を減少させました。

Millerは、図1のように2つの三極真空管を直列に接続すると(CASCaded triODE、またはカスコードトポロジー)、入力から出力までの総静電容量が削減されることに気付きました。上部のチューブグリッドが固定電圧である場合、上部の三極真空管のカソード電圧は下部の三極真空管によって制御されます。四極管が内部スクリーンで開発されたとき、この内部静電容量とそれに関連する効果が減少し、数百メガヘルツで動作するシングルチューブアンプを構築することが可能になりました。

ミラー効果の復活

設計者が熱電子バルブを固体半導体に置き換え始めたときにミラー効果が戻り、これにより高周波動作が再び制限され始めました。

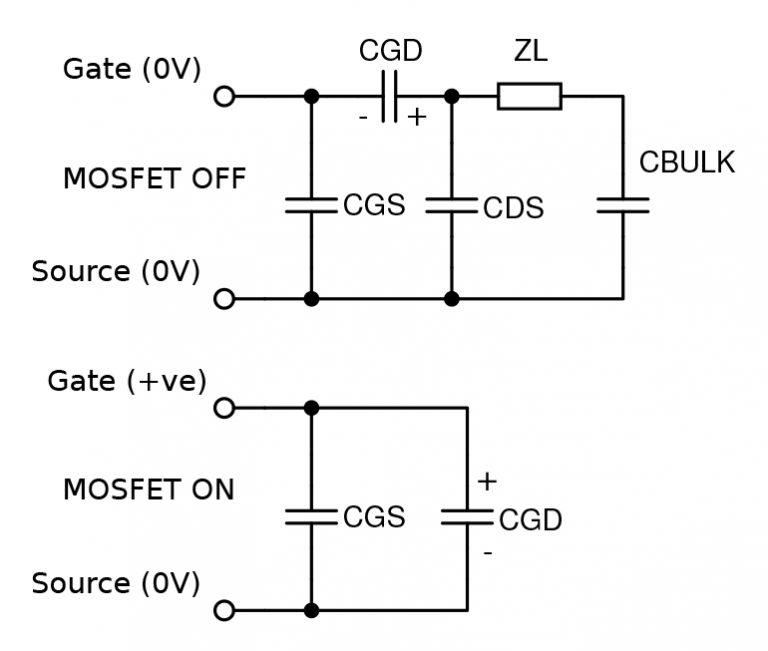

なぜそのようなことが発生したのでしょうか? MOSFETベースのスイッチング回路では、駆動回路が信頼性の高くかつ、低損失の方法で入力容量を充電および放電する必要があるため、ミラー効果によってスイッチング速度が制限されます。CGDと呼ばれるこのミラー容量の影響は、ゲート電圧によって異なります。

たとえば、ゲートが 0V のときにオフになるエンハンスメントモードMOSFETスイッチについて考えてみます。ゲート入力容量の合計は、CGS、CGD、CDS、負荷ZL、およびバルクを含むネットワークとして表示されます(図2を参照)。静電容量CBULK、CGDの両端にも正の電圧があります。MOSFETがオンになると、ドレイン電圧はほぼゼロに低下し、総容量はCGSと並列にCGDになり、オフ状態と比較するとCGDの両端に負の電圧がかかります。オンからオフに切り替えたり、元に戻したりする場合、入力容量はこれらの条件の間いったりきたりする必要があります。

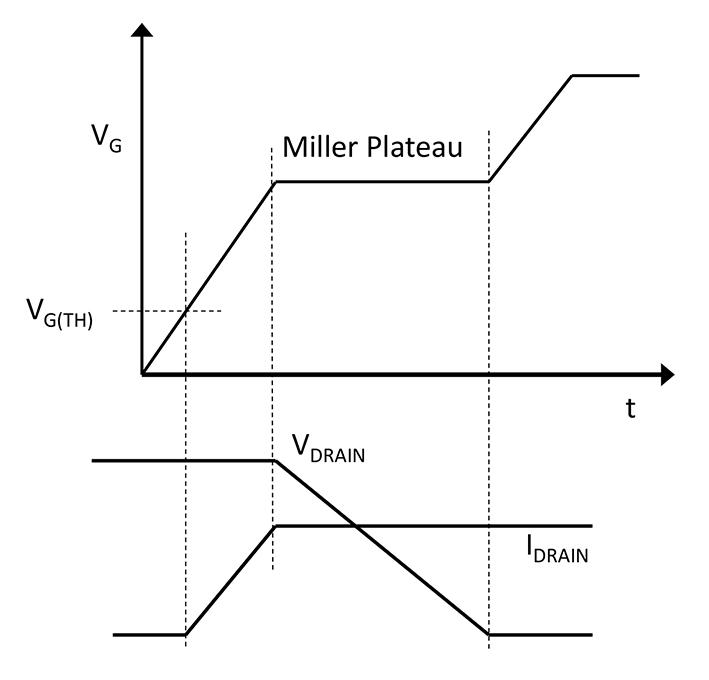

MOSFET のゲートスイッチング波形(図3 を参照)の正方向に向かう部分のプラトーは、2 つの入力キャパシタンス状態の間の遷移を表しており、ドライバーは急峻に動作しなければならず、スイッチングの遷移が遅くなります。さらに悪いことに、ドレインの電圧が下がると、正のオン電圧指令に対抗して CGD を通してゲートを負にしようとします。MOSFETをオフにすると、このプロセスは、MOSFETをオフに駆動すると逆になります。CGDはゲートの正電圧を「引っ張ろう」とするため、MOSFETやIGBTを使用する設計者は、この影響に対抗するために負のオフ状態のゲート電圧を使用することが推奨されています。これにより、ゲートを駆動するために必要な電力が増加します。

ゲート・ドレイン容量の制御

デバイスのゲート・ドレイン容量(CGD)は、半導体デバイスのアーキテクチャーに影響されるため、横置きか縦置きかによって変化します。低電圧MOSFETの場合、CGDを最小限に抑えることは可能ですが、高電圧では特に炭化ケイ素(SiC)や窒化ガリウム(GaN)などの材料を使用してワイドバンドギャップのデバイスを構築したい場合に問題となることがあります。これらの技術のスイッチング速度は、ミラー容量によって制限されており、この影響に対抗する最善の方法は、カスコード回路トポロジーを使用することです。

現代のカスコード

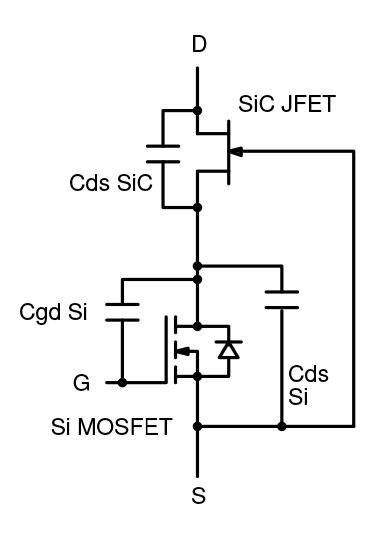

基本的なSiCスイッチは、接合FET(JFET)アーキテクチャーを採用しています。JFETを縦型デバイスとして構成すると、CGDが低くなり、ドレイン・ソース容量CDSも低くなります。しかし、JFETはゲートが0Vの常用ONデバイスであり、OFFにするには負のゲート電圧が必要となります。これは、電源を入れた瞬間にすべてのデバイスがデフォルトでオン状態になるブリッジ回路の問題です。このような回路は、Si MOSFETとSiC JFETをカスケード型トポロジーで配置することで、ノーマリーオフのデバイスを使用した方が良いと考えられます(図4)。

MOSFETのゲートとソースが0Vになると、ドレイン電圧が上昇します。JFETのゲートも0Vなので、MOSFETのドレインからソースの電圧が10Vまで上昇すると、JFETはゲートとソースの間に-10Vの負の電圧がかかり、オフになります。MOSFETのゲートがプラスになるとオンになるため、JFETのゲート・ソースをショートさせてJFETをオンにします。この回路トポロジーにより、「ノーマリーオフ」のデバイスが作られます。また、このトポロジーにより、直列入出力容量にはJFETのCDSが含まれており、これがゼロに近いため、ミラー効果や高周波利得への影響を低減することができます。

その他の利点

スイッチング中は、Si MOSFETのドレイン電圧は、JFETのドレイン-ソース間容量CDSがほぼゼロ、MOSFETのCDSがゼロではないことから、JFETのドレイン電圧を「ポットダウン」しているため、MOSFETのドレインは低電圧のままとなります。このため、MOSFETは、ドレインとソース間のオン抵抗が非常に低く、ゲートドライブ特性が格段に容易な低電圧タイプとすることができます。さらに、低電圧タイプのMOSFETのボディーダイオードは、順方向のドロップが非常に小さく、回復が速いという利点があります。JFETにはボディーダイオードがないため、整流ブリッジ回路や同期整流のように第3象限の逆スイッチ導通が必要な場合は、MOSFETのボディーダイオードが導通します。これにより、JFETのゲートソースは約+0.6Vにクランプされ、ハードオンが確実に行われ、低い電圧降下で逆電流が流れるようになります。

ミラー効果の終わり

SiCカスコードトポロジーは、ミラーキャパシタンスの問題を解決し、ゲート駆動が容易で、ノーマリーオフ動作が可能で、高性能なボディーダイオードも実現しています。これは、ボディーダイオードの特性が悪くなりやすいSiC MOSFETや、CDSが高くなりやすいGaN HEMTとは異なります。サーミオニックデバイスの高周波利得制限ミラー効果をもたらした物理学の不変性は、半導体デバイスにも適用されます。しかし、この物理学の不変性は、カスコードに基づいた問題解決策が、最新のSiCデバイスでも、昔ながらのバルブと同じように機能することを意味しています。

お問い合わせ

本記事に関してご質問などありましたら、以下より問い合わせください。

Qorvoメーカー情報Topページへ

Qorvoメーカー情報Topページへ戻りたい方は、以下をクリックください。