インテル®の 100G 開発キット、Stratix®V GX エディションは、下記をサポートすることで 100G システムのデザインの評価を可能にします。

特徴

この開発キットを使用すると、以下が可能となります。

- 光モジュールによる 10G/40G/100G ライン・インタフェースのサポート

- DDR3 (6x32 ビット)メモリ・バンクと QDRII BL2(1x36 および 1x18 ビット)メモリ・バンクによる、外部メモリ・インタフェースを必要とするアプリケーションのサポート

- 2 つの FCI社 AirMax コネクタを介したシステム側インタフェースの構築

- ライン側(光モジュール)からシステム側(AirMax コネクタ)までの完全なデータパスの解析

- 最大 12.5 Gbps のトランシーバ性能の評価

- フィジカル・メディア・アタッチメント(PMA)の10G/40G/100G イーサネット、Interlaken、CEI-6G/11G、および他の主要規格への準拠の検証

- SFP、SFP+、QSFP、CFP などの光モジュール間の相互運用性の確認

注文情報

| 製品名 | 100G 開発キット、Stratix V GX エディション |

| ご注文コード | DK-100G-5SGXEA7N |

開発キットの内容

100G 開発キット、Stratix V GX エディションには、以下のものが含まれています。

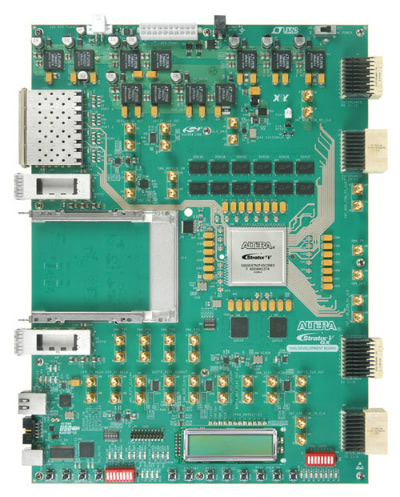

- Stratix V GX 開発ボード(図 1 参照)

- 搭載デバイス:5SGXEA7N2F45C2N

- EPM2210F324C3N、MAX®II 324 ピン CPLD

- FPGA コンフィギュレーション

- ファースト・パッシブ・パラレル(FPP)コンフィギュレーション

- 2 種類のコンフィギュレーション・イメージ(ファクトリおよびユーザー)を格納するための 1 ギガビット・フラッシュ・メモリ

- Quartus®II プログラマ、Nios®II ソフトウェア、およびシステム・コンソールで使用するためのオンボード USB-Blaster™ II ケーブル

- 外部 USB-Blaster ケーブル用 JTAG ヘッダ

- メモリ

- 12 個の 2 ギガビット DDR3 SDRAM

- 2 個の 72 メガビット QDR II SRAM

- 汎用ユーザー入力/出力

- 4 個のユーザー用プッシュボタン

- 2 個の DIP スイッチ

- 8 個のユーザー用 LED

- 2 行の文字表示用 LCD

- 10 個のコンフィギュレーション・ステータス LED

- コンポーネントおよびインタフェース

- 10/100/1000 イーサネット PHY および RJ-45 ジャック

- 48 本のトランシーバ・チャネル

- SMA インタフェース用:2 チャネル

- SFP+ インタフェース用:4 チャネル

- QSFP インタフェース用:8 チャネル

- CFP インタフェース用:10 チャネル

- Interlaken インタフェース用:24 チャネル

- 温度計測回路

- ダイ温度

- 電源

- 19 V DC 入力

- DC 電源入力用 2.5 mm バレル・ジャック

- 電源オン/オフ用スライド・スイッチ

- オンボード消費電力測定回路

- このキットには Quartus II 開発ソフトウェアのライセンスは含まれません。

図 1. Stratix V GX 100G 開発キット

関連資料

| ドキュメント | 説明 |

| ユーザー・ガイド(英語版・PDF) | 100G 開発キットのセットアップおよび搭載されたソフトウェアの使用方法について解説しています。 |

| リファレンス・マニュアル(英語版・PDF) | ボードのコンポーネントおよびインタフェースに関する詳細を含んでいます。 |

| キット・インストール (ESボード用) |

リファレンス・マニュアル、ユーザー・ガイド、クイック・スタートガイド、部品表、レイアウト、PCB、回路図、ボード・アップデート・ポータルのサンプル・ファイルなど、開発キットに含まれるすべてのファイルのフル・インストール |

| キット・インストール | リファレンス・マニュアル、ユーザー・ガイド、クイック・スタートガイド、部品表、レイアウト、PCB、回路図、ボード・アップデート・ポータルのサンプル・ファイルなど、開発キットに含まれるすべてのファイルのフル・インストール |