Intel: How do I manually specify the location of the ALTPLL?

Category: Tools

Tools: Quartus® Prime Standard Edition, Quartus® Prime Lite Edition

Devices: Cyclone® 10 LP, Cyclone® IV, MAX® 10

To manually locate the ALTPLL, use the Assignment Editor.

The contents to be specified for each item are shown in the table below.

| To column | ALTPLL node name * The ALTPLL node name specified in the To column differs depending on whether or not the Locked output signal is used. Please refer to the information in the table below. |

| Assignment Name field | Location |

| Value column | Specify the position information to be placed Element: PLL Location: PLL_<number> |

▶ When using the Locked output signal

| Node name selected in the To field |

| <pll name>:<instance name>|altpll:altpll_component|pll_altpll:auto_generated|pll1 |

| An example of how to specify |

|

Search for the above node name in the Assignment Editor's Node Finder.

|

▶ When not using the Locked output signal

* If Locked is not used, it can also be specified using the method for using the Locked output signal above.

| Node name selected in the To field |

| <pll name>:<instance name> |

| An example of how to specify |

|

Right-click Select > Locate Node > Locate in Assignment Editor on the ALTPLL IP from the Quartus® Prime Project Navigator and select the specified PLL name from the To column. (Refer to the figure below)

|

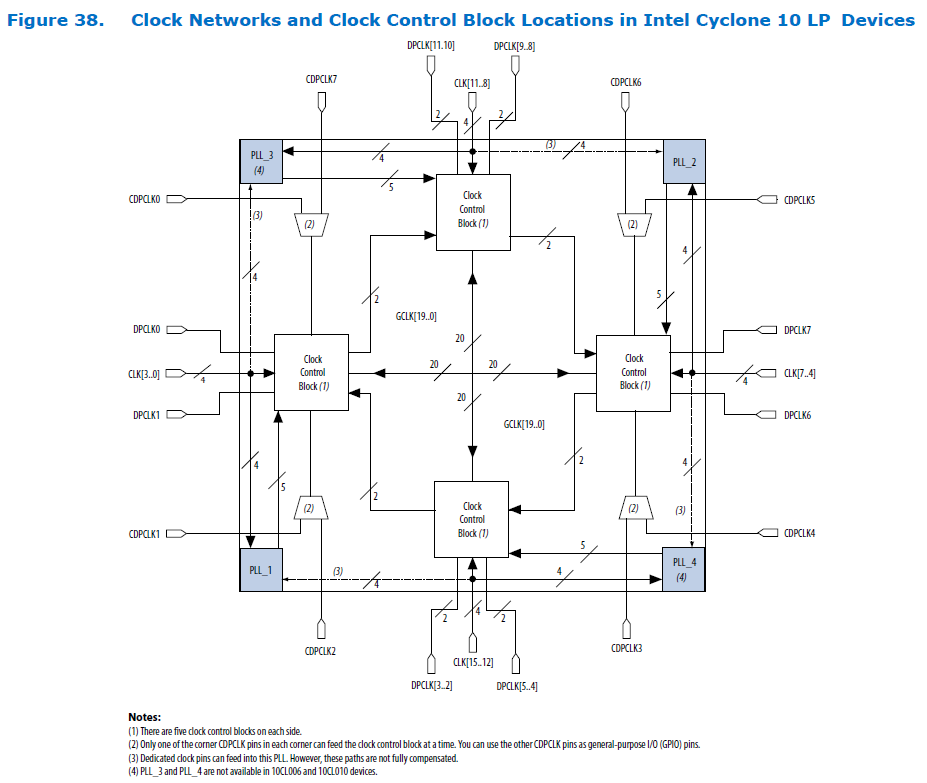

There is a correlation between the layout of the PLL reference clock pin and the location of the PLL in the FPGA series that support ALTPLL. (Refer to the figure below)

If the reference clock pin cannot be directly connected to the designated PLL, it will be connected via the clock control block, increasing the clock path delay.

On the other hand, even if the PLL is routed directly from the reference clock pin, there are paths whose compensation is not guaranteed by the FPGA family, so be sure to refer to the target device handbook.

Also, how to manually specify the location of the PLL Intel FPGA IP (formerly Altera PLL) can be found in this FAQ.

![]() Experienced FAE

Experienced FAE

Free consultation is available.

From specific product specifications to parts selection, the Company FAE will answer your technical concerns free of charge. Please feel free to contact us.