The Clock Domain and Synchronizer Structure Analysis tool allows you to extract possible metastable points from the circuit structure, such as signal connections between different clock domains.

▶ Introduction video

▶ Document

▶ Feature introduction (CDC Structural Analysis / Metastability Verification / Assertion Verification for Protocol Checks)

▶ Related information

▶ Seminar/Workshop

▶ inquiry

Introduction video

[movie]

Introducing Questa CDC

Document

[Material (PDF)]

let's try it! Questa CDC Tutorial

Import FPGA project for CDC analysis

<Environment construction>

Please refer to here for downloading and installing Questa CDC.

<Application for evaluation license>

If you do not have a license and would like to try out HyperLynx DRC, please contact us to request an evaluation license.

▶Inquiries (request for evaluation license), etc.

Please write "I would like an evaluation license". The person in charge will contact you.

Feature introduction

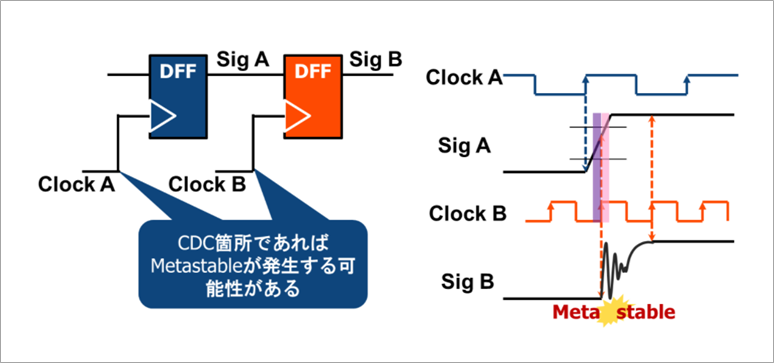

For multi-clock domain designs, simulation cannot accurately predict data transfers between different clock domains. Therefore, by analyzing the circuit structure that tends to cause problems in advance, countermeasures can be taken from the initial stage of design.

A problem in multi-clock domain designs is metastability. Metastability occurs when the timing of the transmit clock and the receive clock do not match, causing setup/hold timing violations. When metastability occurs, the received signal goes through an unstable state and then converges.

Each feature of Questa CDC is here.

CDC structural analysis

It automatically identifies clocks in the design, analyzes CDC between asynchronous data transfers, generates a report, and warns of CDC for which no countermeasure circuitry has been implemented.

You can identify and visually confirm the RTL parts that need to be addressed.

Metastability verification

Siemens EDA's patented metastability inductor (automatic metastability generator) randomly generates metastability that can occur from the circuit configuration, enabling verification close to actual machine operation. .

Assertion validation for protocol checks

This is done to check if the verification points inside the FPGA are working as intended.

ModelSim DE's built-in assertion validation uses the assertion language, while Questa CDC automatically inserts checks.

Related Information

▶ How to download the Siemens EDA tool

▶ How to install Questa CDC/Formal

▶ How to license Siemens EDA tools

Seminar/Workshop

How to distinguish between asynchronous clock domains that are often overlooked - FPGA Edition

▶ Siemens EDA Seminar

Inquiry

Manufacturer information Top

If you would like to return to the manufacturer information top page, please click below.

Trademarks and registered trademarks owned by Siemens: here