はじめに

こんにちは!くらみぃです。

ただいまマイコン演習と並行して、Quartus® Prime のタイミング解析について勉強しています。

タイミング解析とは、信号の遅延を考慮しても期待通りに回路が動作するか解析することです。

タイミング解析の概要やフローについては、私の先輩であるマス男さんが記事を書いていますので、ぜひご覧になってください!

今回はタイミング解析の中でも、クロックに対するタイミング制約を勉強していく中で学んだことを書きたいと思います。

タイミング制約とは

Quartus でのタイミング制約の与え方はとぷぅさんの記事に詳しく書いてありますので割愛します。

TimeQuest Timing Analyzer は SDC をサポートしています。

SDC はコマンド形式になっているので、各制約で使用するコマンドや使用するオプション( 引数 )などを覚えておかなくてはなりません。

大変ですね。

とぷぅさんの記事にもあるように、Quartus を使用するとグラフィカルにタイミング制約を与えることができます。

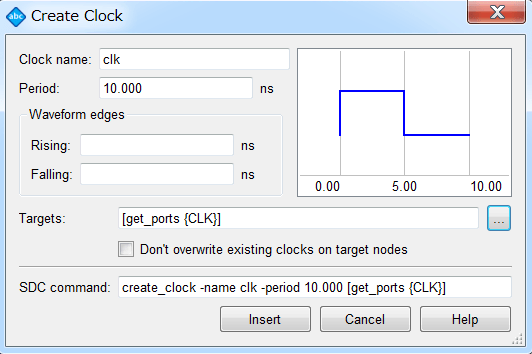

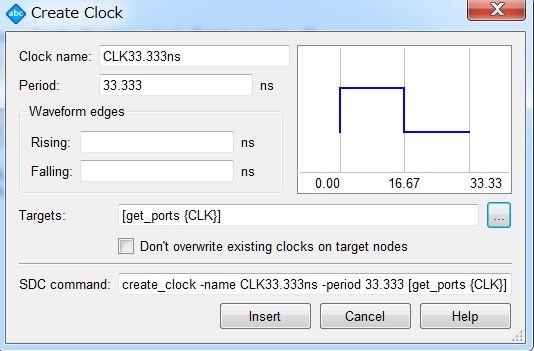

例えばデザイン上の CLK ポートに対して周波数 100 [ MHz ] の制約を与えたいとき、図 1 のように入力します。

周波数と周期は反比例な関係のため、 Period に入力する値は 10 [ ns ] となります。

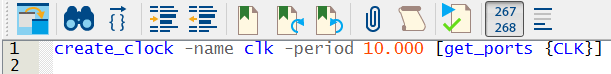

入力完了後に図 1 のInsert ボタンをクリックすると、 SDC Editor に図 2 のように表示されます。

簡単に制約を与えられて便利ですね!

そんなことを思っていた時に大先輩である I さんから一言。

「じゃあ 30 [ MHz ] の制約を与えるにはどうすればいいと思う?」

Period 項目には周期 ( ns ) で入力する必要があるので、まず周波数を周期に換算します。

周波数と周期は反比例の関係にあるので、

1 / 30 * 10^6 = 33.3333… [ ns ]

となります。

このように割り切れず循環小数となってしまっては、正確な 30 [ MHz ] の制約を与えることができません。

ではどうすればいいか。

調べた結果、 2 つの方法があることがわかりました。

1. 専用の SDC コマンドのオプションを使う

下記の SDC コマンドを SDC Editor に直接記入することで、周期ではなく周波数を基準に制約を与えることが出来るとわかりました。

create_clock -period 30MHz -name clk30MHz [get_ports clk]

2. Period 項目に小数点第 3 位まで入力する

例えば 30 [ MHz ] の制約を与えたい場合、 Period 項目に「 33.333 」と入力すれば 30 [ MHz ] の制約を与えたことになります。

理由は、 SDC で設定できる値が小数点第 3 位まで( 最小で指定できるのが 1 ps まで )のため、そこまで入力すると 30 [ MHz ] と認識されるからです。

実際に 2 つの方法で制約を与えてみましたので、見ていきましょう!

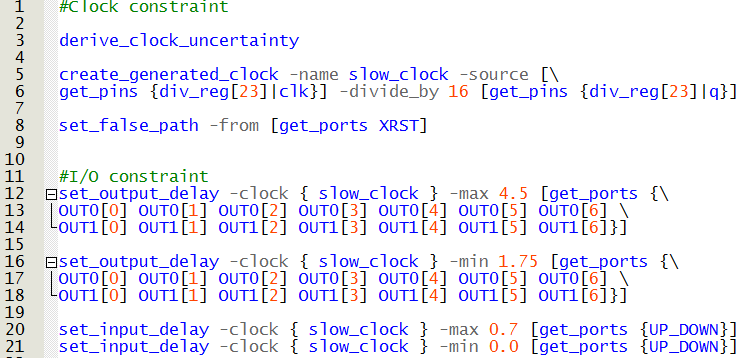

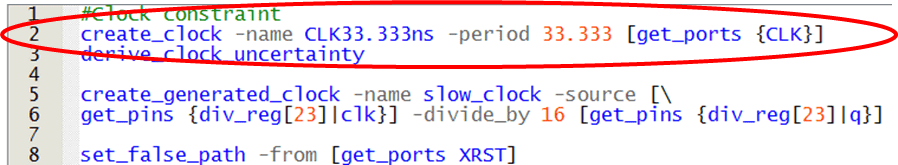

図 3 が今回使う SDC ファイルです。メインクロックに対する制約以外はすでに記述済みのものです。

まずは専用コマンドを使う場合についてみていきます。

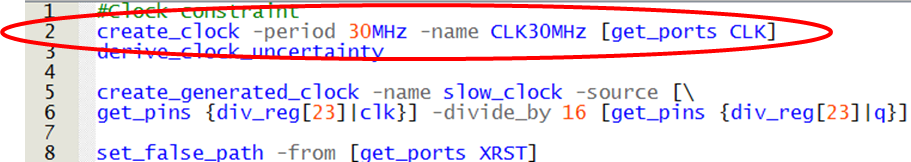

図 3 の 2 行目にコマンドを直接入力します。

今回は 30 [ MHz ] の制約を与えたいので、 -period 30MHz と入力します。

名前は任意で指定できますので、今回はわかりやすく CLK30MHz という名前にしたいため、-name CLK30MHz と入力します。

今回はターゲットがデザイン上にある CLK ポートなので、 [ get_ports CLK ] と入力します。(図 4 )

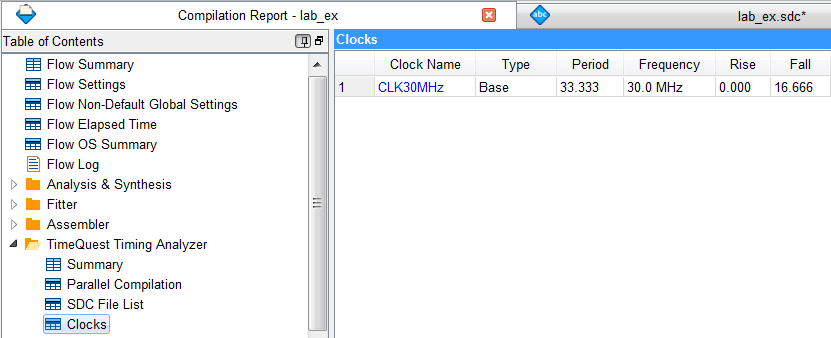

入力が終わったのでフルコンパイルをして、 Compilation Report を見てみると、 30.0 [ MHz ] の制約が与えられていることがわかります。(図 5 )

次に「 Period 項目に小数点第 3 位まで入力する」について検証したいと思います。

図 3 の 2 行目にカーソルを合わせ、右クリック→ Insert Constraint → Create Clock を選びます。

そして図 6 のように各項目に入力して Insert ボタンを押します。

すると図 7 のようになるので、保存した後フルコンパイルをしてみます。

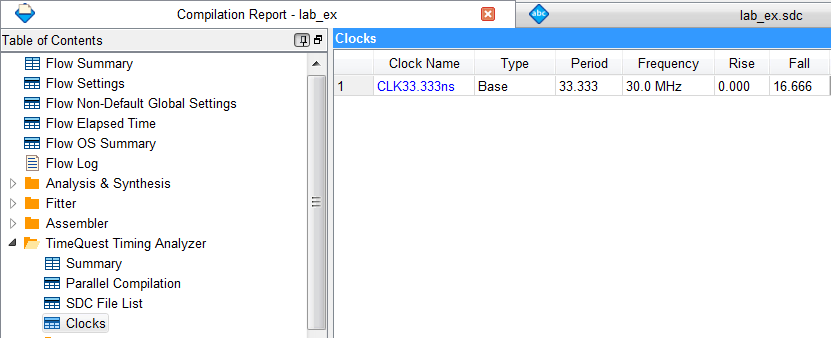

そして Compilation Report を確認してみると 30 [ MHz ] の制約が与えられていることがわかります。(図 8 )

まとめ

タイミング制約を与える際に、周期が循環小数になってしまうときの対処法は

1. 専用の SDC コマンドを使う

2. Period 項目に小数点第 3 位まで入力する

だということがわかりました。