デバッグ機能の実現方式

次にデバッグについて解説します。表 1はデバッグ機能実現方式の比較を示したものです。今回は代表的な方式についてあげましたが、実際にはこれらの中間的なものも存在します。以下各方式について解説します。

表 1 主なデバッグ機能実現方式の比較

|

方式 |

On-Chip デバッガ |

ハード サポート | ROM モニタ |

OS 依存 |

|

構成 |

ハード |

ハード+ソフト |

ソフト(ROM) | ソフト(RAM) |

|

デバッグ対象 |

ROM/RAM |

RAM |

RAM |

RAM |

| 実行/停止/中断 |

○ |

○ |

○ |

○ |

|

変数参照/修正 |

○ |

○ |

○ |

○ |

|

リアルタイム |

○ |

× |

× |

× |

|

リソース占有 |

◎ |

○ |

× |

○ |

|

その他 |

機能はハード量に依存 |

RAM容量 |

On-Chipデバッガ方式

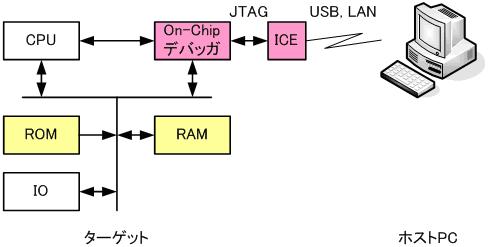

デバッグ機能を全てハードウェアで構成する、市販マイコンで採用されている方式です(図 3参照)。図 3~図 6で紫色はデバッグ機能実現に必要なリソース、黄色はデバッグ対象となるソフトウェアの格納先を示しています。ホストPCとの通信はJTAGベースのシリアル通信路で行います。CPUと並行してバスをモニタし、特定のアドレスやデータが発生するとCPUの実行を中断させる(アドレスブレーク/データブレークと呼ぶ)事ができるので、他の3方式と異なりROM上のプログラムもデバッグすることが可能です。また命令実行毎にCPUレジスタの内容をリアルタイムにダンプするトレース機能もこの方式にしか出来ない特徴です。

しかし機能のサポートに応じて論理規模も増加し、場合によってはCPUよりも大きな論理となる場合があります。

図 3 On-Chipデバッガ方式の構成

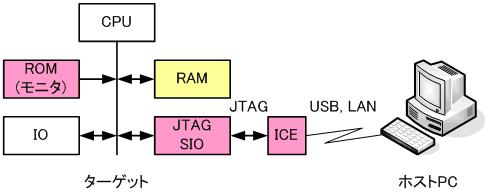

ハードサポート方式

On-Chipデバッガまでの機能は求めないが、必要最低限のデバッグ機能は欲しいという場合に採用される方式です(図 4参照)。On-Chipデバッガ同様JTAGベースのシリアル通信を行うので、基板上の専用リソースは必要としません。それ以外の機能は次に解説するROMモニタ方式と同様になります。

CPUベンダーによっては、数点のアドレスブレーク等On-Chipデバッガ方式の一部をハードサポートしているものもありますが、制約が多いため使い勝手が良いとは言えません。

図 4 ハードサポート方式の構成

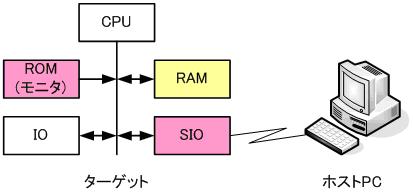

ROMモニタ方式

CPUのソフトウェア例外発生命令を利用したデバッグ方式です(図 5参照)。ターゲットのROM上に書き込まれたモニタプログラムが起動と共に立ち上がり、デバッグ専用のシリアルインターフェイス(SIO)を介してホストPCとの通信を行います。デバッグ対象の実行バイナリはRAM上にロードされ、実行を中断もしくは停止したい箇所の命令をこの例外命令に置き換えることでCPUの実行管理を実現します。またメモリや変数の参照・変更などそれ以外の機能も全てがCPUのソフトウェアで実現されています。しかしデバッグ対象がRAM上にあることが大前提となるので、最終的にROM化するアプリケーションの場合でも、デバッグ時の事を考慮したRAM容量をターゲットのハードウェアに搭載しておく必要があります。

図 5 ROMモニタ方式の構成

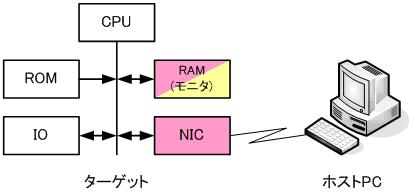

OS依存方式

OSに備わっているデバッグサポート機能を利用する方式です。実行管理はROMモニタ方式と同じです。これまでの3方式とは異なりOSに関係する状態も含めて管理できるので、アプリケーションのデバッグには最適と言えます。しかしこの方式はOSが立ち上がっていることが前提となるので、OS自体のデバッグには前述の3方式のいずれかが必要となります。

図 6 OS依存方式の構成

今回はデバッグ方式を解説する上で解りやすい切り口としましたが、実際はいくつもの方式を組み合わせた製品が出荷されています。例えばOn-Chipデバッガを使いながらOS上のアプリケーションデバッグにも対応したツール等があります。確かにハードウェア+OSがほぼ固定化されている製品であれば、アプリケーション開発効率を上げる手段としては最適です。しかし今回の連載は汎用的な観点で解説しているので解説の対象からはずしています。周辺情報は各自補って下されば幸いです。

Nios IIの対応

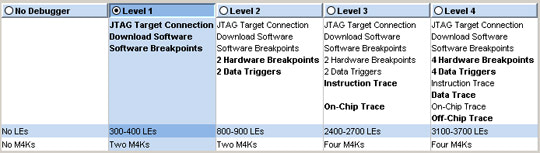

図 7にNios IIのデバッグ機能選択画面を示します。この図はSOPC BuilderでNios IIを組み込むと出てくる画面です。

・No Debugger:ROMモニタ方式、OS依存方式

・Level1、2:ハードサポート方式

・Level3、4:On-Chipデバッガ方式

に相当します。

図 7 Nios II のデバッグ機能選択画面

また下から2段目に追加されるLE数の目安が表示されています。機能に応じて論理規模が大きくなっていることが良く解ります。更にLevel3以上は市販のライセンス購入が必要になるので、デバイスの規模も含めデバッグ機能の導入は予算次第という所でしょうか。

※Level3:First Sililon Solutions(FS2)社のライセンスをお持ちでなくても、16フレーム分であれば、インストラクションのOn-Chip Trace機能をご評価いただけます。

統合開発環境(Integrated Development Environment)

これまで説明してきたツールはそれぞれ独立しており単独で使用可能ですが、特にデバッグが進むと、バグによりソースを一部修正した後にコンパイル→リンクを一括して行う事が多くなるので、繰り返し操作を簡単に行いたくなります。そのためにファイルの依存関係やツールの実行オプション等を記述した定義ファイルを用意し、makeというツールを使って実行管理を行います。しかしこのmakeはコマンドラインのため直感的でなく、定義ファイルの記述も慣れが必要でした。更に前述のデバッグ機能の方式に依存してデバッガの立ち上げ手順が異なるなど、操作性において幾つもの課題がありました。

そこでGUI(Graphical User Interface)ベースでこれらを一括して管理出来るようにしたのが、統合開発環境(IDE)です。以前は各ベンダーが独自開発した物が提供されていましたが、最近はJava向けに開発されたEclipseというオープンソースの開発環境をベースに、C言語のデバッグ機能をアドオンしたものを多く見かける様になってきました。

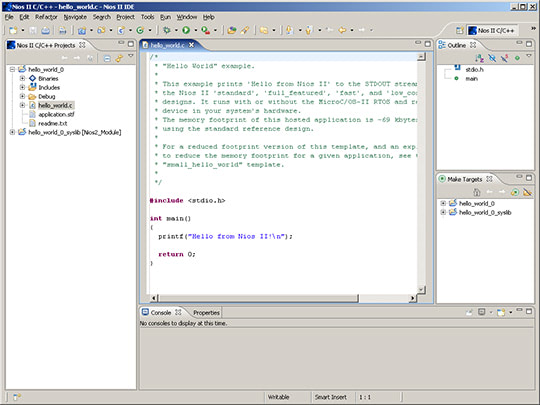

Altera社のIDEもこのEclipseベースとなっています(図 8参照)。

図 8 Nios II IDEの画面例

おわりに

今回はハードウェアの側面から見たデバッグ機能を中心に解説しましたが、様々な手法があることはご理解いただけたと思います。ソフトコアCPUはその論理からツールサポートまで、様々なニーズに対応出来るように考えられていますので、これをうまく活用することがユーザの醍醐味なのです。

「ユーザオリエントなSoC(System On Chip)をミニマムオーダ1個から実現できる」ソフトコアCPU+FPGAを、是非皆さんも体験してみて下さい。

次回以降2回にわたり、完全にハードから離れてソフトウェア中心に話を進め、OS(Operating System)の搭載事例まで解説する予定です。