Introduction

hello. Recently, I've been feeling the growth little by little.

This time, we would like to introduce the new features of our latest device, the Stratix ® 10 FPGA.

Stratix 10 has many exciting new features that can improve the overall performance of your design!

We are planning to introduce it several times from this time, so please check it out.

Encounter with Hyper-xx

=At a meeting one day=

Section Chief "Regarding Stratix 10's HyperFlexTM....Hyper-Retiming due to the addition of Hyper-Register..."

I"(...Hyper?)"

Section chief "Hyper-Pipelining is..."

I ``……………………''

Section Chief "Hyper-Optimization is..."

I"(Hyper- How many things are there...)"

Hyper-xx That's a lot...

And so, the meeting ended without any distinction between them.

I thought this was bad, so I went back to my seat and checked it out.

By the way, the Hyper-xx that I am aware of is

・Hyper Flex

・Hyper-Register

・Hyper-Retiming

・Hyper-pipelining

・Hyper-Optimization

5 types of Let's see what each represents.

What is HyperFlex?

HyperFlex is the whole scheme for improving the performance of FPGAs.

This is a mechanism added from Stratix 10.

And the function that actually increases the performance is the above

・Hyper-Retiming

・Hyper-pipelining

・Hyper-Optimization

Etc.

Why are these new features available starting with Stratix 10?

yes. Thanks to the newly added registers!

That's Hyper-Register!

What are Hyper-Registers?

Hyper-Register is a new register added from Stratix 10.

It is a simple register with 1 input and 1 output, and its basic function is the same as the ALM register.

Many of these Hyper-Registers are placed in the Stratix 10. (That number is more than ten times the number of ALM registers!)

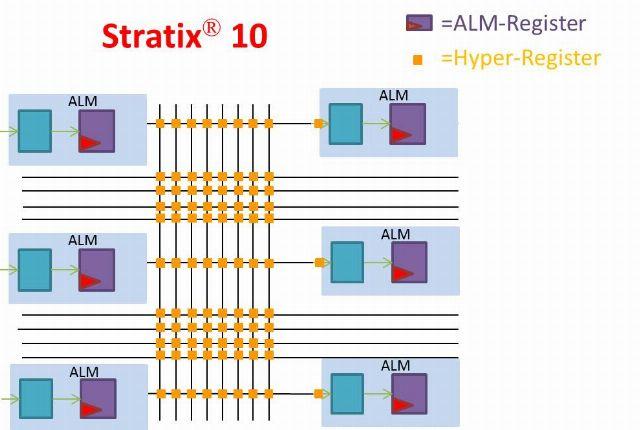

And what you should pay attention to is the placement position of Hyper-Register.

This is the point where the above new features can be achieved.

Placement of Hyper-Register

So where are the Hyper-Registers?

This register is Placed on the wiring that connects ALMs It is done.

to be precise

・Wiring matrix (Row/Column) intersection

・Input all blocks

is placed in

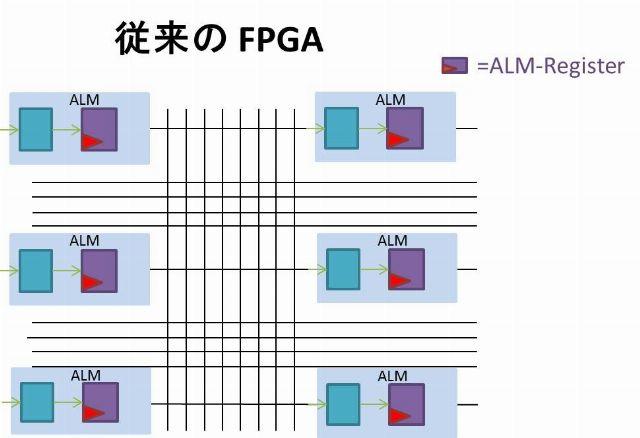

Now let's compare it with the internals of a conventional FPGA.

This is how they are arranged inside.

What is ALM?

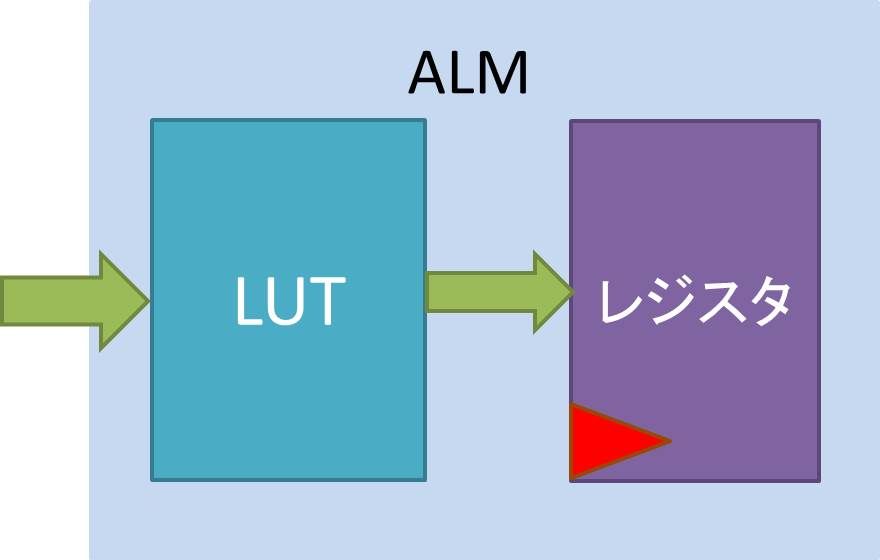

As a side note, let me explain a bit about ALM.

ALM is one of the minimum logic units of FPGA and consists of:

・LUT (lookup table)

・Adder

·register

FPGAs combine ALMs to implement user-written circuits.

Stratix 10 has both registers in ALM and Hyper-Registers.

Summary

Hyper-Registers work flexibly in Stratix 10

・Hyper-Retiming

・Hyper-pipelining

・Hyper-Optimization

such as new function can be achieved and performance can be improved!

・Hyper Flex

The whole mechanism to increase the performance of FPGA introduced from Stratix 10

・Hyper-Retiming, Hyper-Pipelining, Hyper-Optimization, etc.

Features that actually work to improve performance

・Hyper-Register

Registers introduced from Stratix 10 to achieve above functionality

There were many Hyper –xx this time, and there were many times when I was confused while writing the article….

However, I will do my best to make the article easy to understand so that everyone can understand it!

In the next article, we plan to introduce one of the new features, Hyper-Retiming!

So it's clear how Hyper-Register works specifically! ?

Check it out!