In this column, we will introduce "technical information on FPGA that is surprisingly unknown, but makes a difference if you know it."

From FPGA beginners to veterans, the contents can be used widely, so please keep in touch with us until the end.

[Part 4] Reasons why high-precision power simulators were not used

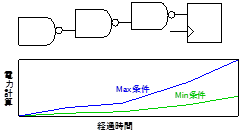

Compared to delay calculations, it is difficult to improve the accuracy of power calculations.

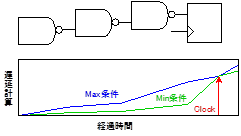

Delay calculation is one of the reasons for recommending synchronous design, as the error between Min and Max delays can be eliminated by synchronizing with the clock (Figure 1).

However, in the calculation of power consumption, even if the clock is input, the difference between the Min power and the Max power will gradually widen (Fig. 2).

So how can we improve the accuracy of power calculations?

Previously, the author incorporated the following functions to develop a high-precision power simulator with an error of several percent compared to HSPICE.

・Calculate penetration power from waveform slope (Slew, Lamp) (Because slope propagates, delay calculation is also necessary)

・Calculate DC power

・Calculate X power (power when logic is in “X” state)

・Prepare a model (algorithm) that can calculate special cells such as memory with high accuracy and high speed

However, contrary to my expectations, this power simulator was not used much. . .

The reason why a high-precision power simulator was not used

Accurate toggle information inside the circuit is necessary to use a highly accurate power simulator.

However, very few people use system-level testbenches to simulate.

Because of this, the high-precision power simulator that we created was put on hold.

After all, after that, we developed a new simple power simulator that estimates the propagation of toggle information from the logic of the circuit (how many times the input transitions and how many times the output transitions) when the toggle information of the input pin is entered. It was become a thing.

How to use the power simulator

Intel provides two power simulators.

Before RTL is complete: EPE (Early Power Estimator) gives you a rough estimate of maximum power consumption.

After RTL is complete: PowerPlay Power Analyzer using actual wire capacitance will give you more accurate power values.

Power simulation has a large error, so there is a margin to increase the value.

Therefore, it is not recommended to select a device based only on "power simulator values".

If you want to know the exact power value, try to “measure with the actual device” as much as possible.

The PowerPlay Power Analyzer is useful when comparing the power consumption between descriptions A and B, which have different RTL descriptions. It is an effective tool to know which description consumes less power.

Details of the created high-precision power simulator

(1) Calculation of penetration power

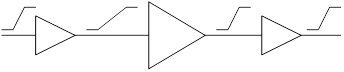

When the CMOS circuit is stopped, either the pMOS or nMOS transistor is closed, so no DC current flows. However, during signal transitions, shoot-through current flows between the slightly open pMOS and nMOS.

It's just like a family restaurant with double doors half-open and a cold breeze coming in from the outside.

In order to calculate this through current, the slope value of the waveform that changes each time it passes through the cell is required.

However, since SDF (Standard Delay Format) does not have information on the slope of the waveform, I calculated it separately.

(2) DC power calculation

As I wrote in the 3rd column, in order to calculate the DC power, it is necessary to know the logic "L" state and "H" state times. The SAIF (Switching Activity Interface format) file has this time information, so we refer to it for calculation.

If you don't calculate the DC power, there will be a large error in the DC power of the pull-up and pull-down buffers, so don't forget to do it.

(3) X power/glitch power calculation

X power is the power consumption when the logic is in the X state.

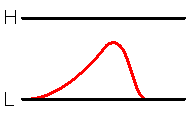

For example, the power consumption when the signal returns to “L” while transitioning from “L” to “H”.

Figure 3. Power is consumed even if the logic is “L” ⇒ “L”.

This power consumption can be calculated from the width of the delay time of the cell and the width of the timing at which the input signal changes.

It's a complicated algorithm because the logic also needs to be checked.

Arithmetic circuits generate many glitches internally until the output stabilizes, so if this calculation is not performed, the error will increase. However, there seem to be few tools that can calculate this power consumption.