第10回は、「FPGAの電源回路設計時のレイアウト方法をご紹介」いたします!

基本的には、どの電源においても評価ボードのガーバーデータを参考としてください。データシートについては、レイアウトの注意点の解説のみ参考にしてください。データシート上のレイアウトは、簡易的に書かれている場合もあるため注意してください。

|

ステップ1:回路図を確認

まず準備として、回路図を確認します。データシートにある回路図とデモボードの回路図を用意して、所望の仕様に合った回路図も探しておきます。 所望の電圧設定の回路図が無い場合は、データシートの計算式を元に周辺定数を決定して電源回路を完成させてください。

ステップ2:FPGAを含めた電源回路設計

次に、お客様がお持ちのアプリケーションに適した回路図へ変更します。電源回路とFPGAを接続する電源ライン全体の回路設計です。FPGAの電源シーケンスも合わせて設計をおこないます。

- 出力電圧の設定、起動時の出力電圧の傾き、Enableの操作方法、デバイス固有の機能設定などを反映させます。

- FPGAの電源設計においては、PDNツールで算出した容量も反映させます。

- 出力電圧の設定をEPEを使って目安を算出し、反映させます。

- Enableなどのシーケンスをも考慮します。

ステップ3:レイアウトの準備と注意点の確認

電源回路の評価ボードのガーバーデータを確認し、電源回路単体でレイアウトを作成します。レイアウトの注意点は、データシートの注意書きをよく確認しておきます。

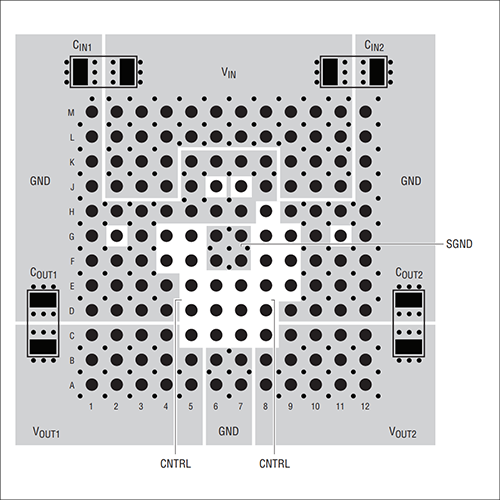

図1は、アナログ・デバイセズ社のμModule LTM4650推奨レイアウトです。横に、データシート内にあるレイアウトの注意点の一部を併記してあります。こちを参考にCADを使って、電源回路のレイアウト設計をおこないます。

**** レイアウトの注意点 *****

• 入力と出力の高周波用セラミック・コンデンサーをVIN、

PGNDおよびVOUTの各ピンに隣接させて配置し、高周波

ノイズを最小に抑えます。

• 2層目には、グランド・レイヤーを配置します。

• ビアの導通損失を最小に抑え、モジュールの熱ストレスを

減らすため、トップ・レイヤーと他の電源レイヤーの間の相互接

続に多数のビアを使います。

• 充填ビアまたはメッキビアでない限り、パッドの上に

直接ビアを置かないでください。

• 信号ピンに接続された部品には、別のSGNDグランド銅領域

を使います。SGNDとGNDをデバイスの下で接続します。

ステップ4: ボード設計

電源デバイスだけでなく、FPGA やその他周辺デバイスも考慮した回路、ボード設計をおこないます。

電源回路と FPGA 間にビーズフィルターを配置する際には、電源のフィードバックループ内にフィルターを配置しないように注意が必要です。また、フィルターによる IR ドロップが発生すると FPGA が要求する電源電圧精度を逸脱する可能性があるので電圧設定の定数見直しなども検討してください。

FPGA の要求電圧精度を満たさないと考えられる場合は、電源のリモートセンス機能や電源電圧の精度を向上させるサーボ機能をもったパワーシステムマネージメントデバイスの検討もおこなってください。

ステップ5: 設計検証

この後、ボード設計の検証をおこないます。

可能な限り、SI/PIのシミュレーションによりFPGA所望の電源回路設計になっているか確認して頂ければと思います。SI/PIのシミュレーションを実施して電源の品質による問題が確認された場合には、ステップ2~ステップ5を繰り返し確認し、設計におけるトラブルを未然に防いでください。

ステップ6: ボードの製作と実機検証

ステップ2~5を繰り返し最適なボード設計と考えられるようになったところで、ボードの製作に進んで頂ければと思います。

最終的に実機検証をおこない、問題がないことを確認して頂ければと思います。